Fターム[4M104AA02]の内容

Fターム[4M104AA02]に分類される特許

81 - 100 / 393

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

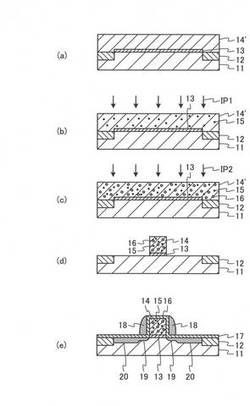

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに表示装置

【課題】 ソース・ドレイン電極と半導体膜との接触抵抗を低減し、移動度特性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 板上に形成されたゲート電極と、前記ゲート電極を覆うようにして前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体膜と、少なくとも各々の一部が前記半導体膜上に形成され、ソース電極及びドレイン電極として機能する一対の電極と、を具備する薄膜トランジスタであって、前記半導体膜は、GeあるいはSi及びGeを含有し、前記一対の電極の各々は、ボロンあるいはV族元素を含有する金属膜で形成され、前記一対の電極の各々と前記半導体膜との間に、ジャーマノシリサイドあるいは金属−Ge間化合物が形成されている。

(もっと読む)

ヘテロ接合障壁領域を含む半導体デバイス及びその製造方法

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極間の間隔が狭い場合においても、ゲート電極間のシリサイドブロック膜の抜け性を向上させる。

【解決手段】ゲート電極14と抵抗素子24とが同一半導体基板1上に混載された半導体装置において、シリサイドブロック膜25を介して抵抗素子24の側面にサイドウォール17を形成する。

(もっと読む)

酸化膜形成方法

【課題】膜中欠損を生じさせることなくGe基板の表面にGe酸化膜を形成する。

【解決手段】Ge基板2の表面にGe酸化膜を形成するプロセスシステム1の酸化炉13において、1000Pa以下の圧力及び300℃以下の基板温度のもとでGe基板2にオゾン供給装置11からオゾンガスを供して当該基板の表面にGe酸化膜を形成する。室温よりも低温の基板温度のもとで前記基板に前記オゾンガスを供給してGe基板2上にオゾン分子層を形成させる。次いで、前記オゾンガスの供給を遮断させた後、Ge基板2を室温まで加熱することにより前記オゾン分子層によって当該基板の表面を酸化させてGe酸化膜を形成させる。Ge基板2が室温まで達した後に前記加熱を遮断して当該基板の温度を室温よりも低温に降下させるとよい。Ge基板2を加熱するための加熱源として赤外光光源を用いるとよい。前記オゾンガスはオゾン濃度が100%であるとよい。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

半導体を含む金属材料の形成方法

【課題】シリコンを含有する半導体領域及びゲルマニウムを含有する半導体領域を含む基板から、ニッケルシリサイド及びニッケルジャーマナイドの共集積化を行うに際し、金属系材料の間で短絡の危険なしに、実装が単純かつ容易な金属系材料の形成方法を提供する。

【解決手段】第1半導体材料から作られた領域と、誘電体材料から作られたパターンによって分離されたゲルマニウムを含む第2半導体材料から作られた領域と、を含む基板を準備し、金属層を堆積し(F2)、第1熱処理(F3)を行うことを含む。金属層は、第1半導体材料と、ゲルマニウムを含む第2半導体材料と、反応して、それぞれ、第1金属系材料と、ゲルマニウムを含有する第2金属系材料と、を形成する。第1熱処理(F3)は、0.01%〜5%の酸素量を含む雰囲気中で行われる。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

ケイ化ニッケルの向上した形成方法

【課題】半導体及び先端実装技術、例えば、ゲート電極、オーミック接触、相互接続ライン、ショットキー障壁ダイオード接触、光起電力、太陽電池及び光電子部品形成などにおける様々な目的のために使用されうるケイ化ニッケルの形成工程数を削減する形成方法を提供する。

【解決手段】ケイ素含有基体をニッケルでコーティングし、このニッケルは保護層でコーティングし、この組み合わせはケイ化ニッケルを形成するのに充分な温度に加熱される。このケイ化ニッケル形成は酸素含有環境において行われうる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

81 - 100 / 393

[ Back to top ]