Fターム[4M104AA02]の内容

Fターム[4M104AA02]に分類される特許

41 - 60 / 393

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

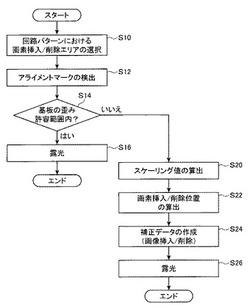

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置およびその作製方法

【課題】バックゲート電極、しきい値電圧を制御するための回路、および不純物添加法を用いずにしきい値電圧が制御されたトランジスタを作製する。該トランジスタを用いて、電気特性が良好で、信頼性が高く、消費電力の小さい半導体装置を作製する。

【解決手段】組成の制御された酸化タングステン膜を有するゲート電極を用いる。酸化タングステン膜の成膜方法によって組成などを調整され、仕事関数を制御することができる。仕事関数の制御された酸化タングステン膜をゲート電極の一部に用いることでトランジスタのしきい値を制御できる。しきい値電圧が制御されたトランジスタを用いることで、電気特性が良好で、信頼性が高く、消費電力の小さい半導体装置を作製することができる。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

透明導電膜の形成方法

【課題】透明導電膜を低コストかつ高効率で作製することができ、基板の大面積化への対応も容易な透明導電膜の形成方法を提供する。

【解決手段】本発明の透明導電膜の形成方法は、酸化インジウム錫化合物からなるITO粒子を含有する導電性インク(Ink)を、その表面に所定のパターンのインク保持部が形成されたフレキソ印刷版11に保持させる工程と、このフレキソ印刷版11に、絶縁透光性基板10を密着させ、上記インク保持部に保持された導電性インクを基板10の所定位置に転写する工程と、この転写後に上記転写された導電性インクを加熱して、絶縁透光性基板10上に、所定パターンの透明導電膜を形成する工程と、を備える。

(もっと読む)

n型ゲルマニウム上への低抵抗コンタクトの作製方法

【課題】n型Ge上に形成されるコンタクトの接触抵抗を低減する。

【解決手段】第1ドーパントレベルのn型ドーパントがドープされたゲルマニウム領域(10)を上部に有する半導体基板を得る工程と、n型ドープされたゲルマニウム領域(10)を覆う界面シリコン層(11)を形成する工程であって、界面シリコン層(11)は第2ドーピングレベルのn型ドーパントでドープされて臨界膜厚より大きな膜厚を有し、これにより界面シリコン層(11)は少なくとも部分的に緩和される工程と、界面シリコン層(11)を覆うように、1×10−2Ωcmより小さい電気抵抗率を有する材料の層(12、13)を形成する工程とを含む方法。本発明はまた、対応する半導体デバイスを提供する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

41 - 60 / 393

[ Back to top ]