Fターム[4M104AA04]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000)

Fターム[4M104AA04]の下位に属するFターム

GaAs (523)

Fターム[4M104AA04]に分類される特許

341 - 360 / 1,477

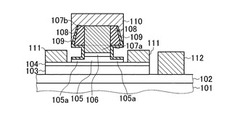

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

半導体素子用エピタキシャル基板の製造方法、半導体素子用エピタキシャル基板、および半導体素子

【課題】簡便な手法によってエピタキシャル基板の障壁層表面の平坦性を向上させ、ショットキーコンタクト特性の優れたエピタキシャル基板を実現する方法を提供する。

【解決手段】半導体素子用のエピタキシャル基板を製造する方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層をエピタキシャル形成するチャネル層形成工程と、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層をエピタキシャル形成する障壁層形成工程と、障壁層形成工程における加熱温度よりも100℃以上250℃以下高い加熱温度で障壁層が形成された下地基板を加熱することにより、障壁層の表面平坦性を向上させる平坦化処理工程と、を備える。

(もっと読む)

凹部バリア層を備えた高電子移動度トランジスタ

【課題】高電子移動度トランジスタ(HEMT)で、凹部バリア層を備え、バリア層間にゲート電極を形成することにより、エンハンスメント型FETを提供する。

【解決手段】基板上104上にバッファ108層を形成し、バッファ層上にスペーサ層112を形成し、スペーサ層上にバリア層116を形成する。バリア層内に凹部を形成し、凹部を通して、少なくてもその一部が前記スペーサ層上に配置されるようにゲート構造140を形成する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が小さいオーミック電極を備えたIII−V族窒化物半導体を用いた半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板11の上に順次形成された、第1のIII−V族窒化物半導体層12及び第1のIII−V族窒化物半導体12と比べてバンドギャップが大きい第2のIII−V族窒化物半導体層13と、p型の導電型を有する第3のIII−V族窒化物半導体層21と、第1のオーミック電極14とを備えている。第1のオーミック電極14は、下部が第2のIII−V族窒化物半導体層13及び第3のIII−V族窒化物半導体層21を貫通し且つ第1のIII−V族窒化物半導体層12における2次元電子ガス層よりも下側の領域に達するように形成されている。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

ショットキダイオードおよびその製造方法

【課題】確実なノーマリオフ動作とリーク電流の少ないショットキダイオードを提供する。

【解決手段】基板31表面にバッファ層32とUID-GaN層33とUID-AlGaN層34とが順次積層され、UID-GaN層とUID-AlGaN層との界面のUID-GaN層側に2DEG層35が発生するエピタキシャル基板と、UID-AlGaN層の表面に形成されたオーミックアノード電極39とオーミックカソード電極40と、オーミックアノード電極とオーミックカソード電極との間のオーミックアノード電極の側面に隣接して形成されたショットキアノードリセス36を少なくとも覆う熱CVDSiNショットキアノード絶縁膜37と、絶縁膜の表面のショットキアノードリセス内に形成されたショットキアノード電極41とを少なくとも備え、オーミックアノード電極とショットキアノード電極とが接続されている。

(もっと読む)

III族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置

【課題】 アクセス抵抗およびオン抵抗が低いIII族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置を提供する。

【解決手段】

障壁層902は、チャネル層901上方にヘテロ接合され、

チャネル層901の上部の一部およびその上方の障壁層902が除去されて凹部が形成され、

チャネル層901および障壁層902の一部にn型導電層領域904が形成され、

n型導電層領域904は、前記凹部の表面を含み、

n型導電層領域904の深さTimpが、n型導電層領域904表面の各部から前記表面と垂直方向の測定値で15nm以上であり、

オーミック電極906および907は、前記凹部の表面を介して前記n型導電層領域にオーミック接触していることを特徴とする、III族窒化物半導体素子。

(もっと読む)

半導体装置

【課題】高電圧を印加した際に逆バイアスにおけるリーク電流が少なく、順方向電圧降下Vfが低い整流素子を有する単一基板上にトランジスタ素子と整流素子を一体にした半導体装置を提供する。

【解決手段】半導体装置10は、単一の基板11上にトランジスタ素子12と整流素子13とを備える半導体装置10であって、トランジスタ素子12は、基板11上に形成された活性層14と、活性層14に接合されたソース電極15とドレイン電極16とゲート電極17を備え、整流素子13は、活性層14に接合されたアノード電極18と、ドレイン電極16を用いたカソード電極と、アノード電極18とカソード電極の間に第1の補助電極19を備えた。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、高い信頼性を有するオーミック電極を備えた化合物半導体装置及びその製造方法を提供することを目的とする。

【解決手段】実施形態によれば、窒化物半導体層と、この窒化物半導体層上に設けられたオーミック電極と、を備え、前記オーミック電極は、前記窒化物半導体層との間で金属窒化物を形成する金属を含む第1電極層と、前記第1電極層上に設けられた、アルミニウム(Al)を含む第2電極層と、前記第2電極層の外面を被覆し、かつタングステン(W)を含む第3電極層と、前記第3電極層の外面を被覆し、かつ金(Au)を含む第4電極層と、を有することを特徴とする化合物半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

薄膜電極、及びその製造方法

【課題】実効キャリアー濃度が増加し、物質間のエネルギーバンドギャップ調節によりショットキー障壁が減少し、高い透過率を有する、優れた電気的、光学的、熱的及び構造的特性を有する新概念のオーミック接触システムを提供する。

【解決手段】発光ダイオード又はレーザーダイオードにおいてオーミック接触を形成するための薄膜電極において、p型窒化ガリウム層上に積層され、Ni−X固溶体を含有する第1電極層と、前記第1電極層上に積層され、Au、Pt、Pd、Ni、Ru、Rh、Re、C、Cu、及びIrからなる群から選択される少なくとも1種以上の元素を含有する第2電極層と、を含むことを特徴とする、薄膜電極である。

(もっと読む)

テラヘルツ波受信素子

【課題】テラヘルツ波を効率よく受信し、信号/雑音比を向上したテラヘルツ波受信素子を提供する。

【解決手段】第1の波長λ1のテラヘルツ波を受信するテラヘルツ波受信素子100であ

って、2以上の半導体層(バッファ層102aおよび電子供給層104a)のヘテロ接合により形成される2次元電子チャネル層103a、ゲート幅方向にλ1/2の長さを有するゲート電極111a、ドレイン電極113aおよびソース電極112aを有する第1のFET100aと、第1のFET100aのゲート電極111aのゲート幅方向における中央部と接続され、かつ、ゲート電極111aと直交するように配置されたゲート配線114aとを備える。

(もっと読む)

半導体発光素子の製造方法

【課題】発光効率と信頼性の向上

【解決手段】第2半導体層108上の全面に、透明導電膜10を形成し、形成された透明導電膜の上に、フォトレジストを塗布し、第1半導体層104の電極形成部16の上部のフォトレジストが除去される際に、除去される部分の輪郭部において、残されたフォトレジストの厚さが除去される部分に向かって次第に薄くなるようにフォトレジストを除去する。残されたフォトレジストをマスクとして、透明導電膜をウエットエッチングして、第2半導体層の一部を露出させる。残されたフォトレジスト及び透明導電膜をマスクとして、ドライエッチングして、第1半導体層の電極形成部を露出させる。残されたフォトレジストをマスクとして、透明導電膜のドライエッチングで露出した部分をウエットエッチングし、残されたフォトレジストを除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

窒化ガリウム系半導体ダイオード

【課題】面内の抵抗率が不均一である窒化ガリウム基板上に形成したダイオード構造の耐圧を向上させることができる窒化ガリウム系半導体ダイオードを提供する。

【解決手段】半導体ダイオード1は、主面がC面である窒化ガリウム自立基板10と、pn接合16a又はショットキー接合16を含む接合領域と、窒化ガリウム自立基板と接合領域との間に設けられ、窒化ガリウム自立基板表面の基板面内での最小抵抗率より低い抵抗率を有し、窒化ガリウム自立基板の導電型と同一の導電型の半導体層14とを備える。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

341 - 360 / 1,477

[ Back to top ]