Fターム[4M104AA04]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000)

Fターム[4M104AA04]の下位に属するFターム

GaAs (523)

Fターム[4M104AA04]に分類される特許

321 - 340 / 1,477

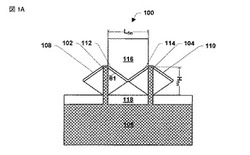

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

半導体装置

【課題】 表面保護膜中へのホットキャリアの侵入に起因する半導体装置の出力低下を抑制すること。

【解決手段】 本半導体装置100は、窒化ガリウム系半導体からなる電子走行層12と、電子走行層12上に設けられ、窒化ガリウム系半導体からなる電子供給層16と、電子供給層16上に設けられ、窒化ガリウムからなるキャップ層18と、キャップ層18上に設けられたゲート電極24と、電子供給層16上にゲート電極24を挟んで設けられたソース電極20及びドレイン電極22と、キャップ層18上に設けられた表面保護膜30と、キャップ層18と表面保護膜30との間に介在し、少なくともゲート電極24とドレイン電極22との間の領域に設けられたAlxGa1−xN(0.5≦x≦1)からなるバリア層50と、を備える。

(もっと読む)

化合物半導体装置

【課題】ゲート電極のリーク電流の増大を抑制して、長期間にわたって安定した高電圧動作を実現する。

【解決手段】GaNからなる化合物半導体層100上に形成されたゲート電極103において、GaNからなる化合物半導体層100上でショットキー接合してなるNi層41と、Au、Cu及びAlからなる群から選択された1種の金属からなる低抵抗金属層42と、Ni層41と低抵抗金属層42との間に形成されたPd層44を設けるようにする。

(もっと読む)

半導体装置

【課題】高周波モジュール中におけるスイッチング素子として用いられるHEMT素子を小型化する。

【解決手段】GaAsからなる基板1の主面上の素子分離部9で規定された活性領域内において、ゲート電極17は、1本で形成し、ソース電極13とドレイン電極14との間では紙面上下方向に延在し、それ以外の部分では左右方向に延在するようにパターニングすることにより、活性領域外に配置されるゲート電極17の割合を減じ、ゲートパッド17Aの面積を減じる。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが小さく且つ良好な高周波特性を有する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された窒化物半導体積層体102と、ソース電極105、ドレイン電極106及びゲート電極107と、窒化物半導体積層体102の上に形成された絶縁膜110と、絶縁膜110の上に接して形成され、端部がゲート電極107とドレイン電極106との間に位置するフィールドプレート115とを備えている。絶縁膜110は、第1の膜111と、第1の膜111よりも絶縁耐圧が低い第2の膜112とを含み、ゲート電極117とドレイン電極116との間に形成された薄膜部110aを有している。フィールドプレート115は、薄膜部110aを覆い且つ開口部においてソース電極と接続されている。

(もっと読む)

化合物半導体装置

【課題】ゲート電極のリーク電流の増大を抑制して、長期間にわたって安定した高電圧動作を実現する。

【解決手段】GaNからなる化合物半導体層100上に形成されたゲート電極102において、GaNからなる化合物半導体層100上でショットキー接合してなるTixW1-xN層(0<x<1)43と、TixW1-xN層43の上方に形成され、Au、Cu及びAlからなる群から選択された1種の金属からなる低抵抗金属層42を設けるようにする。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

化合物半導体素子及びその製造方法

【課題】金合金電極と層間絶縁膜との密着性を向上させる。

【解決手段】化合物半導体素子は、ゲート半導体層10と、カソード半導体層12と、カソード半導体層12上に形成されたAu合金カソード電極14と、ゲート半導体層10上に形成されたAu合金ゲート電極16と、層間絶縁膜18と、カソード電極14及びゲート電極16上のAl配線20と、保護膜22を備える。カソード電極14及びゲート電極16と層間絶縁膜18との界面に、酸化アニール処理により形成され、下地層の構成元素を主成分とする酸化膜15,17を備える。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

導電性薄膜の形成方法及び導電性薄膜形成装置

【課題】スパッタ成膜において、あらゆる膜特性を同時に満足させる手法を提供すること。

【解決手段】スパッタ現象を利用して基板上に導電性薄膜を形成する方法であって、薄膜形成中に、スパッタ電力、スパッタガス、および反応性ガスを含む成膜パラメータの少なくとも1つを2つの値に変動させ、その時間分割比を制御することを特徴とする導電性薄膜の形成方法である。また、p型またはn型の導電型を有する半導体上に導電性薄膜を形成する方法において、半導体上への成膜開始時点に、強度にプラズマ照射を行うことを特徴とする導電性薄膜の形成方法も採用できる。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ特性を有する低オン抵抗で高耐圧の窒化物半導体素子を提供する。

【解決手段】基板上に設けられた第1導電型の窒化物半導体からなる第1半導体層5と、前記第1半導体層の上に設けられ、前記第1半導体層のシートキャリア濃度と同量のシートキャリア濃度を有する第2導電型の窒化物半導体からなる第2半導体層6と、を備える。前記第2半導体層の上には、前記第2半導体層よりも禁制帯幅が広い窒化物半導体からなる第3半導体層7が設けられる。前記第2半導体層に電気的に接続された第1主電極10と、前記第1主電極と離間して設けられ、前記第2半導体層に電気的に接続された第2主電極20と、をさらに備え、前記第1主電極と前記第2主電極との間において、前記第3半導体層および前記第2半導体層を貫通して前記第1半導体層に達する第1のトレンチの内部に絶縁膜33を介して設けられた制御電極30を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を得ることを目的とする。

【解決手段】本発明に係る第1の半導体装置は、窒化物半導体層1と、窒化物半導体層上に設けられた電極とを備え、窒化物半導体層1は電極下に、それ以外の部分よりも高濃度にn型不純物を含む高濃度不純物領域2を備え、電極は、窒化物半導体層1上に設けられた第一金属層3と、第一金属層3上に設けられた第二金属層4と、第二金属層4上に設けられた第三金属層5と、を備え、第一金属層3は第二金属層4よりも窒化物半導体層1との高い密着性を有する金属を含み、第三金属層5は水素よりもイオン化傾向の小さい金属を含む。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

半導体に直接電着する方法

【課題】 半導体の上に直接電着する方法を提供する。

【解決手段】 本開示は、半導体材料の少なくとも1つの表面上に金属又は金属合金を電着する方法を提供する。本発明の方法は、半導体材料の少なくとも1つの表面上の、電着された金属膜による完全な被覆を提供する。本開示の方法は、半導体材料を準備することを含む。半導体材料の少なくとも1つの表面上に、電着プロセスによって金属膜が付けられる。用いる電着プロセスには、最初に低電流密度を加え、所定の時間後に電流密度を高電流密度に変える電流波形が用いられる。

(もっと読む)

半導体装置

【課題】本発明は、面積利用効率を向上しつつ、トランジスタTの特性を維持し、更に整流素子Dの低順方向電圧化を図ることができる半導体装置を提供する。

【解決手段】半導体装置1は整流素子DとトランジスタTとを備える。整流素子Dは、電流経路43と、その一端に配設され整流作用を持つ第1の主電極11と、その他端に配設された第2の主電極12と、その第1の主電極11と第2の主電極12との間に配設され、第1の主電極11に比べて順方向電圧が大きい第1の補助電極15とを有する。トランジスタTは、電流経路43と、その一端において電流経路43と交差する方向に配設された第3の主電極13と、第3の主電極13を取り囲んで配設された制御電極14と、第2の主電極12とを有する。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

321 - 340 / 1,477

[ Back to top ]