Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

2,141 - 2,160 / 3,070

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、n型領域を有するシリコン基板の上に、窒素を含む酸化シリコンを用いたゲート絶縁膜と、ホウ素を含むシリコンを用いたゲート電極とを形成する工程と、ゲート電極両側の前記シリコン基板内にp型ソース/ドレイン領域を形成する工程と、ゲート電極の側壁上に酸化シリコンを用いてサイドウォールスペーサを形成する工程と、ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜を形成する工程と、層間絶縁膜の平坦化された表面から内部に向って凹部を形成し,該凹部内に下地のバリア層とその上の銅領域を含む銅配線とを埋め込む工程と、銅配線の上に炭化シリコン層を形成する工程と、 前記炭化シリコン層の上方に絶縁層をCVDで形成する工程と、を含むことを特徴とする。

(もっと読む)

電界効果型トランジスタ及びその製造方法

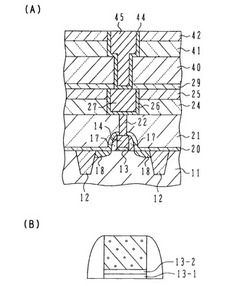

【課題】 電界効果型トランジスタ及びその製造方法に関し、デバイス面積の増大を招くことなく、真性容量に対する寄生容量比を低減して高速動作を可能にする。

【解決手段】 ゲート電極5の上下に半導体的性質を示すカーボンナノチューブ4,9からなるチャネルを設ける。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタは作製される。ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。  (もっと読む)

(もっと読む)

半導体基板上にて集積回路を形成するための方法

【課題】配線に使われる多結晶シリコン層を形成する際に、アモルファスシリコン層が相変化して基板が変形する。この変形を、相変化時の機械的ストレスの発生を回避することにより軽減する方法を提供する。

【解決手段】基板1上のキャパシタ電極、ゲート電極などの導電層2の上に中間層としてアモルファス状の抗ストレス層3を設け、その上にアモルファスシリコン層4を形成する。この後、シリコン層の結晶化温度に加熱し、アモルファスシリコン層を相変化させ多結晶シリコン層にする。抗ストレス層の存在により結晶化時の機械的ストレスの発生が回避される。抗ストレス層は、別の加熱により相変化させ低抵抗化し、導電層と多結晶シリコン層は電気的に接続される。

(もっと読む)

液晶表示装置及びその製造方法

【課題】本発明は、製造工程を単純化してマスク数を低減させることにより、生産性の向上を図る液晶表示装置用アレイ基板及びその製造方法を得ることを目的とする。

【解決手段】

本発明は、従来より少ないマスク工程を利用して液晶表示装置用アレイ基板を製造して工程を単純化して製造効率を向上させるだけでなく製造費用を大幅に節減する。又は、本発明による液晶表示装置用アレイ基板は、別途のアレイ基板保護膜を形成せずに、チャンネル保護膜形成時に酸化膜を形成して保護膜とすることで、不良を防止して画質を向上させるとともに、別途の装備と材料を要しないので材料費が節減される。

(もっと読む)

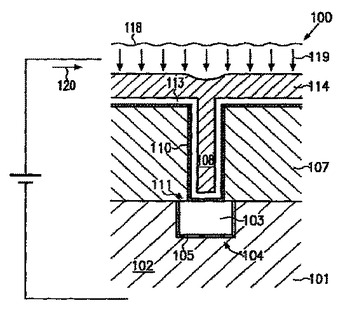

ルテニウム含有膜の蒸着のための装置及び方法

本発明は、1又はそれ以上の基板(101)上にルテニウム金属化合物含有膜を蒸着するための方法を提供する。所望の金属化合物が、適切な溶媒内に最初に溶解される。前駆体混合物が次いで蒸発されて、CVD、MOCVD、ALD、などを備えた処理方法によって基板上の金属化合物の蒸着に使用される処理チャンバ(100)に供給される。この方法は、高品質な実質的に一様な膜の蒸着に結びつく、その上、この方法は金属化合物成分の効率的利用をして、金属化合物の蒸着のためのコストを減少させる。 (もっと読む)

炭化珪素半導体装置、炭化珪素半導体装置の製造方法、炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体及び炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体の製造方法

【課題】シリサイド電極に被着させた上部導体膜の剥離を起こさない炭化珪素半導体装置、炭化珪素半導体装置の製造方法、炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体及び炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体の製造方法を提供すること。

【解決手段】n型SiC基板1に、Niなどのコンタクト母材を被着させ、n型SiC基板1と固相反応させてシリサイド電極を形成し、該シリサイド電極中に生成している炭素の少なくとも一部を該電極外部に排出させ、それを除去して、炭素含有量が、モル数で比較して、珪素含有量よりも少ない炭素低含有シリサイド電極52とし、炭素低含有シリサイド電極52上に上部導体膜3を被着させたことを特徴とする炭化珪素半導体装置を構成する。

(もっと読む)

炭化珪素ディンプル基板

第1主表面と、第1主表面に対向した第2主表面とを有する、高熱伝導性の基板を含むディンプル基板およびその製造方法。活性エピタキシャル層が、基板の第1主表面の上に形成される。ディンプルが、第2主表面から基板中を第1主表面に向かって延びるように形成される。低抵抗材料からなる電気コンタクトが、第2主表面の上とディンプルの中に形成される。低抵抗で低損失のバックコンタクトがこのように、基板を効果的なヒートシンクとして維持しながら形成される。  (もっと読む)

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】3マスク工程を通じて良好なパターンデザインを形成すると共に、段差の除去できる薄膜トランジスタ基板の製造方法を提供する。

【解決手段】本発明の薄膜トランジスタ基板の製造方法は、薄膜トランジスタ140が形成されたゲート絶縁膜125を覆う保護膜150上にコンタクトホール及び画素電極160が形成される領域をオープンさせるための第1フォトレジストパターンを形成する段階、第1フォトレジストパターンが形成された保護膜150上に透明導電膜を全面蒸着させた後、コンタクトホール及び画素電極160が形成される領域以外に形成された透明導電膜を露出させる第2フォトレジストパターンを形成する段階、第2フォトレジストパターンにより露出された透明導電膜をエッチング処理した後、保護膜150上に残留する第1及び第2フォトレジストパターンを除去して、保護膜150上にコンタクトホール及び画素電極160を形成する段階を含む。

(もっと読む)

電子デバイス、電子デバイスの製造方法および電子機器

【課題】特性に優れ、かつ、特性が大気中において経時的に劣化するのを防止し得る電子デバイス、かかる電子デバイスを製造する電子デバイスの製造方法、および、電子機器を提供すること。

【解決手段】薄膜トランジスタ1は、ソース電極20aおよびドレイン電極20bと、ソース電極20aおよびドレイン電極20bの表面に形成された有機膜60と、ソース電極20aおよびドレイン電極20bを覆い、かつ、有機膜60と接触するように設けられた有機半導体層30と、有機半導体層30上に設けられたゲート絶縁層40と、ゲート絶縁層40上に設けられたゲート電極60とを有する。有機膜60は、好ましくは一般式:CF3(CF2)m(CH2)nCH(CH2SH)2(ただし、mは1〜35の整数を示し、nは2〜33の整数を示す。)で表される非共役系有機化合物を、ソース電極20aおよびドレイン電極20bの表面に結合させてなるものである。

(もっと読む)

無電解フェーズと電流供給フェーズとを含むウェット化学堆積によりパターニングされた絶縁体上の金属層

無電解堆積および電気堆積プロセスをインサイチュで実行することによって、非常に信頼性のあるメタライゼーションが供給され、その際に、シード層を形成する、従来の化学気相堆積(CVD)、原子層堆積(ALD)ならびに物理気相堆積(PVD)技術にみられるような、汚染物質ならびにデバイススケーリングに関する欠点を克服することができる。ある実施例では、バリア層はさらに、ウェット堆積プロセスに基づいて堆積される。  (もっと読む)

(もっと読む)

パターンおよび配線パターンならびにそれらの製造法

【課題】低コストで半導体素子または表示素子を製造することができる、パターンの製造法とそれにより形成されるパターンの提供。

【解決手段】基板上に形成された感光性樹脂組成物層の上に疎液性の高い表面被覆層を形成させ、パターンを形成させる。基板上に残留する表面被覆層は疎液性が高く、一方、被覆が除去された部分は相対的に親液性が高いので、被覆が除去された部分に選択的に導電性材料含有組成物を付着させることができ、所望の配線パターンを得ることができる。

(もっと読む)

無電解ニッケルめっき用貴金属表面活性化液

【課題】金等の貴金属上に無電解ニッケルめっき皮膜を形成する場合に、簡単な処理方法によって貴金属部分にのみ良好な無電解ニッケルめっき皮膜を形成することが可能な、貴金属に対する前処理液を提供する。

【解決手段】(i)錯化剤、(ii) 銅塩及び銀塩からなる群から選ばれた少なくとも一種の成分、並びに(iii) アルデヒド類、を含有する水溶液からなる無電解ニッケルめっき用貴金属表面活性化液、並びに該活性化液を用いて貴金属表面を活性化した後、無電解めっき用触媒を付与し、次いで、無電解ニッケルめっきを行うことを特徴とする貴金属上への無電解ニッケルめっき方法。

(もっと読む)

垂直構造の窒化物半導体発光素子及びその製造方法

【課題】電流分散効率を改善した垂直構造の窒化物半導体発光素子及びその製造方法を提供する。

【解決手段】窒化物単結晶成長用基板31上に順次n型窒化物半導体層32、活性層33、p型窒化物半導体層34を形成し、n型窒化物層の表面の少なくとも一面のほぼ中央領域に中央が開放されたマスクMを介して窒化物単結晶が損傷された高抵抗領域34aを形成する。これを含むp型窒化物半導体層上にオーミックコンタクト層と導電性基板を順次形成し、窒化物単結晶成長用基板を分離し、n型窒化物半導体層32の露出面上にn側電極を設けて、オーミックコンタクト層と接するp型窒化物半導体層の表面及びn側電極と接するn型窒化物層の表面の少なくとも一面のほぼ中央領域に窒化物単結晶が損傷されオーミックコンタクト層とショットキ接合を有する高抵抗領域を形成した垂直構造の窒化物半導体発光素子とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜に接するゲート電極の空乏化を抑制しながら、ゲート電極の仕事関数の調整を効率的に行うことが可能な半導体装置およびその製造方法を提供する。

【解決手段】 p型シリコン基板1、埋め込み酸化膜2、及び単結晶シリコン層3から構成されるSOI基板4において、単結晶シリコン層3にソース領域10およびドレイン領域11を備える。また、ソース領域10とドレイン領域11との間の単結晶シリコン層3の表面側はチャネル層3aとして機能する。単結晶シリコン層3(チャネル層3a)の上にはゲート絶縁膜5が形成される。ゲート絶縁膜5上には、窒化チタン(TiN)からなる金属粒子6a,6b、及びポリシリコン膜7から構成されるポリシリコンゲート電極8が設けられる。ここで、TiNからなる金属粒子は、ゲート絶縁膜5に接する部分6aと接しない部分6bからなる。

(もっと読む)

半導体装置

【課題】トレンチゲート型の半導体装置において、ゲート電極内に発生するボイドによるオン抵抗の増加、耐圧や破壊耐量の低下等の問題を生じさせることを効果的に防止する。

【解決手段】トレンチゲート型のMOSトランジスタにおいて、トレンチ15が形成され、このトレンチにゲート絶縁膜16を介してゲート電極が埋め込まれる。ゲート電極は、ゲート絶縁膜16に沿ってトレンチ15内部に凹部を有するように形成される第1のゲート電極17Aと、この凹部側の表面に沿って形成される層間絶縁膜18と、凹部を埋め込むように形成され第1のゲート電極17と同一の材料からなる第2のゲート電極19Aとを有する。

(もっと読む)

熱およびプラズマ増強蒸着のための装置および操作方法

【課題】 熱およびプラズマ増強蒸着のための装置および操作方法を提供することである。

【解決手段】 第1の温度で蒸着システムの第1のアセンブリを維持し、第1の温度より低く低下された温度で蒸着システムの第2のアセンブリを維持し、基板を第2のアセンブリの移送空間から真空アイソレートされる第1のアセンブリの処理空間に配置し、基板上に材料を堆積させる、基板上の蒸着のための方法、コンピュータ読み取り可能なメディア、および、システムである。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】高精細でありトランジスタ特性の良好な、フレキシブルで大面積にも対応でき量

産性のある、薄膜トランジスタおよび薄膜トランジスタの製造方法を提供することを目的

とする。

【解決手段】基材上に、少なくとも下部電極のゲート電極、上部電極のソース電極及びド

レイン電極、絶縁層のゲート絶縁層、半導体からなる活性層の半導体活性層を含む層構成

の薄膜トランジスタであって、少なくとも上部電極が前記基材とは異なる第二の基材上の

、例えば、表面に凹部、又は凸部、又は平部を有する基材の凹部、又は凸部、又は平部に

電極材料が形成された後、前記基材のゲート絶縁層上に転写されて、上部電極のソース電

極及びドレイン電極を形成したことを特徴とする薄膜トランジスタ。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】発光アレイとTFTアレイとの間に金属物質で接触電極を製造することにより発生される接触の不良による断線の問題を解決することができる有機電界発光表示装置及びその製造方法に関する。

【解決手段】本発明に係る有機電界発光表示装置は、第1の基板101上にカラーフィルターアレイと有機発光層が形成された発光アレイ130と、第2の基板102上に発光アレイを制御するための薄膜トランジスタが形成された薄膜トランジスタアレイ140と、発光アレイ130と薄膜トランジスタアレイ140を電気的に接触させる接触電極を含む接触部150とを備え、接触電極150は、電導性高分子物質からなる。

(もっと読む)

相変化インクを用いて、半導体ウェハ上に電気接点を形成するプロセス

基板の表面上に電気接点または導電体を形成するプロセスであって、相変化導電性または半導電性印刷インク、または印刷後の処理の後に導電性または半導電性となるかかる相変化印刷インクをインク・ジェット印刷するステップを備えている、プロセス。 (もっと読む)

2,141 - 2,160 / 3,070

[ Back to top ]