Fターム[4M104BB14]の内容

Fターム[4M104BB14]の下位に属するFターム

Ti/Pt/Au (104)

Fターム[4M104BB14]に分類される特許

141 - 160 / 3,174

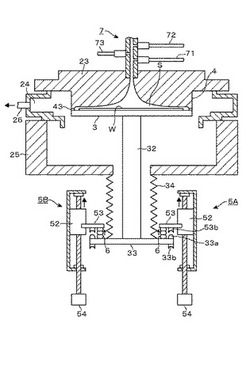

成膜装置及び成膜方法

【課題】処理空間内の圧力を高めることができる成膜装置を提供すること。

【解決手段】処理容器2内に、基板であるウエハWの載置領域を備えた載置台3と、この載置台3と対向する天板部材4とを設け、載置台3を昇降機構5により天板部材4側へ上昇させて、載置台3と天板部材4との間で処理空間Sを形成する。載置台3における載置領域の外側領域と天板部材4との少なくとも一方には突起部43が設けられ、前記処理空間Sの形成時にその先端が他方に接触することにより、前記外側領域と天板部材4との間の離間距離が規制され、前記載置領域を囲むように排気用の1mm未満の隙間40が形成される。隙間40が狭小であることから、処理空間S内に反応ガスを封じ込めることができ、処理空間内の圧力が高められる。

(もっと読む)

半導体装置

【課題】大電力用途の半導体装置に用いるトランジスタには、高いドレイン電流を確保するためのチャネル領域を有する構造が必要である。その一例のトランジスタとして、縦型(トレンチ型)トランジスタも検討されているが、ドレイン電流のオンオフ比がとれず、良好なトランジスタ特性が得られないという課題がある。

【解決手段】導電性を有する基板上において、側面がテーパー形状の断面を有する複数の島状の領域が表面にドット状に設けられた酸化物半導体層を、基板と酸化物半導体層の間に設けられた第1の電極と酸化物半導体層上に設けられた第2の電極とで挟持し、絶縁層を介した酸化物半導体層の島状の領域の側面上に、ゲート電極としての機能を有する導電層を設ける。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

薄膜デバイス

【課題】 酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、基板としての絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上の酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、TFT101の特徴は、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分に、フッ素及び塩素の少なくとも一方を含む表面層15が存在することである。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

薄膜デバイス及びその製造方法

【課題】酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上のインジウムを含む酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分の表面層15におけるXPSスペクトルのインジウム3d軌道起因のピーク位置が、表面層15の下部に存在する酸化物半導体領域におけるXPSスペクトルのインジウム3d軌道起因のピーク位置よりも、高エネルギ側にシフトしている。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

GaN系化合物半導体装置

【課題】ゲート電極へのリーク電流を大幅に低減できるGaN系化合物半導体装置を提供する。

【解決手段】このGaN系HFETによれば、ゲート電極をなすTiN膜の抵抗率(Ω・μm)を24.7(Ω・μm)とした。このように、ゲート電極のショットキー電極層としてのTiN膜の抵抗率が10Ωμm以上であることによって、ゲート電極をなす金属材料TiNの抵抗率(ゲートメタル抵抗率)が10Ωμm未満である場合に比べて、ゲートリーク電流を著しく低減できる。

(もっと読む)

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

半導体デバイス及びその製造方法

【課題】接合障壁ショットキーダイオード及びその製造方法を提供すること。

【解決手段】第1の導電型を有する半導体層と、この半導体層上にあり、半導体層と共にショットキー接合部を形成する金属接点と、半導体層内に半導体領域とを含んでいる。半導体領域と半導体層とが、第1のp−n接合部を、ショットキー接合部と並列に形成する。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、ショットキー接合部に隣接する半導体層内に空乏領域を発生させるように構成され、それによってショットキー接合部を通る逆漏れ電流が制限される。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、第1のp−n接合部のパンチスルーが、ショットキー接合部の降伏電圧よりも低い電圧で起こるように構成される。

(もっと読む)

成膜装置および成膜方法

【課題】銅めっき工程の電極に用いるCu堆積膜による貫通孔開口の閉塞状態を適切に制御できる成膜装置を提供する。

【解決手段】成膜装置100は、貫通孔が形成された基板34Bおよび銅放出源35Bを格納する真空チャンバ30と、真空チャンバ30内を所定の真空度に減圧する真空ポンプ36と、基板34Bに印加する電力を発生する電源80と、基板34Bおよび銅放出源35B間の距離の設定に用いる駆動機構と、を備える。銅放出源35Bから放出された銅材料を基板34Bの一方の主面に堆積させ、主面における貫通孔の開口を銅材料からなる堆積膜によって閉塞させるとき、堆積膜による開口の閉塞状態が、上記距離および上記電力に基づいて調整される。

(もっと読む)

半導体素子およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体素子およびその製造方法等を提供する。

【解決手段】半導体素子は、有機半導体層と、この有機半導体層と接するように配設された電極と、この電極とは別体として形成され、かつ電極と電気的に接続された配線層とを備えている。半導体素子の製造方法は、基板上に、有機半導体層およびこの有機半導体層と接する電極を形成する工程と、この電極と電気的に接続された配線層を形成する工程とを含んでいる。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および閾値電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有するSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。そして、ショットキーバリアダイオード1の閾値電圧Vthを0.3V〜0.7Vにし、定格電圧VRにおけるリーク電流Jrを1×10−9A/cm2〜1×10−4A/cm2にする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

141 - 160 / 3,174

[ Back to top ]