Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

241 - 260 / 333

電気的接続構造、その製造方法および半導体集積回路装置

【課題】 低抵抗の電気的接続構造を提供する。

【解決手段】 導電体に炭素細長構造体が電気的に接続された電気的接続構造において、導電体上に、導電性触媒担持体層と炭素細長構造体を生成するための触媒微粒子層と炭素細長構造体とを順次積層して、電気的接続構造を得る。

(もっと読む)

半導体デバイス構造およびその方法

上に重なる第1の金属酸化物層(16,46)を有する半導体基板(12,42)、第1の金属と窒素または炭素のうちの一方とを有する上に重なる中間層(18,48)、および上に重なる第2の金属酸化物層(20,50)を有するデバイス構造(10,40)、ならびにそのデバイス構造を形成する方法に関する。次いで、中間層(18,48)に酸素が提供される。酸素は導体層から誘電体層(19,53)へと中間層(18,48)を変化させる効果を有する。次いで、例えば、ゲート(24,58)および2つの電流電極(29,30,62,64)を形成することによって、最終デバイスが形成され得る。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性が高く小型なTFTを作製するために、信頼性の高いゲート電極、ソース配線及びドレイン配線を形成するための半導体装置の作製方法及び半導体装置を提供することを課題とする。

【解決手段】絶縁表面を有する基板上に半導体膜を形成し、前記半導体膜上にゲート絶縁膜を形成し、前記ゲート絶縁膜上にゲート電極を形成し、前記ゲート電極に高密度プラズマにより窒化することによって前記ゲート電極の表面に窒化膜を形成する半導体装置の作製方法である。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】本発明は、液晶表示装置に用いられる薄膜トランジスタ基板及びその製造方法に関し、ゲート電極や所定の配線の材料に低抵抗金属を用いても、高い信頼性を確保しうる薄膜トランジスタ基板及びその製造方法を提供することを目的とする。

【解決手段】TFT基板は、窒素含有層としてのAlN膜51と、主配線層としてのAl膜50と、MoN膜54とMo膜53とからなる上層配線層とにより構成された積層構造のゲート電極33を有している。ゲート電極33の側面は全体としてなだらかに傾斜するように形成されているので、ゲート絶縁膜32上に良好な膜質のゲート絶縁膜32を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗・ドレイン抵抗・ゲート抵抗の低減と、寄生容量の削減、優れた静特性と高周波特性の実現を可能とする半導体装置およびその製造方法を提供すること。

【解決手段】ゲート電極6には、半導体結晶1の表面に対して垂直な方向から見たときに、ソース電極(W薄膜2の一方)と重なって見える第一の重なり部分と、ドレイン電極(W薄膜2の他方)と重なって見える第二の重なり部分とが存在し、ソース電極と第一の重なり部分との間と、ドレイン電極と第二の重なり部分との間に空隙11があり、半導体結晶1に形成されたリセス領域の最下段において、ソース側とドレイン側とに空隙7を残して、ゲート電極6が、電界効果型トランジスタ構造の障壁層8と接し、ソース電極、ドレイン電極およびゲート電極6の、半導体結晶1から遠い側の表面はベンゾシクロブテン膜10によって覆われている半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMOSトランジスタにおけるNMOSトランジスタの性能向上と、PMOSトランジスタのNBTI信頼性の維持を同時に実現できる半導体装置およびその製造方法を提供する。

【解決手段】フォトリソグラフィーを用いて、シリコン基板101上にNMOS領域に開口部を有するレジストマスクRM3を形成し、その上から15kVの加速電圧で、ドーズ量1×1015/cm2のN2(窒素)イオンをイオン注入して、NMOS領域のシリコン基板101内に窒素を導入する。その後、活性酸素を用いた酸化手法によりシリコン酸化膜を形成した後に、活性窒素処理を行ってSiON薄膜に転化し、NMOS領域およびPMOS領域に、それぞれSiONのゲート絶縁膜103および104を形成する。

(もっと読む)

自己整合され積極的にスケーリングされたCMOSデバイスにおけるゲート電極の金属/金属窒化物二重層のCMOS構造体及び半導体構造体

【課題】 低仕事関数金属の不適切な熱安定性のために、nFET仕事関数とpFET仕事関数との両方を適正にするために用いることができるゲート・スタックを有するCMOS構造体を提供すること。

【解決手段】 本発明は、半導体基板の1つの領域上に配置された少なくとも1つのnMOSデバイスと、半導体基板の別の領域上に配置された少なくとも1つのpMOSデバイスとを含む、CMOS構造体に向けられる。本発明によれば、少なくとも1つのnMOSデバイスは、ゲート誘電体と、4.2eV未満の仕事関数を有する低仕事関数の元素状金属と、その場金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを含み、少なくとも1つのpMOSデバイスは、ゲート誘電体と、4.9eVより大きい仕事関数を有する高仕事関数の元素状金属と、金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを有する。本発明はまた、こうしたCMOS構造体を製造する方法も提供する。

(もっと読む)

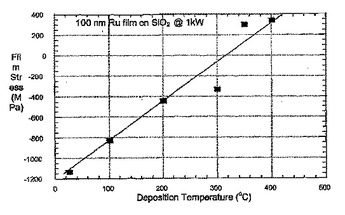

ルテニウム系材料およびルテニウム合金

本明細書には、ルテニウムおよび元素周期表のIV族、V族、もしくはVI族の元素の少なくとも1つの元素またはこれらの組合せが含まれる、蒸着法または原子層堆積法において用いるための合金が記載される。また、本明細書には、ルテニウム系材料またはルテニウム系合金を含む少なくとも1つの層、および元素周期表のIV族、V族、もしくはVI族の元素の少なくとも1つの元素またはそれらの組合せを含む少なくとも1つの層が含まれる積層材料が記載される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムと窒素とを含む膜で形成し、そのハフニウムと窒素とを含む膜中の窒素を適性な組成比にすることで、従来から用いられているPoly−Si電極とほぼ同レベルの良好な移動度を得ることを実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムと窒素とを含む膜からなり、前記ハフニウムと窒素とを含む膜は少なくとも窒素を含みかつハフニウムと窒素とに対する窒素の組成比が51%以下である。

(もっと読む)

スパッター堆積された薄フィルムのための均質固溶体合金

本発明はスパッタリング表面を含むスパッタリング構成部材を含む。そのスパッタリング表面の少なくとも99原子%が元素形態の2つ以上の元素の固溶体に対応する単一相からなる。加えて、そのスパッタリング構成部材の全容積が元素形態の2つ以上の元素の固溶体に対応する単一相からなることができる。本発明は、還元工程、電気分解工程およびヨウ化物工程の1つ以上を使用して混合金属材料を形成する方法を包含する。 (もっと読む)

MOS電界効果半導体装置の製造方法及びMOS電界効果半導体装置

【課題】メタルゲート電極を用いた高性能のCMOS電界効果半導体装置を提供する。

【解決手段】n型ゲート電極及びp型ゲート電極を同一のメタルで構成し、且つ、そのN濃度をn型ゲート電極とp型ゲート電極とで異ならせる。それにより、所定の仕事関数差のn型ゲート電極及びp型ゲート電極を備える高性能のCMOS電界効果半導体装置が実現可能になる。また、そのように同一のメタルで構成されたN濃度の異なる層上に低抵抗層を形成することにより、n型ゲート電極とp型ゲート電極の仕事関数を制御しつつそれらの低抵抗化を図ることが可能になり、より高性能のCMOS電界効果半導体装置が実現可能になる。

(もっと読む)

圧電素子、液滴吐出ヘッド、液滴吐出装置

【課題】良好な電極能を有しつつ低コストで、且つ圧電体に対する充分な吸着性を有する圧電素子、及びそれを備える液滴吐出ヘッドを提供することを目的とする。

【解決手段】共通電極46(下部電極)、圧電体48、及び信号電極50(上部電極)がこの順で積層して構成された圧電素子34において、共通電極46及び/又は信号電極50の構成層の少なくとも1層として、Ta,V,Nb,Mo,W,Ti,Zr,及びHfの金属、前記金属の元素を1種以上含む合金、前記金属の元素を1種以上含む窒化物、前記金属の元素を1種以上含む珪化物、並びに、前記金属の元素を1種以上含む硼化物から選択される少なくとも1種で構成される電気伝導層の少なくとも1層を適用する。これにより、良好な電極能を有しつつ低コストで、且つ剥がれ難い電極を持つ圧電素子34となる。

(もっと読む)

半導体装置の製造方法及びその製造に用いられる成膜装置

【課題】 半導体装置の製造に際し、より効率的な清浄化処理を行う方法を提供することである。

【解決手段】 絶縁性表面の一部に、金属からなる導電領域が露出した基板を、処理チャンバ内に搬入する。処理チャンバ内に、有機酸を、蒸気またはミストの状態で導入し、基板を清浄化する。有機酸の蒸気またはミストの導入を停止し、続いて成膜用の原料ガスを、処理チャンバ内に導入して、基板上に薄膜を形成する。

(もっと読む)

中性ビームを利用した原子層蒸着装置及びこの装置を利用した原子層蒸着方法

【課題】第2の反応ガスをプラズマ化して発生されたラジカルのフラックス、すなわち、イオンビームを中性ビーム化して被処理基板に照射するようにした中性ビームを利用した原子層蒸着装置及びこの装置を利用した原子層蒸着方法を提供する。

【解決手段】本発明による中性ビーム蒸着装置を利用した蒸着方法は、被処理基板に化学的に吸着されない物質を含む第1の反応ガスを被処理基板がローディングされた反応チャンバ内に供給して化学的に吸着されない物質を含む第1の反応物吸着層を被処理基板上に化学的に吸着させて形成する段階と、第1の反応物吸着層が形成された被処理基板上に第2の反応ガスにより生成された中性ビームを照射して化学的に被処理基板上に吸着されない物質を第1の反応物吸着層から除去して第2の反応物吸着層を形成する段階と、を備える。本発明による中性ビームを利用した原子層蒸着装置及びこの装置を利用した原子層蒸着方法を利用することによって、チャージングによる損傷なしに工程を実行することができる。

(もっと読む)

ALDによる貴金属の促進された堆積

【課題】基板上に貴金属を含む薄膜を化学気相成長法を用いて安定的に堆積する方法を提供する。

【解決手段】反応チャンバ中の基板上に貴金属を含む薄膜を堆積するための方法であって、該方法は、以下を含む: 該基板を水素ハライド又は金属ハライドの気体ハライド又は有機金属化合物を用いて処理すること;及び 貴金属反応物及び酸素含有反応物からの該貴金属を含む薄膜を、気相堆積プロセスである原子層堆積プロセスを用いて堆積すること。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 Al等の低抵抗材料を高融点金属と積層した電極における抵抗上昇とオーバーハング形状のない薄膜トランジスタとその製造方法を提供する。

【解決手段】 Al及びCuより選ばれた金属又はこれを主成分とする合金から形成した主配線層2を、Ti、Mo、W、Cr、Al及びCuより選ばれた金属又はこれらの金属の合金に窒素を含有させた材料の下層配線層1と、Ti、Mo、W、Cr、Al及びCuより選ばれた金属又はこれらの金属の合金に窒素を含有させた材料の上層配線層3とで挟んだ積層配線構造を使用し、下層配線層1と上層配線層3とで異なる金属又は合金を用いるか、あるいは、上層及び下層配線層1、3で同一の金属又は合金に窒素を含有させた材料を使用し、それらの窒素含有量が異なるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層によりエクステンション層およびソース・ドレイン層が形成された半導体装置において、合金層と半導体基板間に生じる接合リークを防止して、信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1には、活性領域を区画する素子分離絶縁膜2が形成されており、活性領域における半導体基板1上にゲート絶縁膜4を介してゲート電極5が形成されている。ゲート電極5の両側における半導体基板1上には、エピタキシャル成長層により形成された2つのエクステンション層6と、2つのソース・ドレイン層8が積層されている。ソース・ドレイン層8における素子分離絶縁膜2側の端部には、当該端部における合金層の形成を防止する保護層9が形成されている。保護層9から露出したソース・ドレイン層8には、合金層10が形成されている。

(もっと読む)

マグネトロンスパッタリング装置用高純度Ti材の製造方法

【課題】高信頼性の半導体素子を得るために、Ti窒化物から成る膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のTi窒化物から成るコンタクトバリアー層のAl含有量を原子数で1×1018個/cm3以下に形成するためにTi原料からエレクトロンビ−ム溶解法でAlを3ppm以下に除去することを特徴とするマグネトロンスパッタリング装置用高純度Ti材の製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムとシリコンとを含む膜で形成することで、Poly−Siと同等の仕事関数値を得るともに、下地のゲート絶縁膜とハフニウムとの反応性を低減してゲートリークを抑制し、ゲート絶縁膜の薄膜化を実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムとシリコンとを含む膜からなるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース/ドレイン電極と半導体層とのショットキーバリアが低い電界効果トランジスタを具備する半導体装置を提供すること。

【解決手段】基板10上に半導体性のカーボンナノチューブ12が形成されている。カーボンナノチューブ12側面に形成されたソース及びドレイン13が形成されている。前記ソース及びドレイン13は、カーボンナノチューブ12の側面に接触形成されたメタルカーバイト15と、前記メタルカーバイト上に形成されたメタル電極14とを具備する。ソースとドレインとの間の前記カーボンナノチューブ上に形成されたゲート絶縁膜16、ゲート電極17が積層されている。

(もっと読む)

241 - 260 / 333

[ Back to top ]