Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

181 - 200 / 333

自己整合した耐熱性コンタクトを備える半導体デバイス及びその作製方法

半導体デバイスを形成する方法が、半導体基板上に半導体層を形成することによって提供される。マスクが、半導体層上に形成される。半導体層上に複数のイオン注入領域を形成するために、第1の伝導型を有するイオンがマスクによって半導体層中へ注入される。マスクによってイオン注入領域上に金属層が形成される。複数のイオン注入領域に注入されたイオンをそれぞれ活性化し、かつ複数のイオン注入領域上にオーミックコンタクトを設けるために、複数のイオン注入領域および金属層が単一工程でアニールされる。関連するデバイスも提供される。  (もっと読む)

(もっと読む)

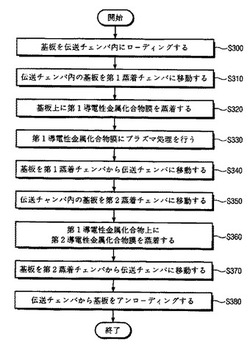

半導体素子の形成方法

【課題】半導体素子の形成方法を提供する。

【解決手段】前記方法は、基板上に有機金属化学蒸着工程によって第1導電性金属化合物膜を形成し、前記第1導電性金属化合物膜上に物理気相蒸着工程によって第2導電性金属化合物膜を形成することを含む。第1及び第2導電性金属化合物膜は、第1導電性金属化合物膜が酸素原子に露出されることを防止するか、最小化した状態で形成される。したがって、第1導電性金属化合物膜の劣化を減少させることができる。

(もっと読む)

ゲート構造物の形成方法及びそれを用いた半導体装置の製造方法

【課題】改善された電気的特性を有するゲート構造物の形成方法及びそれを用いた半導体装置の製造方法を提供する。

【解決手段】基板上にゲート絶縁膜パターン、第1導電層パターン、及びダミーゲート層パターンを含む第1予備ゲート構造物を形成する。第1予備ゲート構造物に隣接する基板に不純物領域を形成した後、基板上に第1ゲート構造物を覆う絶縁層を形成する。ダミーゲート層パターンを除去してゲート絶縁膜パターン及び第1導電層パターンを含む第2予備ゲート構造物を形成した後、第1導電層パターン上に第2導電層パターンを形成する。ゲート電極を導電層パターンに変化されるか導電層パターンを形成するための犠牲層の役割を遂行するダミーゲート層パターンを適用することで、不純物領域の形成工程を含む半導体装置の製造のための高温工程下でもゲート電極が劣化されることを防止することができる。

(もっと読む)

半導体製造方法およびエッチングシステム

【課題】疎パターン領域と密パターン領域を有する半導体の製造方法において、再現性良く疎パターンと密パターン寸法の独立制御を可能とし、各パターンの露光完の寸法及びゲート電極寸法の長期変動を抑制する。

【解決手段】マスクパターンが疎に形成された領域と密に形成された領域とを有する半導体基板上に積層膜を成膜する成膜工程とマスクパターンを形成するリソグラフィ工程S1と装置内の堆積物を除去するクリーニング工程S11Cとマスクパターンを細線化するトリミング工程S3とマスクパターンを積層膜に転写するドライエッチング工程S4、S5から成る半導体製造方法において、トリミング工程S3の前もしくは後に、シーズニング工程S11Sに続いて堆積ステップ工程S2を導入する。

(もっと読む)

半導体装置

【課題】一部のゲート絶縁膜に高誘電率膜を用いている半導体装置において、より簡略して形成することが半導体装置を提供する。

【解決手段】第一の領域と第二の領域とを有する半導体装置において、第一の領域(コア部100)には、第一のゲート電極4、第二のゲート電極5および高誘電率ゲート絶縁膜3が形成されている。第一のゲート電極4と第二のゲート電極5とは、組成比が相違する。高誘電率ゲート絶縁膜3の上には、第一のゲート電極4と第二のゲート電極5が形成されている。また、第二の領域(I/O部200)には、第三のゲート電極7、第四のゲート電極8およびSiON膜6またはSiO2膜が形成されている。第三のゲート電極7と第四のゲート電極8とは、注入されている不純物元素の種類および/または濃度が異なる。また、SiON膜6またはSiO2膜上には、第三のゲート電極7と第四のゲート電極8が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート絶縁膜の膜厚が増加することを抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に絶縁膜20を形成するステップと、絶縁膜上に第1の金属膜30を形成するステップと、第1の金属膜の上方に、酸素分子1モルあたりの金属酸化物を生成する際の生成エネルギーが負であって、かつ生成エネルギーの絶対値が第1の金属膜より大きい第2の金属膜50を形成するステップと、第1及び第2の金属膜にパターニングを行うステップと、所定の熱処理を行うステップとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有しかつ低抵抗なメタルゲート電極を備えたCMOSトランジスタを形成する。

【解決手段】nMOSFET10のメタルゲート電極12を、HfN層12aおよび金属層12b,12cの3層構造とし、pMOSFET20のメタルゲート電極22を、HfN層22a、Nドープ金属層22bおよび金属層22cの3層構造とする。各メタルゲート電極12,22の最下層のHfN層12a,22aのN濃度、および中層の金属層12bとNドープ金属層22bのN濃度の関係を調整して、仕事関数を適切に制御すると共に、各メタルゲート電極12,22の最上層に低抵抗の金属層12c,22cを設け、その低抵抗化を図る。これにより、仕事関数制御のために最下層および中層にNが導入されている場合でも、最上層の低抵抗層によって低抵抗コンタクトが確保されるようになる。

(もっと読む)

半導体接合部に薄膜物質を選択的に堆積させる方法

本発明の実施形態は、基板上に形成されたデバイスに高品質コンタクトレベル接続部を形成するプロセスを提供する。一実施形態において、基板上に物質を堆積させるための方法であって、基板を酸化物エッチング緩衝液にさらして、前処理プロセスで水素化シリコン層を形成するステップと、基板上に金属シリサイド層を堆積させるステップと、金属シリサイド層上に第一金属層(例えば、タングステン)を堆積させるステップと、を含む前記方法が提供される。酸化物エッチング緩衝液は、フッ化水素とアルカノールアミン化合物、例えば、エタノールアミン、ジエタノールアミン、又はトリエタノールを含有することができる。金属シリサイド層は、コバルド、ニッケル、又はタングステンを含有することができ、無電解堆積プロセスによって堆積させることができる。一例において、基板は、溶媒と金属錯体化合物を含有する無電解堆積溶液にさらされる。 (もっと読む)

半導体装置及びその製造方法

【課題】好適な特性を有するゲート絶縁膜及びゲート電極からなるP型FET及びN型FETを備える半導体装置を提供する。

【解決手段】P型FET形成予定領域とN型FET形成予定領域とにわたって、基板上にゲート絶縁膜を形成し、ゲート絶縁膜上にP型FET用のゲート電極層を形成し、P型FET形成予定領域とN型FET形成予定領域とにおいて、P型FET用のゲート電極層を加工することにより、P型FET形成予定領域にP型FET用のゲート電極を形成すると共に、N型FET形成予定領域にダミーゲート電極を形成し、N型FET形成予定領域において、ゲート絶縁膜上からダミーゲート電極を除去することにより、溝を形成し、溝にゲート電極材料を埋め込むことにより、ゲート絶縁膜上にN型FET用のゲート電極を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】銅拡散防止能力に優れ、且つ、銅配線との密着性が良好なバリアメタル膜を形成することができる半導体装置の製造方法を提供すること。

【解決手段】第4の層間絶縁膜16の上面とビアホール16aの内面に、希ガスと窒素ガスとの混合ガスを使用する反応性スパッタ法により、チタン族元素の窒化物よりなるバリアメタル膜18を形成する工程を有し、バリアメタル膜18を形成する工程が第1スパッタ工程と第2スパッタ工程とを含み、該第2スパッタ工程において、上記混合ガス中における窒素ガスの流量比を第1スパッタ工程におけるよりも低くする共に、第1スパッタ工程で形成されたビアホール16a底部のバリアメタル膜18を薄膜化する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜に高誘電率膜を使用し、ゲート電極に金属を含む導体膜を使用するpチャネル型MISFETにおいて、生産性向上を図ることができる技術を提供することにある。そして、金属を含む導体膜の仕事関数値が酸化シリコン膜に接するとした場合にシリコンの価電子帯近傍の値から離れたものであっても、pチャネル型MISFETのしきい値電圧を下げることができる技術を提供する。

【解決手段】半導体基板1上に形成されたpチャネル型MISFETQ1は、酸化ハフニウム膜よりなるゲート絶縁膜10を有し、このゲート絶縁膜10上に、酸化アルミニウム膜よりなる金属酸化物膜11を有する。そして、金属酸化物膜11上に窒化タンタル膜よりなるゲート電極12を有している。ここで、金属酸化物膜11は、ゲート電極12の仕事関数値をシフトする機能を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の界面準位を低い状態に維持しつつ、低抵抗で適性な仕事関数値を有するゲート電極の形成を可能とする。

【解決手段】半導体基板11上にゲート絶縁膜13を介してゲート電極14を備えた絶縁ゲート型トランジスタからなる半導体装置1であって、前記ゲート電極14は、前記ゲート絶縁膜13側に上層のゲート電極14を成膜する際のダメージを抑止する導電性を有する緩衝膜15と、前記緩衝膜15上に形成されたゲート電極本体部16とで構成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上での抵抗が十分に高く、且つ銅配線上での抵抗が十分に低いキャップ層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板1上に第3の層間絶縁膜10を形成する工程と、第3の層間絶縁膜10に第1の配線溝10aを形成する工程と、第1の配線溝10aに銅を埋め込んで第1、第2の銅配線12a、12bにする工程と、第3の層間絶縁膜10と第1、第2の銅配線12a、12bの上に、希ガスと窒素ガスとの混合ガスを用いる反応性スパッタ法により、キャップ層13として窒化ジルコニウム層を形成する工程とを有し、第3の層間絶縁膜10上に形成されるキャップ層13は、比抵抗が1×109μΩ・cm以上となるように形成される半導体装置の製造方法による。

(もっと読む)

高アスペクト比用途の異方性フィーチャを形成するためのエッチング方法

【課題】本発明は、エッチング工程における、高アスペクト比用途の異方性フィーチャの形成方法を提供する。

【解決手段】開示された方法は、側壁パッシベーション管理技法を通して、高アスペクト比のフィーチャのプロファイルと寸法の制御を有利に促進する。一実施形態において、側壁パッシベーションは酸化パッシベーション層をエッチング層の側壁及び/又は底部に選択的に形成することによって管理される。他の実施形態において、側壁のパッシベーションは余分な再堆積層を定期的に除去して平坦で均一なパッシベーション層をその上に維持することによって管理される。平坦で均一なパッシベーション層により、欠陥及び/又は下層のオーバーエッチングを起こすことなく、高アスペクト比のフィーチャを、基板上の高及び低フィーチャ密度領域の双方に所望の深さ及び垂直プロファイルの限界寸法に適した形で徐々にエッチングすることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 優れた金属シリケート膜を形成することができ、特性や信頼性に優れた半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11上にゲート絶縁膜13を形成する工程と、ゲート絶縁膜上にゲート電極14を形成する工程と、を備えた半導体装置の製造方法であって、ゲート絶縁膜を形成する工程は、金属シリケート膜を形成する工程を含み、金属シリケート膜の形成に用いるシリコン原料は、モノシラン中の少なくとも1つの水素原子をアルキル基で置換した第1の炭化水素シリコン化合物、ジシラン中の少なくとも1つの水素原子をアルキル基で置換した第2の炭化水素シリコン化合物、及びトリシラン中の少なくとも1つの水素原子をアルキル基で置換した第3の炭化水素シリコン化合物の少なくとも1つを含む。

(もっと読む)

半導体デバイスの製造において直接銅めっきし、かつ充填して相互配線を形成するための方法及び組成物

【課題】半導体デバイスの製造において直接銅めっきし、かつ充填して相互配線を形成するための方法及び組成物の提供。

【解決手段】本発明は、半導体デバイスの製造において直接銅めっきし、かつ充填して相互配線を形成するための方法及び組成物を目的としている。本発明によれば、上記方法とは、銅イオン源を45〜200mM、好ましくは45〜100mMの濃度で、及び2〜4つのアミン官能基を有する脂肪族ポリアミンである少なくとも1種の銅錯化剤を30〜200mM、好ましくは60〜200mMの濃度で溶媒中の溶液に含有し;かつ上記銅/錯化剤のモル比が0.2〜2、好ましくは0.3〜1.5である銅電解槽を調製し、基板の銅拡散バリア層を上記銅電解槽に接触させ、上記基板に、銅が電気めっきされる厚みに従い調整された時間中、電気的バイアスを印加し、上記基板を上記銅電解槽から取り出す方法である。

(もっと読む)

複数の金属層を積層した半導体素子

【課題】CET特性及び絶縁特性を向上させた半導体素子を提供する。

【解決手段】基板110と、基板110上に積層され、高誘電体物質から形成されるゲート酸化膜120と、ゲート酸化膜120上に積層され、ゲート酸化膜120と同種金属の窒化物から形成される第1金属層131と、第1金属層131上に積層される第2金属層132と、第2金属層132上に積層される第3金属層133と、第3金属層133上に積層され、第1金属層131〜第3金属層133と共にゲート電極を形成する物質層140と、を含んでいる。これにより、半導体素子のゲート酸化膜と金属層間の化学的な反応により発生するCET特性の低下および電流の漏れなどを防止することで半導体素子の絶縁特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタは作製される。ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。  (もっと読む)

(もっと読む)

金属ゲート電極及びポリゲート電極を有する高性能回路

【課題】 高kの金属誘電体スタックからなるゲート電極構造により、CMOSのゲートポリシリコンの空乏化を阻止する。

【解決手段】 本発明によると、nFETデバイス又はpFETデバイスの少なくとも一方が、薄膜化されたSi含有電極すなわちポリシリコン電極と、該Si含有電極上の第1の金属とを有するゲート電極スタックを含み、他方のデバイスが、薄膜化されたSi含有電極を有さず、少なくとも第1の金属ゲートを有するゲート電極スタックを含む、半導体構造が提供される。

(もっと読む)

181 - 200 / 333

[ Back to top ]