Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

301 - 320 / 333

半導体装置とその製造方法

【課題】シリコン窒化膜を堆積してもシート抵抗が上昇しない配線構造を提供する。

【解決手段】半導体基板上に第一の高融点金属膜5を形成する工程と、前記第一の高融点金属膜上に高融点金属窒化物の反応物7を持つ第二の高融点金属膜6Aを形成する工程と、前記第二の高融点金属膜上にシリコン窒化膜8を形成する工程とからなる。これにより、シリコン窒化膜の膜質を変化させることなく、また成膜時のパーティクルの発生を従来方法と同等としたまま、シリコン窒化膜下の高融点金属のシート抵抗の上昇を最小限に抑えることができる。

(もっと読む)

銅配線の形成方法

【課題】CVD法により、埋め込み性、下地層との密着性に優れた銅配線形成方法の提供。

【解決手段】ホールや溝が形成された基板表面上に、金属原料としてテトラキスジエチルアミノバナジウム、テトラキスジメチルアミノバナジウム、テトラキスエチルメチルアミノバナジウム、テトラキスジエチルアミノチタン、テトラキスジメチルアミノチタン、テトラキスエチルメチルアミノチタンを、還元性ガスとしてターシャリーブチルヒドラジン、NH3、H2、SiH4、Si2H6を用いて、CVD法によりバナジウムまたはチタン含有膜からなる下地層を形成し、この上に、CVD法により銅含有膜を形成し、ホールや溝を埋め込み、配線を形成する。

(もっと読む)

表面活性化剤を用いた銅の原子層蒸着

本発明は、原子層蒸着法において、基材上または多孔性固体の中あるいは上に銅膜を形成するための新規な原子層蒸着法に関する。 (もっと読む)

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 従来技術による金属ゲート電極形成ではシリコン基板が大口径化した場合、ウェハ面内、及び疎密間での寸法及び形状のばらつきが大きくなるという課題があった。

【解決手段】 本発明は、タングステンゲートエッチングにおいて、寸法のウェハ面内均一性に優れた電極形成可能とした半導体装置の製法であって、具体的には、シリコン基板101にゲート絶縁膜としてシリコン酸化膜102、高誘電体膜(High−k膜)103、ゲート電極材料としてタングステン膜104、マスク膜としてシリコン窒化膜105を順に成膜する。反射防止膜106を塗布し公知のリソグラフィ技術によりパターンを形成し、この基板を反射防止膜106、シリコン窒化膜105を一般的な条件でエッチングした後、タングステン膜をシリコン基板の中央と外周のプラズマ密度の比を3〜4:1の条件で残膜が3〜5nmになるまでエッチングを行い、最後に残りのタングステン膜をプラズマ密度の比が中央:外周=1:1の条件でエッチングを行うこと方法である。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、ゲート電極を形成する際の製造プロセスを簡略化することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、一対のn型のソース/ドレイン領域6aと、チャネル領域5a上にゲート絶縁膜7aを介して形成されたゲート電極8aと、一対のp型のソース/ドレイン領域6bと、チャネル領域5b上にゲート絶縁膜7bを介して形成されたゲート電極8bとを備えている。そして、ゲート電極8aは、ゲート絶縁膜7a上に形成されたTaN層9aと、TaN層9a上に形成されたポリシリコン層10aとを含み、ゲート電極8bは、ゲート絶縁膜7b上に形成されたTaN層9bと、TaN層9b上に形成されたポリシリコン層10bとを含み、TaN層9aおよび9bは、同じ層からなる。

(もっと読む)

CMOSデバイスのソースおよびドレインの寄生抵抗低減

ドープされた半導体基板を与えることと、pn接合部を画定するべく基板に第二ドーパントを導入することと、pn接合部に対応する容量を低減するべくpn接合部付近の基板中に中性化種を導入することとを含む、半導体系デバイスを製造するための方法である。半導体系デバイスは、第一および第二ドーパントを有する半導体基板と、中性化種とを含む。第一および第二ドーパントはpn接合部を画定し、中性化種は、pn接合部に対応する容量を低減するべくpn接合部付近の第一ドーパントの一部を中性化する。 (もっと読む)

反射防止コーティング及び積層配線ライン

【解決手段】 チタニウム−アルミニウム−窒素(「Ti−Al−N」)が半導体基板上に積層されて反射防止コーティングとしての役割を果たす。配線ラインの実施の形態に対して、アルミニウム導電層(54)及びアルミニウム−チタニウム下層(52)は、反射防止キャップ層の下に形成される。

【効果】 配線ライン製造プロセスに対して、Ti−Al−N層は、製造中の不要なフォトリソグラフ光(即ち、光子)の反射を防止するキャップ層(56)としての役割を有する。電界放射ディスプレイ装置(FED)(150)に対して、Ti−Al−N層は、ディスプレイスクリーン(118)のアノードに由来する光がトランジスタ接合部を通過して装置動作を妨害するのを防止する。Ti−Al下層は熱処理中にアルミニウム導電層に起きる収縮を低減する。

(もっと読む)

半導体素子の製造方法およびマグネトロンスパッタリング装置用Ti材の製造方法

【課題】高信頼性の半導体素子を得るために高融点金属、高融点金属からなる合金、高融点金属の珪化物、Ti,Ta,W,Ti−W合金の窒化物からなる膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】Ti原料からAlを除去してAl濃度が3ppm以下であるマグネトロンスパッタリング装置用Ti材を調製し、このTi材を用いてAl含有量が原子数で1×1018個/cm3以下であり結晶質または非晶質であるコンタクトバリアー又はゲート電極層をスパッタリング法により形成することを特徴とするソース−ドレイン領域の接合深さが0.3μm以下である半導体素子の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜に取り込まれる不純物を低減させて、凹部内の配線における欠陥を減少させることが可能な半導体装置の製造方法を提供する。

【解決手段】まず、表面にビアホール1a及び配線溝1bを有するウェハWをめっき液に浸漬させ、かつウェハWとアノード11との間に電圧を印加して、ウェハW上にめっき膜4を形成する。めっき膜4を形成した後に、電圧を印加した状態でウェハWをめっき液から取り出す。そして、シード膜3及びめっき膜4に熱処理を施し、結晶を成長させて、配線膜5を形成する。最後に、ビアホール1a及び配線溝1bに埋め込まれた部分以外の配線膜5等を除去し、配線5aを形成する。

(もっと読む)

原子層蒸着による銅フィルムの蒸着のための銅(II)錯体

本発明は、新規な1,3−ジイミンおよび1,3−ジイミン銅錯体ならびに原子層蒸着法における基材上または多孔性固体中もしくは多孔性固体上での銅の蒸着のための1,3−ジイミン銅錯体の使用に関する。 (もっと読む)

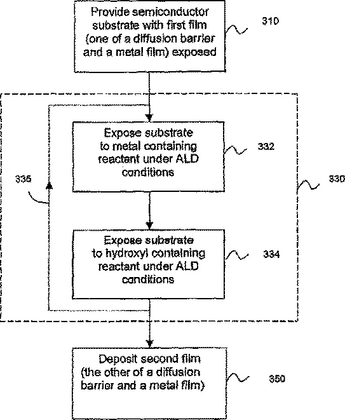

酸素架橋構造及び方法

拡散バリア膜と金属膜との間の接着性を改善するための方法が提唱される。拡散バリア膜及び金属膜の両方は、いずれかのシークエンスで、半導体基板上へ堆積される。拡散バリア膜又は金属膜のいずれか一方である第一膜(第一膜は、基板の表面領域の少なくとも一部で暴露される)を有する基板は、酸素含有リアクタントに暴露され、第一膜の露出部分に酸素含有基又は酸素原子の約1の単層の表面終端を生成する。次いで、第二膜(これは、拡散バリア膜及び金属膜のうち他方である)が基板上に堆積される。さらに、酸素架橋構造が提唱され、該構造は、拡散バリア膜及び該拡散バリア膜との界面を有する金属膜を含む(ここで、界面は、酸素原子の単層を含有する)。

【課題】

【解決手段】  (もっと読む)

(もっと読む)

原子層蒸着による銅フィルムの蒸着のための銅(II)錯体

本発明は、新規な1,3−ジイミン銅錯体および原子層蒸着法における基材上または多孔性固体中もしくは多孔性固体上での銅の蒸着のための1,3−ジイミン銅錯体の使用に関する。 (もっと読む)

薄膜形成方法

【課題】プラズマ前処理を行うこともなく、低温で、比抵抗が低く、酸化物膜やCu配線膜に対する密着性が優れ、またCu配線の信頼性を損なうことのないバリアメタル膜であるW系金属薄膜を形成する方法の提供。

【解決手段】真空チャンバー102内に原料ガス(WF6、W(CO)6ガス等)を導入する工程と、化学構造中に水素原子を含んだ反応性ガス(H2、NH3、SiH4、NH2NH2ガス等)を触媒体108に接触させて活性種にしてから真空チャンバー102内に導入する工程とからなるCAT−ALD法により成膜する。

(もっと読む)

窒化物系化合物半導体装置及びその製造方法

【課題】 極めて簡単な手段を採ることで、窒化物系化合物半導体と電極との接触抵抗を低下させ、また、電極表面及び電極パターンエッジのモフォロジを良好に維持することを可能にして高い信頼性を実現できるようにする。

【解決手段】 金属窒化物、例えばTiNを含む第1の層及びMox Ga1-x (0<x<1)を含む第2の層が半導体に近い側から前記の順に積層されてなる電極を備えてなることが基本になっている。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 メタルゲート及びhigh-kゲート絶縁膜を有するCMOSにおいて、nMOS及びpMOSトランジスタの低しきい値化を実現する。

【解決手段】 n型MISFET形成領域11のゲート絶縁膜3aはHfO2膜であり、メタルゲート電極4aは、TiN膜と、ゲート絶縁膜との界面に生成されたにゲート電極に含まれるIV族遷移金属と酸素を含むがシリコンは含まない界面層とからなり、その仕事関数はn型MISFETのゲート電極材料に適した4.0〜4.2eVである。p型MISFET形成領域12のゲート絶縁膜3bはHfSiO2/HfO2であり、メタルゲート電極4bはTiNと、ゲート絶縁膜との界面に形成されたにゲート電極に含まれるIV族遷移金属と酸素および金属的シリコン(Si0)からなる界面層とからなり、その仕事関数は、p型MISFETのゲート電極材料に適した4.9eVとなっている。

(もっと読む)

半導体装置の製造方法

【目的】 不純物の残留を抑制し、バリアメタルを高純度に成膜することを目的とする。

【構成】 基体上にTa[N((CH3)2]5を供給するTa[N((CH3)2]5供給工程(S102)と、前記Ta[N((CH3)2]5におけるTaとは異なるCを除去するH2供給工程(S106)と、前記Cが除去された前記Ta[N((CH3)2]5の吸着分子に基づいて前記TaN膜を生成するNH3供給工程(S108)と、を備え、前記Ta[N((CH3)2]5工程とH2供給工程とNH3供給工程とを繰り返すことで、前記基体上にTaN膜を堆積させることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度に優れると共に、低抵抗であって且つ絶縁膜に対する密着性の高いバリアメタル膜を有する半導体装置を提供する。

【解決手段】 基板(1)上に形成された絶縁膜(6)と、絶縁膜(6)中に形成された埋め込み金属配線(10)と、絶縁膜(6)と金属配線(10)との間に形成されたバリアメタル膜(A1)とを備えた半導体装置において、バリアメタル膜(A1)は、絶縁膜(6)が存在している側から金属配線(10)が存在している側へ向かって順に積層されている金属酸化物膜(7)、金属化合物膜(8)及び金属膜(9)よりなる。金属化合物膜(8)の弾性率は、金属酸化物膜(7)の弾性率よりも大きい。

(もっと読む)

301 - 320 / 333

[ Back to top ]