Fターム[4M104BB30]の内容

Fターム[4M104BB30]に分類される特許

161 - 180 / 1,457

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

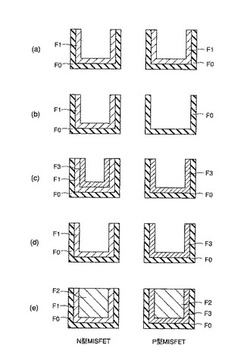

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

スパッタリングターゲット、スパッタリングターゲットの作製方法および半導体装置の作製方法

【課題】酸窒化物膜を作製する成膜技術を提供する。また、その酸窒化物膜を用いて信頼性の高い半導体素子を作製する。

【解決手段】窒化インジウム、窒化ガリウム、窒化亜鉛の少なくとも1つを原料の一とし、これと、酸化インジウム、酸化ガリウム、酸化亜鉛の少なくとも1つと混合して窒素雰囲気中で焼結したインジウムとガリウムと亜鉛を有する酸窒化物よりなるスパッタリングターゲットを用いて酸窒化物膜を作製することにより、必要な濃度の窒素を含んだ酸窒化物膜が得られる。得られた酸窒化物膜はトランジスタのゲートやソース電極、ドレイン電極等に用いることができる。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

拡散バリアー層及びその製造方法

【課題】表面を有する基材アセンブリを提供し、この表面の少なくとも一部の上にバリアー層を提供することを含む、集積回路の製造で使用する方法を提供する。

【解決手段】バリアー層14は、白金(x):ルテニウム(1−x)合金でできており、ここでxは約0.60〜約0.995、好ましくはxは約0.90〜0.98である。バリアー層14は、化学気相堆積によって作ることができ、バリアー層14を形成する表面の少なくとも一部は、ケイ素含有表面でよい。この方法は、キャパシター、蓄積セル、接触ライニング等の製造で使用する。

(もっと読む)

半導体装置

【課題】しきい値電圧の経時的な低下を抑制でき、またアルミ配線による絶縁膜の腐食やAlスパイクに起因するゲート・ソース間の短絡を防止できる半導体装置を提供する。

【解決手段】半導体装置のMOSFETセルは、ポリシリコンのゲート電極6およびn-ドリフト層2の上部に形成されたn+ソース領域4を備える。ゲート電極6上は層間絶縁膜7によって覆われており、Alのソース電極101は、層間絶縁膜7上に延在する。またゲート電極6にはAlのゲートパッド102が接続される。ソース電極101と層間絶縁膜7との間、並びにゲートパッド102とゲート電極6との間のそれぞれに、Alの拡散を抑制するバリアメタル層99が配設される。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

金属ゲート電極を有する半導体素子の製造方法

【課題】 収率が低下することなくCMOS集積回路の特性を最適可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板1の上の第1領域A内及び第2領域B内に各々形成された第1グルーブ15a及び第2グルーブ15bを有する層間絶縁膜15を形成する。次に、半導体基板1上に積層金属膜22を形成し、積層金属膜22上に非感光性を有する平坦化膜23を第1グルーブ15a及び第2グルーブ15bを充填するように形成する。第1領域A内の平坦化膜23を乾式エッチングによって選択的に除去し、第1領域A内の積層金属膜22を露出させ、第2領域B内の積層金属膜22を覆う平坦化膜パターン23pを形成する。これにより、第1領域A内の最上部金属膜を容易に除去することができるので、収率が低下することなく異なる仕事関数を有する第1金属ゲート電極及び第2金属ゲート電極を形成できる。

(もっと読む)

半導体素子の製造方法

【課題】タングステン層の膜残りの発生を抑制する。

【解決手段】半導体基板1、コンタクトホール3を備えた絶縁膜2、絶縁膜2の表面およびコンタクトホール3の表面を被覆する被覆層4、並びに、コンタクトホール3を埋込むタングステン(W)層5を有するウエハに対し、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で高速でドライエッチングする工程と、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で、低速でドライエッチングする工程と、ウエハを冷却しつつ、被覆層4が露出するまで、W層5を低速でドライエッチングする工程と、ウエハを冷却しつつ、コンタクトホール3内のW層5を絶縁層2の高さまで低速でドライエッチングする工程と、を有する半導体素子の製造方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、ソースドレイン間のリーク電流を低減する。

【解決手段】ゲート絶縁膜112に接する第1のゲート膜114として、インジウムと窒素を有し、バンドギャップが2.8電子ボルト未満の化合物導電体を用いる。この化合物導電体は、仕事関数が5電子ボルト以上、好ましくは5.5電子ボルト以上であるので、酸化物半導体膜106の電子濃度を極めて低く維持でき、その結果、ソースドレイン間のリーク電流が低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】縦型トランジスタとしての機能が低下することなく、安定性の高い半導体装置を提供する。

【解決手段】活性領域T及び活性領域Tを区画する素子分離領域3が形成されて成る半導体基板1と、活性領域Tに設けられた凹部9内に形成され、上面が半導体基板1の主面からなる第1ピラー1Aと、活性領域T及び素子分離領域3に渡って形成され、第1ピラー1Aに隣接する第2ピラー2と、第1ピラー1A及び第2ピラー2の各側面を覆うように形成されたゲート電極層10と、第1ピラー1A上に形成されたエピタキシャル半導体層6と、を具備してなり、第2ピラー2が、活性領域T内において第1ピラー1Aから離間して形成された半導体凸部1Bと、素子分離領域3に埋設された埋め込み絶縁膜からなる絶縁体凸部3Aとから構成され、半導体凸部1Bの上面が埋め込み絶縁膜の一部によって被覆されていることを特徴とする。

(もっと読む)

有機薄膜トランジスタの製造方法及び該方法で製造された有機薄膜トランジスタ

【課題】大面積の素子の製造が容易であり、ソース電極及びドレイン電極を形成する際にゲート絶縁層を損傷せず、有機絶縁材料が有する柔軟性を損なわない、有機薄膜トランジスタの製造方法を提供すること。

【解決手段】ゲート電極、及び該ゲート電極を被覆し、有機絶縁材料を含むゲート絶縁層を形成する工程;該ゲート絶縁層上に塗布法、無電解めっき法又は原子層堆積法を用いて導電性材料からなる第1導電層を成膜する工程;該第1導電層上にパターンニングされた第2導電層を形成する工程;該第2導電層で被覆されていない第1導電層の部分を除去して、第1導電層及び第2導電層からなるソース電極及びドレイン電極を形成する工程;及びソース電極、ドレイン電極、及び該ソース電極と該ドレイン電極に挟まれた領域のゲート絶縁層が被覆されるように、有機半導体層を形成する工程;を有する、有機薄膜トランジスタの製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

161 - 180 / 1,457

[ Back to top ]