Fターム[4M104CC03]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | ショットキー接触電極 (1,047)

Fターム[4M104CC03]に分類される特許

61 - 80 / 1,047

ノーマリーオフ型高電子移動度トランジスタ

【課題】 ノーマリーオフ型高電子移動度トランジスタを提供する。

【解決手段】 ノーマリーオフ型トランジスタは、III−V半導体材料の第1の領域、第1の領域上のIII−V半導体材料の第2の領域、第2の領域上のIII−V半導体材料の第3の領域、および第3の領域の少なくとも1つの側壁に隣接するゲート電極を含む。第1の領域はトランジスタのチャネルを提供する。第2の領域は第1の領域のバンドギャップより大きなバンドギャップを有し、チャネル内に2D電子ガス(2DEG)を引き起こす。第2の領域は第1の領域と第3の領域との間に挿入される。第3の領域は、トランジスタのゲートを提供し、トランジスタが正の閾値電圧を有するようにチャネル内の2DEGを空乏化するのに十分な厚さを有する。

(もっと読む)

半導体装置

【課題】ソース・ドレイン間容量の低下と、電流コラプスの抑制とを両立することが可能な半導体装置を提供すること。

【解決手段】基板10と、基板10上に形成された窒化物半導体層11と、窒化物半導体層11上に設けられたソース電極24、ゲート電極28、及びドレイン電極26と、ゲート電極28、及びゲート電極28とドレイン電極26との間の窒化物半導体層11の表面を覆う絶縁膜20と、窒化物半導体層11上であって、ゲート電極28とドレイン電極26との間に設けられたフィールドプレート30と、を具備し、ゲート電極28とドレイン電極26との間の領域の絶縁膜20上におけるフィールドプレート30の幅Wは0.1μm以上であり、フィールドプレート30のドレイン電極26側の端部と、ドレイン電極26のゲート電極28側の端部との距離L1は、3.5μm以上であり、動作周波数が4GHz以下である半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面の金属汚染を十分除去することにより、製造された炭化珪素半導体素子の初期特性を改善する。また、金属汚染を低減し、半導体装置の長期信頼性を向上する方法を提供する。

【解決手段】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面を酸化するステップと、該ステップにより炭化珪素表面に形成された二酸化シリコンを主成分とする膜を除去するステップとからなる炭化珪素表面の金属汚染除去工程を適用する。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体素子の製造方法

【課題】SiC半導体基板の不純物元素を捕捉・固定するためのゲッタリング層の形成を含む半導体素子の製造方法を提供する。

【解決手段】SiC基板10上にSiCエピタキシャル層16を形成し、該エピタキシャル層16にイオン注入および熱処理を行なって半導体素子を製造する方法において、上記SiC基板10よりも欠陥密度の高いゲッタリング層13を形成する工程を含むことを特徴とする半導体素子の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

炭化珪素ショットキダイオード

【課題】本発明の目的は耐圧変動が抑制された炭化珪素ショットキダイオードを提供する。

【解決手段】本発明の炭化珪素ショットキダイオードは、炭化珪素半導体基板1の表面に形成されるショットキ電極2と、その周囲を取囲むべく、炭化珪素半導体基板の表面に不純物が導入されて成るガードリング3と、該ガードリング上に延在すると共に当該ガードリングの周囲を取囲むように前記炭化珪素半導体基板の表面上に延在する絶縁膜4と、を備え、ショットキ電極は炭化珪素半導体基板の表面上においてガードリングに接し、かつ絶縁膜上にも延在し、ガードリングの幅寸法比を10、ショットキ電極がガードリングに接する幅寸法比を1、絶縁膜上に延在するショットキ電極の先端からガードリングの外周端までの離間距離比をXとするとき、離間距離比Xは、3〜9内に設定されている。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタと回生素子とを含み、優れたリカバリ特性によりスイッチング損失が低減された半導体装置を提供すること。

【解決手段】電界効果型トランジスタと回生素子とを含み、前記電界効果型トランジスタは、第1の導電型を有する第1の半導体層と、前記第1の半導体層の表面に配置された第2導電型を有する第2の半導体層と、前記第2の半導体層の表面に配置された前記第1導電型を有する第3の半導体層と、前記第1の半導体層と前記第2の半導体層と前記第3の半導体層とに隣接するように配置された絶縁膜を介して配置されたゲート電極と、第1の金属層と、第2の金属層と、を備え、前記回生素子は、前記第1の金属層と電気的に接続されるアノード端子と、前記第2の金属層と電気的に接続されるカソード端子と、を備えることを特徴とする半導体装置。

(もっと読む)

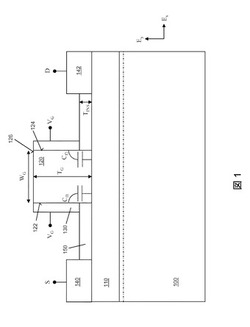

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

炭化珪素ダイオード

【課題】SiC製のJBSダイオードにおいて、サージ耐量を低下させることなく、通電劣化現象を抑制することのできる技術を提供する。

【解決手段】アクティブ領域のn−ドリフト層2内の表面側に、アノード電極4とオーミック接触する複数の第1p領域6と、第1p領域6とは分離され、アノード電極4とショットキー接触する複数の第2領域7とを形成し、アクティブ領域を(11−20)面に射影したときに、複数の第1p領域6を<1−100>方向に正孔の拡散長の2倍よりも広い間隔を置いて配置し、<1−100>方向に配置された第1p領域6と第1p領域6との間に第2p領域7を配置する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】順方向電圧降下の増大が抑制され、且つ順方向サージ耐量の高い、整流機能を有する半導体装置を提供する。

【解決手段】互いに対向する第1の主面110から第2の主面120に向かって延伸し、且つ底部が第2の主面120に達しない複数の溝部15が形成された第1導電型の半導体積層体10と、それぞれの外縁領域の一部が溝部15の側面に露出するように半導体積層体10の第1の主面110に互いに離間して埋め込まれた第2導電型の複数のアノード領域20と、アノード領域20の形成されていない領域において半導体積層体10とショットキー接合を形成し、且つアノード領域20とオーミック接合を形成して、半導体積層体10の第1の主面110に配置されたアノード電極30と、半導体積層体10の第2の主面120に配置されたカソード電極40とを備える。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】コンタクト抵抗を低減しつつ、イオン注入したp+層の消失を低減できる炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる炭化珪素半導体装置の製造方法は、(a)炭化珪素半導体基体表面にマスクとしての酸化膜マスク層21、酸化膜マスク層22を形成し、室温でイオン注入する工程と、(b)イオン注入を行った炭化珪素半導体基体表面を活性化アニールする工程と、(c)活性化アニール後の炭化珪素半導体基体表面を、ドライエッチングする工程と、(d)ドライエッチング後の炭化珪素半導体基体表面を犠牲酸化し、犠牲酸化膜5を形成する工程と、(e)犠牲酸化膜5を濃度10%以下の希フッ酸で5分以内のエッチングにより除去する工程と、(f)炭化珪素半導体基体裏面にオーミック電極6を、炭化珪素半導体基体表面の所定領域にショットキー電極7をそれぞれ形成する工程とを備える。

(もっと読む)

ZnO系半導体素子

【課題】リーク電流をより小さくし、かつ、電気的特性を改善したショットキーバリア型のZnO系半導体素子を提供する。

【解決手段】基板1上にn型ZnO系半導体層2、酸化アルミニウム膜3が順に形成されている。また、酸化アルミニウム膜3上には、金属電極4、パッド電極5が形成される。金属電極4は、Pd層4a上にAu層4bが積層された多層膜構造を有している。金属電極4は、半透明電極として機能する。金属電極4上にはパッド電極5が形成されている。基板1の裏面には金属電極4に対向するように、裏面電極6が形成される。n型ZnO系半導体層2とPd層4aでショットキーバリア構造を構成している。

(もっと読む)

61 - 80 / 1,047

[ Back to top ]