Fターム[4M104CC03]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | ショットキー接触電極 (1,047)

Fターム[4M104CC03]に分類される特許

101 - 120 / 1,047

半導体装置及び半導体装置の製造方法

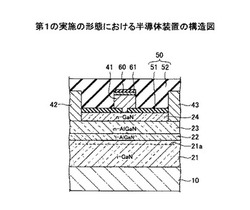

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

高耐圧半導体装置

【課題】従来の高耐圧半導体装置の場合よりも耐圧の低下を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタル層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118とを備え、最内周の第1ガードリング層122とエッジターミネーション層120との間隔が3μm〜5μmの範囲内にある高耐圧半導体装置100。

(もっと読む)

ワイドバンドギャップ逆阻止MOS型半導体装置

【課題】SiCやGaNなどの半導体材料を主要な半導体基板として用いた場合に、大電流を低オン電圧で流すことができ、高信頼性の逆耐圧特性を備えるワイドバンドギャップ逆阻止MOS型半導体装置を提供すること。

【解決手段】SiCのn-型のドリフト層1の一方の主面側に、p+型基板100と、該p+型基板100を貫通して前記n型のSiCのn-型のドリフト層1に達する複数の裏面トレンチ101と、該複数の裏面トレンチ101底部に前記n型のSiCのn-型のドリフト層1とショットキー接合を形成するチタン電極102とを備え、該ショットキー接合領域に対向する他方の主面側領域に、MOSゲート構造を含む活性領域200と、該活性領域200の外周を取り巻く耐圧構造領域203と、該耐圧構造領域203を取り巻き前記他方の主面から前記p+型基板100に達するとともに内部に絶縁膜21が充填されるトレンチ分離層20とを備える構造とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、フィールドプレート構造を絶縁膜の開口中心に対してばらつきなく形成できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、半導体層の表面に絶縁膜を形成する工程と、該絶縁膜の表面に開口を有するレジストを形成する工程と、該レジストと架橋反応するパターンシュリンク剤を該レジストに付着させ、該レジストの内周に硬化層を形成する工程と、該レジスト及び該硬化層をマスクとして該絶縁膜をエッチングする工程と、該硬化層を除去する工程と、該半導体層、該絶縁膜、及び該レジストの表面に金属層を形成する工程と、リフトオフ法により該レジスト及び該レジストの表面の該金属層を除去する工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

異種材料接合型ダイオード及びその製造方法

【課題】電流電圧特性を維持しつつ、アノード電極6の剥離に対する機械的強度を向上させる。

【解決手段】異種材料接合型ダイオードは、半導体基体1と、半導体基体1の上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主表面に接合された、ドリフト領域2とは異なる種類の材料からなるアノード電極6と、半導体基体1に接続されたカソード電極7とを備える。ドリフト領域2とアノード電極6との接合によりダイオードが形成されている。アノード電極6の主表面のうち、ドリフト領域2に接している側の主表面に、嵌合構造(3、G1)が形成されている。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体装置

【課題】小数キャリアの注入量により少数キャリアを引き抜くための時間を適宜設定可能な構成とし、重金属拡散等の技術を利用することなく、低VF特性と、短Trr、低Qrrを、デバイスの使用目的及び態様等に応じて最適化する。

【解決手段】半導体基板31の上に形成された低不純物濃度の第1導電型である第1半導体層32と、第2導電型であるガードリング33と、第2導電型である複数の島状の第3半導体層35と、第1半導体層32の上面の一部の領域に形成された第1のバリアメタル45と、第1半導体層32及び複数の第3半導体層35の上に形成された第1のバリアメタル42の第1のバリアハイト41より高い第2バリアメタル43、45を備えている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層の表面におけるダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】電極溝2Cの内壁面を含む化合物半導体層2の表面は、電極溝2Cを形成する際のドライエッチングによるエッチング残渣物12a及び変質物12bが除去されて、化合物半導体がフッ素(F)で終端されており、この電極溝2Cをゲート絶縁膜6を介してゲートメタルで埋め込み、或いは電極溝2Cを直接的にゲートメタルで埋め込んで、ゲート電極7が形成される。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

半導体装置

【課題】低いバリアハイトのバリアメタルを用いても伝導度変調を起させるように、別に第2のバリアメタル7を設けた構成とすることにより、ドリフト抵抗を低減し、ショットキーバリアダイオードの順方向電圧降下の低減を実現する。

【解決手段】ショットキーバリアダイオード1は、N−エピタキシャル層3と接合する第1のバリアメタル6はバリアハイトの低いメタルを用いるとともに、N−エピタキシャル及びP+ガードリング4にわたって上面にバリアハイトの高い第2のバリアメタル7を設ける構成としたので、微小電流領域は低VF特性のカーブとし、高電流領域ではP+ガードリング4からの小数キャリアの注入を積極的にさせて低VF特性のカーブとし、順方向電圧降下の低減する。

(もっと読む)

窒化物半導体装置

【課題】高周波数動作が可能で、ゲートリーク電流や電流コラプスを抑制できる窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極上に絶縁膜9を介してゲート電極7を配置する。さらに、ソース電極とドレイン電極との間の電子供給層表面を珪素膜11で被覆する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】制御性の良い製造方法のみで形成することができる高周波数動作が可能なノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層4とショットキー接触する浮遊電極8を配置し、この浮遊電極8上に絶縁膜を介してゲート電極7を配置する。さらに、ソース電極5とドレイン電極6との間の電子供給層表面を珪素膜11で被覆する。そして、ゲート電極7に正バイアス印加し、浮遊電極8に電子を蓄積される。

(もっと読む)

101 - 120 / 1,047

[ Back to top ]