Fターム[4M104CC03]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | ショットキー接触電極 (1,047)

Fターム[4M104CC03]に分類される特許

81 - 100 / 1,047

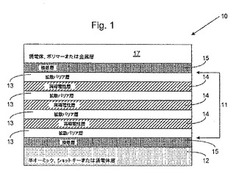

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の実施形態は、トレンチ構造におけるゲート・ソース間容量を低減できる半導体装置およびその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面側に設けられた第1主電極と、前記半導体層の第2の主面側に設けられた第2主電極と、前記半導体層の前記第1の主面側から前記第2の主面の方向に形成されたトレンチの内部に設けられ、前記第1主電極と前記第2主電極との間に流れる電流を制御する2つの第1制御電極と、前記トレンチの内部において、前記2つの第1制御電極と、前記第2の主面側の底面と、の間に設けられた第2制御電極と、を備える。前記2つの第1制御電極は、前記第1の主面に平行な方向に離間して設けられ、それぞれ第1の絶縁膜を介して前記トレンチの内面に対向し、前記第2制御電極は、第2の絶縁膜を介して前記トレンチの内面と対向する。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、サージ耐量が高く、順方向の電流密度を向上させることが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面に選択的に設けられた第2導電形の第1の領域と、前記第1の領域に接続して前記第1の主面に選択的に設けられた第2導電形の第2の領域と、を備える。そして、前記半導体層と前記第1の領域とに接して設けられた第1の電極と、前記第2の領域に接して設けられた第2の電極と、前記半導体層の前記第1の主面とは反対の第2の主面側に電気的に接続された第3の電極とを備える。

(もっと読む)

高耐圧半導体装置

【課題】高耐圧半導体装置の大型化を招くことなく、従来の高耐圧半導体装置900の場合よりも「気中放電による逆耐圧の低下」を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタルからなる第1電極層層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118と、半導体層110の表面上において第1電極層128を取り囲む領域に形成された絶縁層124とを備え、第2ガードリング層118が絶縁層124の外周近傍まで形成されている高耐圧半導体装置100。

(もっと読む)

窒化ガリウム半導体素子

【課題】高出力の窒化ガリウムショットキー・ダイオード素子を提供する。

【解決手段】1〜6μmの厚さを有するn+型ドープしたGaNダイオードから製造した窒化ガリウムベースの半導体ショットキー・ダイオードをサファイア基板の上に配設する。1μmを超える厚さを有するn−型ドープしたGaNダイオードを、複数の細長形の指にパターン化した前記n+型ドープGaNダイオード上に配設し、金属層をn−型ドープGaN層上に配設し、それとの間にショットキー接合を形成する。細長形の指の層厚、長さおよび幅は、降伏電圧が500Vを超え、電流容量が1アンペアを超え、かつ順方向電圧が3V未満である素子を得るように最適化される。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】SiC半導体装置において、不純物添加工程や表面保護膜形成におけるプロセス条件のばらつきがあっても、簡便に逆方向耐圧に大きな影響を与えないターミネーション構造(接合終端構造)を提供する。

【解決手段】素子の外周端部に、第1導電型の耐圧維持層および有限長さの前記第1導電型とは異なる第2導電型の領域からなる接合終端構造を備えたSiC半導体素子であって、前記接合終端構造の一部において、第1の方向である層方向に対して均一ではなく、前記接合終端領域の内側端であって前記素子の外周端から前記接合終端領域の外側端に向かって、前記第1導電型領域の不純物濃度が空間的に変調され、不純物濃度が徐々に減少する傾向を持って形成された接合終端構造を有することを特徴とするSiC半導体素子。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン抵抗が小さく、またオフ容量が低い、デュアルゲートを備えた電界効果トランジスタを提供する。

【解決手段】第1又は第2のゲート電極8は、ソース電極4側又は前記ドレイン電極5側に延びる第1のひさし部61と、第2又は第1のゲート電極8側に延びる第2のひさし部62とを有し、第2のひさし部62の長さが第1のひさし部61の長さより短い。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

半導体装置

【課題】p型SiC領域と金属との低抵抗コンタクトの実現を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、導電性材料を用いた電極240と、導電型がp型の炭化珪素(SiC)半導体部220と、を備えており、かかるp型のSiC半導体部220は、前記第1の電極240に接続され、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)、及びバリウム(Ba)のうちの少なくとも1種類の元素が前記電極との界面部に面密度がピークになるように含有されたことを特徴とする。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

ノーマリオフ型ヘテロ接合電界効果トランジスタ

【課題】p型不純物のドーピングおよびそのp型不純物の活性化を必要とすることなく、簡便かつ低コストでノーマリオフ型HFETを提供する。

【解決手段】ノーマリオフ型HFETは、厚さt1のアンドープAlxGa1−xN層(11)、この層(11)へ電気的に接続されかつ互いに隔てられて形成されたソース電極(21)とドレイン電極(22)、これらソース電極とドレイン電極との間でAlxGa1−xN層上に形成された厚さt2のアンドープAlyGa1−yN層(12)、ソース電極とドレイン電極との間においてAlyGa1−yN層の部分的領域上でメサ型に形成された厚さt3のアンドープAlzGa1−zN層(13)、およびAlzGa1−zN層上に形成されたショットキーバリア型ゲート電極(23)を含み、y>x>zおよびt1>t3>t2の条件を満たすことを特徴としている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

ダイオード用半導体担持電極材料

【課題】良好な整流特性を示すショットキー型ダイオードデバイスに利用可能な、半導体層を担持した安価な材料を提供する。

【解決手段】Cr含有量が10.5〜32.0質量%であるFe−Cr系合金の母材21と、その母材を酸化性雰囲気に加熱することによって形成させた表面酸化皮膜22とが一体となった材料であって、AESによる前記酸化皮膜表面からの深さ方向分析において酸素濃度が最大酸素濃度の1/2となる深さ位置に対応するSiO2換算深さを当該酸化皮膜の膜厚とするとき、当該酸化皮膜は、膜厚が17〜50nmのn型半導体であり、かつ皮膜表面側から順にFe主体アモルファス酸化物、Cr濃化したFe−Cr結晶酸化物を形成して母材とオーミック接合で一体化しており、n型半導体中のドナー密度が1E16cm−3〜1E18cm−3の範囲で含まれているダイオード用n型半導体担持電極材料。

(もっと読む)

81 - 100 / 1,047

[ Back to top ]