Fターム[4M104DD02]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918)

Fターム[4M104DD02]の下位に属するFターム

ダミーパターンの利用 (293)

側壁堆積膜の利用 (769)

Fターム[4M104DD02]に分類される特許

1 - 20 / 856

半導体装置の製造方法

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

(もっと読む)

熱処理方法

【課題】シリサイドの横方向への異常成長を防止しつつ、シリサイド形成を行うことができる熱処理方法を提供する。

【解決手段】半導体ウェハーWのソース・ドレイン領域にシリコンなどのイオンを注入し、そのイオン注入領域150を非晶質化する。非晶質化されたイオン注入領域150にニッケル膜158を成膜する。ニッケル膜158が成膜された半導体ウェハーWにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで1ミリ秒以上20ミリ秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーWの表面温度を目標温度T2から±25℃以内の範囲内に1ミリ秒以上100ミリ秒以下維持する。これにより、ニッケルシリサイドが縦方向に優先的に成長する。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体素子の製造方法

【課題】炭化シリコン基板に接するように、オーミック電極となるシリサイド層を形成するに際して、炭化シリコン基板由来の炭素が、オーミック電極内に拡散して表面に析出するのが抑えられ、オーミック電極の上に電極層を密着性良く形成することができる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法は、炭化シリコン基板2のオーミック電極形成領域2aにシリコン層を形成する第1工程と、シリコン層2上に金属層8を形成する第2工程と、熱処理を行うことによって、シリコン層2に含まれるSiと金属層8の構成元素とを反応させ炭化シリコン基板2と接するシリサイド層41を形成する第3工程と、Siと反応せずに残存した金属層8を除去することによって、シリサイド層41を露出させる第4工程とによってオーミック電極4を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造する。

【解決手段】半導体装置の製造方法は、半導体基板50上に絶縁膜を形成する工程と、絶縁膜上に、ゲート電極20およびハードマスク34を順に積層してなる積層体10を形成する工程と、積層体10をマスクとして、半導体基板50にイオン注入を行う工程と、積層体10の側面上に保護膜44を形成する工程と、エッチングによりハードマスク34を除去する工程と、エッチングにより保護膜44を除去する工程と、を備える。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】炭化珪素半導体装置の製造において、上面が平坦な終端構造とリセス状のアライメントマークとを少ないマスク数で形成すると共に、アライメントマークのリセスの深さを最適化する。

【解決手段】ハーフトーン露光法を用いて、SiCエピタキシャル層2に達する第1の開口部12aとSiCエピタキシャル層2に達しない第2の開口部とを有するレジストパターン11を、SiCエピタキシャル層2上に形成する。エッチングにより、第1の開口部12aに露出したSiCエピタキシャル層2にリセス状のアライメントマーク9を形成すると同時に第2の開口部12bをSiCエピタキシャル層2に到達させる。その後、イオン注入により、第2の開口部12bに露出したSiCエピタキシャル層2に、終端領域8を形成する。

(もっと読む)

半導体装置

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

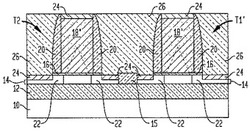

半導体装置および半導体装置の製造方法

【課題】ゲート電極とコンタクトとの間の短絡の発生を抑制する。

【解決手段】基板(2)に設けられた第1拡散領域(3)と、基板(2)に設けられた第2拡散領域(3)と、第1拡散領域(3)に接続された第1コンタクト(11)と、第2拡散領域(3)に接続された第2コンタクト(11)と、第1拡散領域(3)と第2拡散領域(3)の間に設けられたチャネル領域と、ゲート絶縁膜(6)を介してチャネル領域の上に設けられたゲート電極(5)とを具備する半導体装置を構成する。ゲート電極(5)は、第1コンタクト(11)と第2コンタクト(11)とに挟まれた第1領域(A−A’)と、第1領域と異なる第2領域(B−B’)とを備える。第1領域(A−A’)は、第1コンタクト側の第1側面と、第2コンタクト側の第2側面とを含む。第1側面は、第1コンタクトから離れる方向に傾斜する。第2側面は、第2コンタクトから離れる方向に傾斜する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

1 - 20 / 856

[ Back to top ]