Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

521 - 540 / 644

導電体構造、導電体構造の製造方法、素子基板および素子基板の製造方法

【課題】簡素な構成で、耐アルカリ性に優れ、加工精度の高い導電体構造を簡単に得ることができる。

【解決手段】本発明に係るTFTアレイ基板100は、基板10と、基板10上に画素毎に形成された画素電極20と、画素電極20に対応して、基板10上に形成されたTFT素子30とを備えている。そして、TFT素子30に接続された電極・配線31、32、34、331や、容量電極40などは、上層膜31b、32b、34b、331bおよび下層膜31a、32a、34a、331aが積層されて形成された積層体を有しており、下層膜31a等は、1種以上の周期律表第8族元素を含むアルミニウム合金により形成され、上層膜31b等は、下層膜31a等の上に積層されて、1種以上の周期律表第8族元素および窒素を含むアルミニウム合金により形成されている。

(もっと読む)

半導体装置の製造方法

【課題】nMOSTrおよびpMOSTrのそれぞれに適した仕事関数を有するシリサイド電極を有するCMOSのような半導体装置の製造方法を提供する。

【解決手段】半導体基板のnMOS領域およびpMOS領域にシリコンのような元素からなる電極パターンをゲート絶縁膜を介して形成する工程;電極パターンを含むnMOS領域を絶縁膜パターンでマスキングした後、全面にPd、Ptのような第1金属膜を成膜する工程;熱処理を施して第1金属のシリサイドからなるゲート電極を形成する工程;熱酸化処理を施してゲート電極表面にシリコン酸化膜を形成した後、未反応の第1金属膜を溶解除去する工程;前記電極パターンを含むpMOS領域を絶縁膜パターンでマスキングした後、全面にEr、Yのような第2金属膜を成膜する工程;熱処理を施して前記第2金属膜のシリサイドからなるゲート電極を形成する工程;および未反応の第2金属膜を溶解除去する工程;を含むことを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】電気回路の製造において、液滴吐出装置を用いて微細な配線などを形成する場合、吐出位置や吐出タイミングなどを含めて、より高い精度の吐出制御が要求されている。

【解決手段】CADツールを用いて電気回路の設計図面データを作成した後、その設計図面データを水平方向のドット間隔Xdpと垂直方向のドット間隔Ydpを1つの単位とする正方格子の第1ラスタデータに変換し、さらに水平方向のドット間隔Xdpとドット間隔Ydp/V(V>1)とを1つの単位とする長方格子の第2ラスタデータを作成する。なお、第1ラスタデータから第2ラスタデータに変換する前後で同じ任意吐出回数とする。

(もっと読む)

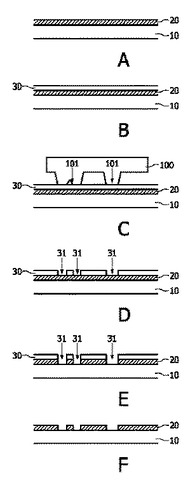

構造の作製方法

金層(20)が金酸化物マスク(30)でパターニングされる。前記マスクは、酸によってパターニングされ、好適にはマイクロコンタクトプリントによってパターニングされる。金酸化物マスク(30)は、金層(20)用のアルカリエッチング溶液中で安定である。金酸化物マスク(30)は、再曝露可能な金パッド(20)を形成するように維持されて良い。  (もっと読む)

(もっと読む)

酸化シリコン層の選択的除去

【解決手段】本発明は、装置を製造する方法に関し、前記装置の第1領域内に第1酸化シリコン層を形成し、前記装置の第2領域内に第2酸化シリコン層を形成するステップと、前記第1領域内に第1タイプのドーピングイオンを注入するステップと、前記第2領域内に第2タイプのドーピングイオンを注入するステップと、前記第1酸化シリコン層が除去され、前記第2酸化シリコン層の少なくとも一部が残るように、定められた継続時間前記第1及び第2領域をエッチングするステップとを備える。  (もっと読む)

(もっと読む)

トランジスタ、およびその製造方法

【課題】CMOSデバイス設計に適した仕事関数をもつメタルゲート電極を提供する。

【解決手段】

トランジスタおよびその製造工程が開示されている。相補型金属酸化膜半導体(CMOS)デバイスは、第1の厚さを有する第1ゲート電極を含むPMOSトランジスタと、第2の厚さを有する第2ゲート電極を含むNMOSトランジスタとを含み、第1の厚さは、第2の厚さよりも大きい。第1ゲート電極および第2ゲート電極は、同じ材料を含んでいることが好ましく、例として、TiSiN、TaNまたはTiNを含んでいるとよい。第1ゲート電極および第2ゲート電極の厚さによって、PMOSトランジスタおよびNMOSトランジスタの仕事関数が設定される。

(もっと読む)

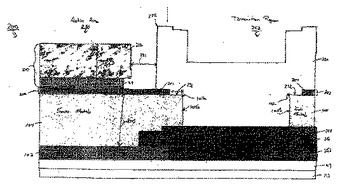

薄膜トランジスタ表示板及びその製造方法

【課題】一つの光マスクを用いてゲート線と画素電極を形成することにより、製造工程が簡単となり製造コストを低減できる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】基板110上に形成される画素電極191と、基板110上に形成されるゲート線121と、ゲート線121上に形成されるゲート絶縁膜140と、ゲート絶縁膜140上に形成されるデータ線171及びドレイン電極175と、データ線171及びドレイン電極175の一部上に形成される保護膜180をと備え、ゲート線121は画素電極191と同一層に形成される二重膜構造または三重膜構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線の幅が狭いフルシリサイド化ゲートプロセスを用いた半導体装置において、ゲート配線の設計ルールを変更することなく、ゲート配線とコンタクトとの接触面積を確保することが容易で且つゲート配線の配線抵抗が小さい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10に形成された素子分離領域12及び素子分離領域12に囲まれた活性領域11と、素子分離領域12及び活性領域11の上に形成され、フルシリサイド化されたゲート配線19と、ゲート配線19の側面を連続的に覆う絶縁性のサイドウォール21とを備えている。ゲート配線19の少なくとも一部分は、サイドウォール21から突出して形成されている。

(もっと読む)

半導体構造の形成方法

【課題】ゲート金属層の側壁エッジ酸化を防止する半導体構造の形成方法を提供する。

【解決手段】ゲート電極は、ドープトシリコン層108と該ドープトシリコン層上の金属層112とからなり、側壁エッジに沿って第2シリコン層120を形成する過程であって、前記第2シリコン層120は、前記側壁エッジのドープトシリコン層領域108及び金属層領域112に沿っており且つ前記ドープトシリコン層より不純物が低濃度にドープされ、前記側壁エッジの金属層領域に沿ってシリサイドを形成するために、前記第2シリコン層のシリコンを前記金属層領域の金属と反応させる過程と、前記反応後、前記ドープトシリコン層のドープトシリコンに対して、前記第2シリコン層のシリコンを選択的に除去する過程と、前記第2のシリコン層のシリコンを選択的に除去した後、側壁エッジのドープトシリコン層領域を酸化する過程を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製した半導体装置を提供することを目的とする。また配線等のパターンを所望の形状で制御性よく形成できる技術を提供することを目的とする。

【解決手段】連続した波状形状有する形状のパターンを、均一な間隔をもって隣接して備えた半導体装置である。隣接するパターンにおいて、吐出する液滴の中心の位置が線幅方向に一致しないように、配線の長さ方向にずらして吐出する。液滴の中心がずれているので、パターン同士の線幅の最大個所(節の最大値)同士が隣接することがなく、より狭い間隔に隣接したパターンを設けることができる。

(もっと読む)

半導体装置の製造方法

【課題】被エッチング膜に堆積されるハロゲン化カーボン膜およびハロゲン化シリコン膜を効果的に除去することが可能な半導体装置の製造方法を提供する。

【解決手段】シリコン膜と酸化シリコン膜および窒化シリコン膜の少なくとも一方の層が成膜された半導体基板をハロゲンを含むエッチングガスによりドライエッチング処理する際、エッチング面に堆積されるハロゲン化カーボン膜およびこのハロゲン化カーボン膜上のハロゲン化シリコン膜を除去する工程を含む半導体装置の製造方法であって、前記ハロゲン化カーボンおよびハロゲン化シリコンの除去は、前記ドライエッチング後に希フッ酸水溶液でウェットエッチング処理する工程と、前記エッチング面を含む全面にOHまたはHを含む有機材料膜を被覆した後、酸素プラズマによりアッシングする工程とを含むことを特徴とする半導体装置の製造方法。

(もっと読む)

導電性パターンの形成方法、半導体装置の製造方法、および有機電界発光素子の製造方法

【課題】塗布技術を用いながらも、表面平坦性を確保しつつ薄型化された導電性パターンを形成可能な方法を提供する。

【解決手段】金属微粒子sを溶媒中に分散させてなるペースト材料を基板1上に塗布してペースト材料膜3を塗布成膜する。ペースト材料膜3を焼成処理して導電性材料膜5とする。導電性材料膜5をパターニングすることにより導電性パターン5aを形成する。その後、この導電性パターン5aをゲート電極とし、これを覆う状態でゲート絶縁膜を形成し、この上部にソース/ドレイン電極を形成する。次に、ソース/ドレイン電極間におけるゲート絶縁膜上に半導体薄膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】歪シリコン層を用いることによりキャリアの移動度を向上させつつ、歪シリコン層下のシリコン・ゲルマニウム層中での導電性不純物の異常拡散を抑制した半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、基板上に形成されたSiGe層2と、SiGe層2上に形成された歪Si層3と、歪Si層3上にゲート絶縁膜4を介して形成されたゲート電極5nと、ゲート電極5nの両側における歪Si層3上に形成された2つの第1エピタキシャル成長層12nと、第1エピタキシャル成長層12n上に形成された2つの第2エピタキシャル成長層10nとを有する。第1エピタキシャル成長層12nは、導電性不純物として例えば砒素を含有する。砒素のプロファイルP1が、SiGe層2の上面よりも上方に位置している。

(もっと読む)

半導体装置

【課題】本発明は、配線の断線によるトランジスタの動作不良が防止された半導体装置を提供する。

【解決手段】基板11上にゲート配線12、ゲート絶縁膜13、ソース・ドレイン配線14がこの順またはこれと逆の順に積層された半導体装置において、ゲート配線12およびソース・ドレイン配線14のうち少なくとも基板11側に配置される一方は、金属材料層12a(14a)と導電性有機材料層12b(14b)またはカーボンブラック層とを有する積層構造からなることを特徴とする半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置の製造装置

【課題】ウエットエッチングでもウェハの中央部と外周部で配線幅にばらつきが生じ難く微細化が可能となる低コストの半導体装置の製造方法およびその製造装置を提供すること。

【解決手段】半導体ウェハ1の中央部のシード層6の膜厚を外周部のシード層6の膜厚に比べ薄くすることで、ウェットエッチング時に外周部のシード層6と中央部のシード層6がほぼ同時に除去され、エッチング時間を短縮できる。エッチング時間が短縮することで、Cu配線9の幅の狭まり量を小さくでき、また、半導体ウェハの外周部と中央部とのCu配線9の幅のばらつきを小さくできて、Cu配線9の微細化を図ることができる。

(もっと読む)

半導体デバイスの電極のための保護バリア層

【課題】 無鉛はんだに含まれている酸性のフラックスから電極を保護し、それによって、その下の活性な半導体接合を保護するバリア層を電極の直上に設けた半導体デバイスを提供する。

【解決手段】 半導体デバイスは、1つの表面上に、少なくとも1つの電極を有する半導体ダイと、電極の上方に形成されている少なくとも1つのはんだ付け可能なコンタクトと、電極の上方に形成され、かつ、はんだ付け可能なコンタクトを露出する開口を有するパッシベーション層とを備え、パッシベーション層の開口は、はんだ付け可能なコンタクトよりも広く、はんだ付け可能なコンタクトとパッシベーション層との間に、空隙が存在する。さらに、電極の上面上であって、はんだ付け可能なコンタクトの下面に沿って、および、空隙の全域にわたって、バリア層を配置されている。バリア層は、パッシベーション層の下に広がっている場合もあり、また、電極の全上面を覆っている場合もあり、さらに、電極の側壁に沿って広がっている場合もある。バリア層は、チタン層を備えている場合もあり、チタン層とニッケル層とを備えている場合もあり、電極およびその下の半導体ダイを、無鉛はんだに含まれている酸性のフラックスから保護する。  (もっと読む)

(もっと読む)

エッチング液組成物及びこれを利用した導電膜のパターニング方法並びにフラットパネルディスプレイの製造方法

【課題】本発明は、エッチング液組成物及びこれを利用した導電膜のパターニング方法並びにフラットパネルディスプレイの製造方法に関する。

【解決手段】エッチング液組成物及びこれを利用した導電膜のパターニング方法並びにフラットパネルディスプレイの製造方法に関し、前記エッチング液組成物は、リン酸、硝酸、酢酸、水及び添加剤を含み、前記添加剤は、塩素系化合物、硝酸塩系化合物、硫酸塩系化合物及び酸化調整剤を含む。また、前記エッチング液組成物を利用して、互いに異なる導電物質からなるゲート電極、ソース/ドレイン電極及び画素電極をパターニングする工程を行ってフラットパネルディスプレイを製造する方法を提供することによって、工程をさらに単純化させることができ、生産費用の低減と生産性の向上を期待することができる。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】パーティクルを効率的に除去して、金属薄膜の品質を向上させる薄膜トランジスタ基板の製造方法を提供する。

【解決手段】絶縁基板上にゲート金属層を形成する段階と、前記ゲート金属層上に感光膜パターンを形成する段階と、前記感光膜パターンを利用して、前記ゲート金属層をエッチングしてゲート配線を形成する段階と、前記感光膜パターンをストリップして、前記ゲート配線を露出させる段階と、前記露出したゲート配線を硝酸を含む洗浄液で洗浄する段階とを有する。

(もっと読む)

アレイ基板及びその製造方法並びに表示装置

【課題】不良発生を防止して表示品質を向上させることができるアレイ基板及びその製造方法並びに表示装置を提供する。

【解決手段】表示領域及び該表示領域の周辺に形成される周辺領域を有する基板と、前記表示領域に形成され、ゲート電極、ソース電極、及びドレイン電極を有し、前記ゲート電極は、第1金属膜と、該第1金属膜上に積層される第2金属膜と、該第2金属膜の窒化処理を通じて前記第2金属膜上に形成される第3金属膜とを有するスイッチング素子とを有する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】マスク数低減工程で、光リーク電流の急増を防止しTFT特性及び残像を改善すること。

【解決手段】ゲート線を形成し、その上にゲート絶縁膜、半導体層及びオーミックコンタクト層を形成し、オーミックコンタクト層上にMoを含む第1導電層、Alを含む第2導電層及びMoを含む第3導電層を形成し、第3導電層上に第1感光膜パターンを形成し、第1感光膜パターンをマスクとして用い第1導電層、第2導電層及び第3導電層をエッチングし、第1感光膜パターンをマスクとして用いオーミックコンタクト層及び半導体層をエッチングし、第1感光膜パターンを所定厚さ除去し第2感光膜パターンを形成し、第2感光膜パターンをマスクとして用い第1導電層、第2導電層及び第3導電層をエッチングしオーミックコンタクト層の一部を露出し、露出したオーミックコンタクト層を塩素系ガス及びフッ素系ガスを用いエッチングすることを含むTFT表示板の製造方法。

(もっと読む)

521 - 540 / 644

[ Back to top ]