Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

121 - 140 / 644

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

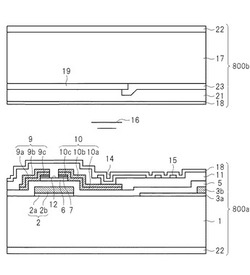

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

(もっと読む)

トランジスタ基板及びその製造方法

【課題】オフ領域におけるゲート電圧−ドレイン電流特性(Vg−Id特性)の劣化を抑制した薄膜トランジスタを備えたトランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTに設けられるチャネル保護層15の下層に形成された半導体層14のうち、ソース、ドレイン電極17間に側壁部が露出する領域(及びその近傍領域)が、酸素プラズマ処理により酸化処理されている。これにより、当該領域に酸化膜20が形成され、非導体化又は高抵抗化する。

(もっと読む)

エッチング液及びこれを用いた金属配線の形成方法

周期的な酸化およびエッチングのための装置と方法

電界効果型トランジスタ及びその製造方法

【課題】絶縁性が高く、かつ均一な膜厚を有するゲート絶縁膜を効率よく形成することができる電界効果型トランジスタの製造方法、及び該電界効果型トランジスタの製造方法により製造され、安定した特性を有する高性能な電界効果型トランジスタの提供。

【解決手段】前記第一の基材上にゲート電極を形成するゲート電極形成工程と、第二の基材上にゲート絶縁膜形成用樹脂溶液を塗布し、ゲート絶縁膜を形成する塗布工程と、前記ゲート絶縁膜表面の流動性が消失するまで乾燥する乾燥工程と、前記ゲート電極と、前記ゲート絶縁膜表面とを接触させて接触体を形成する接触工程と、前記接触体に対し、ゲート絶縁膜形成用樹脂のガラス転移温度以上の熱を加える加熱工程と、前記接触体から前記第二の基材を剥離し、第一の基材上にゲート絶縁膜を形成する剥離工程とを少なくとも含む電界効果型トランジスタの製造方法である。

(もっと読む)

表示装置および表示装置の製造方法

【課題】Cu合金をソース・ドレイン電極に用いたTFTにおいて、コンタクト膜に対して酸化処理を施す場合であっても、良好なオン特性を維持する表示装置を提供することを目的とする。

【解決手段】半導体層4と、銅と1種類の添加元素とを含む銅合金層を有するソース電極10およびドレイン電極9と、ソース電極10及びドレイン電極9のそれぞれの電極と半導体層4との間に形成されるコンタクト膜5と、それぞれの電極とコンタクト膜5との間に形成される酸化物膜8と、を含む薄膜トランジスタ基板を有する表示装置であって、コンタクト膜5は、不純物とシリコンとを含み、酸化物膜8は、シリコン、不純物および酸素を含むとともに、酸化物膜8における不純物濃度がコンタクト膜5における不純物濃度よりも低い、ことを特徴とする表示装置。

(もっと読む)

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】活性層―電極間の寄生抵抗に起因する素子特性のばらつきの少ないIGZO系電界効果型トランジスタを製造する。

【解決手段】基板B上に、IGZO系アモルファス酸化物からなる半導体層11、ソース電極22、ドレイン電極23、ゲート電極21およびゲート絶縁膜31とを備えてなる電界効果型トランジスタ1の製造方法において、半導体層11上にIGZO系アモルファス酸化物層20をスパッタ成膜により成膜し、その後アニール処理を行って、ソース電極22およびドレイン電極23の少なくとも半導体層11に接触する面側を構成する導電層を形成する。スパッタ成膜における背圧は1×10−5Pa未満とし、アニール処理におけるアニール温度を100℃以上、300℃以下とする。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ混載ロジックデバイスのRAM領域の閾値電圧のばらつきを低減する。

【解決手段】本発明の半導体装置は、ロジック領域101と、RAM領域102とが設けられたシリコン基板1と、ロジック領域101に形成されたNMOSトランジスタ20と、RAM領域102に形成されたNMOSトランジスタ40と、を備える。NMOSトランジスタ20、40は、ゲート絶縁膜5とメタルゲート電極6との順でシリコン基板1上に積層された積層構造を有する。NMOSトランジスタ20は、シリコン基板1とメタルゲート電極6との間に、構成元素として、ランタン、イッテルビウム、マグネシウム、ストロンチウム及びエルビウムからなる群から選択される元素を含む、キャップメタル4を有する。NMOSトランジスタ40には、キャップメタル4が形成されていない。

(もっと読む)

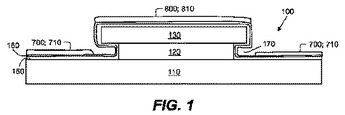

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

エッチング方法

【課題】エッチング液に含まれるインジウムイオン及びスズイオンの内、特にインジウムイオンの濃度を適切な濃度に維持することができるエッチング方法を提供する。

【解決手段】蓚酸を含むエッチング液Lが貯留された貯留槽11からノズル体16,17にエッチング液Lを供給して吐出させ、酸化インジウムスズ膜が形成された基板Kをエッチングするとともに、ノズル体16,17から吐出されたエッチング液Lを貯留槽11内に回収するエッチング工程と、貯留槽11内に貯留されたエッチング液Lをキレート剤が充填された吸着容器32,33内に通液させて、エッチングによりエッチング液Lに含まれるようになったインジウムイオン及びスズイオンを吸着,除去した後、貯留槽11内に還流させる金属除去工程とを含むエッチング方法において、貯留槽11内に貯留されるエッチング液Lのインジウムイオンの濃度を260ppm以下に維持する。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置の製造装置

【課題】希釈された溶液を用いて、貴金属を含む被処理膜等を迅速に且つ効果的にエッチングでき、且つ、設備の稼働率を向上できるようにする。

【解決手段】薬液を調合する薬液調合槽24と、調合された薬液を貯蔵する薬液貯蔵槽28と、貯蔵された薬液を用いて半導体基板を処理する処理チャンバ21とを有する半導体装置の製造装置を用いた半導体装置の製造方法は、薬液調合槽24において、酸化剤と錯化剤とを混合して第1の薬液を調合し、薬液調合槽24において、第1の薬液を活性化する。続いて、薬液貯蔵槽28において、活性化された第1の薬液と純水とを混合し、第1の薬液の濃度及び温度を調整することにより、第1の薬液を希釈した第2の薬液を調整する。続いて、処理チャンバ21に投入された半導体基板に第2の薬液を供給する。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

121 - 140 / 644

[ Back to top ]