Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

181 - 200 / 644

半導体素子およびその製造方法

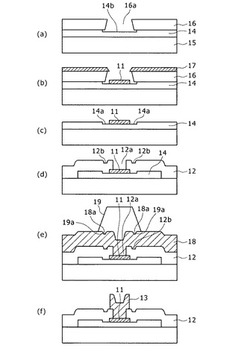

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子と、金属を含むゲート電極を有するMISFETとを備えた半導体装置において、ゲート電極の加工不良及びMISFETの特性の劣化を招くことなく、十分な抵抗値が得られる抵抗素子を実現する。

【解決手段】半導体装置は、抵抗素子RとMISFETとを備えた半導体装置である。抵抗素子Rは、半導体基板10上に形成された金属を含む第1の導電膜12aと、第1の導電膜12a上に形成されたシリコンを含む第2の導電膜17aと、第1の導電膜12aと第2の導電膜17aとの間に形成された絶縁膜13aとを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 酸化物半導体においてはイオン注入法による拡散層形成が難しいため、バルクシリコンMOSトランジスタや多結晶シリコンTFTのようなイオン注入法を用いた自己整合プロセスを組むことができない。本願では、リフトオフを用いる場合のような不都合の生じない自己整合プロセスを酸化物半導体において実現することを課題とする。

【解決手段】 裏面露光により製造される薄膜トランジスタ(TFT)において、チャネル層として酸化物半導体を用い、基板上の電極をマスクとして、基板の裏面側から導電膜上のネガレジストを露光し、ネガレジストの露光部分を残し前記ネガレジストを除去し、露光部分をエッチングマスクとする導電膜のエッチングにより、電極を加工する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】拡散層とゲート電極との少なくとも1つの上に耐熱性が向上したNiSi膜が形成された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Si基板200と、Si基板200内に形成された拡散層10と、Si基板200上にSiを用いて形成されたゲート電極20との少なくとも1つと、前記拡散層10と前記ゲート電極20との少なくとも1つ上に接触して形成されたP元素を含有したNiSi膜40,42と、を備えたことを特徴とする。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流を抑え、微小電流が流れる領域で電圧降下を低くすることができる半導体装置およびその製造方法を提供することを目的としている。

【解決手段】半導体装置の製造方法は、n型半導体層の一方の表面近傍に、微小電流が流れる領域で電圧降下が生じるように濃度設定されたp型半導体層を形成してpn接合を形成し、p型半導体層の表面に、アルミニウムの膜を形成し、アルミニウムとp型半導体層のシリコンを、焼結処理により反応させてアルミニウム・シリサイド膜を生成し、アルミニウム・シリサイド膜の上部に存在するアルミニウムであって、シリコンとは未反応のアルミニウムを、エッチングにより除去して表面を粗面化し、粗面化されたアルミニウム・シリサイド膜の上に、ニッケル膜を形成する。

(もっと読む)

TFT基板及びその製造方法

【課題】生産性及び性能が向上したTFT基板及びその製造方法を提供すること。

【解決手段】本発明にかかるTFT基板は、厚膜部及び厚膜部よりも膜厚が薄い薄膜部を有するゲート電極2と、厚膜部上及び薄膜部上に形成された半導体能動膜7と、半導体能動膜の内側であって、厚膜部より外側の薄膜部に対応する半導体能動膜7上に形成されたオーミックコンタクト膜8と、ソース電極9及びドレイン電極10を構成し、オーミックコンタクト膜8の内側に形成された電極膜30とを備えるものである。

(もっと読む)

電子素子及び電子素子の製造方法

【課題】簡易な構成でリーク電流の抑制された電子素子及びその製造方法を提供する。

【解決手段】基板上に設けられ、Mo−Nb合金から構成された第1の電極と、前記第1の電極上に配置された絶縁膜と、前記第1の電極に対して少なくとも前記絶縁膜を介して配置された第2の電極と、を備えた電子素子とする。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】半導体層をゲート電極によって遮光したボトムゲート型薄膜トランジスタのオフ電流を低減する。

【解決手段】ゲート電極層と、第1の半導体層と、前記第1の半導体層上に接して設けられた前記第1の半導体層よりもキャリア移動度が低い第2の半導体層と、前記ゲート電極層と前記第1の半導体層との間に接して設けられたゲート絶縁層と、前記第2の半導体層に接して設けられた不純物半導体層と、前記不純物半導体層及び前記第1及び第2の半導体層に一部が接して設けられたソース電極及びドレイン電極層と、を有し、前記第1の半導体層のゲート電極層側は全面が前記ゲート電極層によって覆われており、前記第1の半導体層と前記ソース電極及びドレイン電極層が接する部分のポテンシャル障壁は0.5eV以上である薄膜トランジスタを提供する。

(もっと読む)

半導体装置の作製方法

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するように、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるように第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面側で、Al電極膜表面にボイドが形成され難くすることのできる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の一方の主面側に半導体機能領域と所要のコンタクトホール8を含む層間絶縁膜7パターンを形成した後、該半導体基板1の前記一方の主面側の全面に、厚膜のアルミニウム膜またはアルミニウム合金膜を成膜して前記コンタクトホール8の底面を含む半導体基板1表面に導電接触させて所要の電極膜9を形成する際に、前記アルミニウムの成膜工程を膜厚に関して複数回に分け、複数回の前記アルミニウム成膜工程の間に、直前のアルミニウム膜表面の凹凸を等方性エッチングにより平坦化する工程を設ける半導体装置の製造方法とする。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:酸化ランタンまたは酸化ランタニド(例えば、Dy2O3、Pr2O3、Ce2O3)を含む層を準備する工程と;炭酸水である水溶液を供給することにより、酸化ランタンまたは酸化ランタニドを含む層を特定の領域で除去して、酸化ランタンまたは酸化ランタニドを含む層が上に蒸着された表面を露出させる工程とを備える方法が開示されている。

(もっと読む)

有機トランジスター、有機トランジスターの製造方法、電気光学装置および電子機器

【課題】大気中動作に優れており、また電気特性が経時的に劣化し難く、高いキャリア移動度とともに大きなon/off比を有する有機トランジスター、および有機トランジスターの製造方法、かかる有機トランジスターを備え信頼性の高い電子デバイスおよび電子機器を提供することにある。

【解決手段】本適用例の有機トランジスター1Aは、ソース電極20aと、ドレイン電極20bと、ソース電極20aとドレイン電極20bとの間に設けられた有機半導体膜30と、ゲート電極50と、有機半導体膜30とゲート電極50との間に設けられ、ゲート電極50と接する第1のゲート絶縁膜40aと、有機半導体膜30と接する第2のゲート絶縁膜40bとを有するゲート絶縁膜40と、を備え、第2のゲート絶縁膜40bが炭素原子と水素原子よりなる炭化水素化合物を含む。

(もっと読む)

半導体素子およびその製造方法

【課題】温度変化による半導体基板および金属層の熱膨張係数の差に起因して半導体基板にクラックが生じることを防止する。

【解決手段】半導体基板11上に、P型拡散層12の外周縁とN型半導体との境界を覆うように絶縁体被膜20をリング状に形成し、絶縁体被膜20の内側の半導体基板11表面に接触金属層15を積層し、接触金属層15および絶縁体被膜20の表面を覆うように応力緩和中間層30、クッション用電極層16および引き出し電極層17を形成する。絶縁体被膜20は二酸化珪素被膜13と二酸化珪素被膜13よりもエッチングレートの小さい窒化被膜14とからなる。応力緩和中間層30は、線膨張係数が応力緩和金属層16よりも半導体基板11に近い。引き出し電極層17(例えばNi)はクッション用電極層16(例えばAl)よりも表面処理液に対するエッチングレートが小さい。

(もっと読む)

181 - 200 / 644

[ Back to top ]