Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

221 - 240 / 644

半導体装置の製造方法

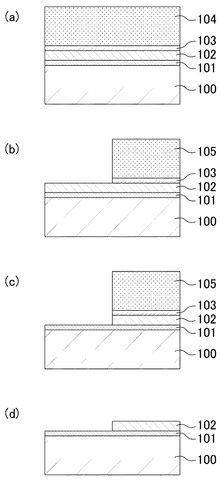

【課題】レジストマスクを用いたウエットエッチングにより、下地のゲート絶縁膜にダメージを与えることなく、寸法精度良く金属膜を加工する。

【解決手段】半導体装置の製造方法は、半導体基板100上に金属薄膜102を形成する工程(a)と、金属薄膜102の上にアルカリ水溶液可溶有機膜103を形成する工程(b)と、アルカリ水溶液可溶有機膜103の上にフォトレジスト膜104を形成する工程(c)と、フォトレジスト膜104に開口部を設けてレジストパターン105を形成する工程(d)と、薬液を用いて、開口部に露出するアルカリ水溶液可溶有機膜103を除去する工程(e)と、工程(e)の後に、ウエットエッチングにより、開口部に露出する金属薄膜102を除去する工程(f)とを備える。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

エッチング用組成物及びエッチング方法

【課題】 銀又は銀合金をエッチングする際に銀残渣を発生させず、しかもエッチング液を繰り返して使用してもエッチング速度が変化しないエッチング液及びそれを用いたエッチング方法を提供する。

【解決手段】 銀又は銀合金のエッチングにおいて、組成物全体に対し、銅イオンを0.01〜10重量%、硝酸を0.01〜10重量%、燐酸を10〜69重量%、カルボン酸を30〜50重量%含有し、残部は水である銀又は銀合金エッチング用組成物を用いる。

(もっと読む)

半導体装置

【課題】小型化・高耐圧化に優れ信頼性の高いパワー半導体装置を生産効率良くかつ高い製品歩留まりで製造できる誘電体分離型の半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板内のチップ配列領域において格子状のスクライブ領域によって区画された複数のチップ領域が整列配置され、前記複数のチップ領域の各々に半導体素子が形成された誘電体分離型の半導体装置であって、少なくとも前記複数のチップ領域の上には電極配線膜が厚さ0.8μm以上2.3μm以下で形成されており、前記電極配線膜の上に前記電極配線膜を保護するパシベーション膜が厚さ0.8μm以上2.7μm以下で形成されており、前記電極配線膜の厚さに対する前記パシベーション膜の厚さの比率が1.0以上1.2以下であることを特徴とする。

(もっと読む)

導電性ポリマー組成物およびそれから作製されたフィルム

本開示は、導電性ポリマー組成物、およびそれらの電子デバイス中での使用に関する。本発明の組成物は:(i)非フッ素化ポリマー酸でドープした少なくとも1種類の導電性ポリマーと;(ii)少なくとも1種類の高フッ素化酸ポリマーと;(iii)電気絶縁性酸化物ナノ粒子とを含む水性分散体である。  (もっと読む)

(もっと読む)

薄膜トランジスタアレイの製造方法及び表示装置

【課題】ソース電極とドレイン電極を均一且つ効率的に製造でき、薄膜トランジスタの半導体特性を低下させない薄膜トランジスタアレイ及びその製造方法を提供する。

【解決手段】基板1上にスキャンライン2を形成する工程と、外部接続用開口部11以外の領域に絶縁層2を形成する工程と、塗布型電極材料を全面に塗布、焼成して塗布電極層を形成した後にエッチングして少なくともソース電極4s及びドレイン電極4dを形成する工程と、ソース電極4s及びドレイン電極4dとを跨ぐ半導体層5を形成する工程と、封止層6を、外部接続用開口部11に露出しているスキャンライン2a上には少なくとも形成しないようにして形成する工程と、封止層6上に表示電極層8を形成した後にエッチングして表示電極8を形成する工程とを有する。この場合において、表示電極形成時のエッチングにより、外部接続用開口部11に露出しているスキャンライン2a上に残った余分な塗布電極層を除去する。

(もっと読む)

薄膜形成方法

【課題】薄膜中に有機物等が残存しにくく、耐熱性が低い基体も使用できる薄膜形成方法を提供すること。

【解決手段】少なくとも表面が界面光電気化学反応作用を有する金属化合物から成る粒子、前記粒子の表面を修飾する有機物、及び前記有機物で表面を修飾された前記粒子を分散させる分散媒から成る塗布液を、基体の表面に塗布して、塗布膜を形成する塗布膜形成工程と、前記塗布膜に、前記金属の界面光電気化学反応作用を促進する波長の電磁波を照射して前記粒子の表面を修飾する前記有機物を光分解する露光工程と、を備えることを特徴とする薄膜形成方法。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】酸化物半導体の活性層を、Ga等を主成分とする酸化物を含む層によって確実に保護して電界効果型トランジスタを製造する方法を提供する。

【解決手段】絶縁基板10又は絶縁層14上に、酸化物半導体層16と、該酸化物半導体層上にGaを主成分とする酸化物を含む第1の保護層18及びInを主成分とする非晶質酸化物を含む第2の保護層20をこの順に交互に少なくとも1層ずつ積層した複合保護層21とを有する積層体30をパターン形成する。次いで、積層体上に、対向配置されたソース電極40A及びドレイン電極40Bをパターン形成する。積層体のソース電極及びドレイン電極が形成されている領域以外において、複合保護層の最上部に位置する第2の保護層から、層ごとに順次エッチングして除去することにより、複合保護層の最下部に位置する第1の保護層を露出させる。

(もっと読む)

電界効果型トランジスタ

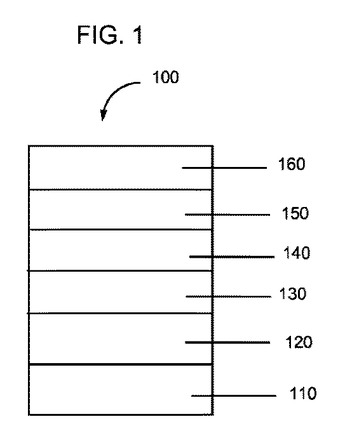

【課題】酸化物半導体の活性層が保護されるとともにソース電極及びドレイン電極とのオーミックコンタクトが確保され、閾値変動が抑制される電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタ100は、ゲート電極12と、ゲート電極上に形成されている絶縁層14と、絶縁層を隔てて前記ゲート電極に対向する位置に形成されている酸化物半導体層16と、Gaを主成分とする酸化物を含み、酸化物半導体層上に形成されている保護層18と、Inを主成分とする非晶質酸化物を含み、保護層上に形成されている接触層20A,20Bと、接触層上で、該接触層に接触しているとともに対向配置されているソース電極22A及びドレイン電極22Bと、を有する。接触層は、保護層とソース電極及びドレイン電極とが厚さ方向で重なる領域に形成されており、ソース電極とドレイン電極との間では分離している。

(もっと読む)

薄膜トランジスタの作製方法及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の導電膜と、絶縁膜と、半導体膜と、不純物半導体膜と、第2の導電膜とを積層し、この上にレジストマスクを形成し、第1のエッチングを行って薄膜積層体を形成し、該第1の導電膜に対してサイドエッチングを伴う第2のエッチングをドライエッチングにより行ってゲート電極層を形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。ドライエッチングを行う前に、少なくともエッチングされた半導体膜の側壁を酸化処理することが好ましい。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オン電流を低下させることなくオフ電流を低減し、画素回路やゲート駆動回路の制御に適用可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ100は、中央部がチャネルとなる微結晶シリコン層4と、この微結晶シリコン層4上に設けられた非晶質シリコン層5とを備え、ソース電極7およびドレイン電極8を、コンタクト層6a、6bにそれぞれ接続された下部ソース電極7aおよび下部ドレイン電極8aと、この下部ソース電極7aおよび下部ドレイン電極7bの上面に形成された上部ソース電極7bおよび上部ドレイン電極8bとの2層で構成するとともに、上部ソース電極7bおよび上部ドレイン電極8bのチャネル側端部をそれぞれ下部ソース電極7aおよび下部ドレイン電極8aのチャネル側端部に対して庇状に突出するように構成した。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】非晶質酸化物半導体から構成された活性層における、少なくとも電界効果型トランジスタとして構成されたときにソース電極及びドレイン電極の界面に連続する領域の浸食の抑制された電界効果型トランジスタの製造方法を提供する。

【解決手段】電界効果型トランジスタ10の製造方法によれば、第1の導電層形成工程において非晶質酸化物半導体層17上に第1の導電層20を形成した後に、パターン形成工程及び加工工程においてレジストパターン30を形成して該レジストパターン30による非保護領域をエッチングすることによって、第1の導電層20と共に非晶質酸化物半導体層17を加工して活性層18上に第1の導電層20の積層された状態とした後に、第1の導電層20からレジストパターン30を剥離する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に対して略垂直な形状のゲート電極を有する半導体装置の製造方法を提供する。

【解決手段】半導体基板11の主面11aにゲート絶縁膜12を介して形成された金属含有膜19を有するゲート電極膜30上にマスク材31を形成し、マスク材31を用いてゲート電極膜30をゲート絶縁膜12が露出するまで異方性エッチングし、ゲート電極13を形成する工程と、金属含有膜19を酸化し、金属含有膜19の側壁に酸化膜34を形成する工程と、ゲート絶縁膜12を等方性エッチングし、半導体基板11上に露出したゲート絶縁膜12を除去するとともに、半導体基板11と金属含有膜19との間に挟まれたゲート絶縁膜12を後退させる工程と、金属含有膜19を選択的に等方性エッチングし、金属含有膜19のゲート絶縁膜12より外側に突出した部位を除去する工程と、を具備する。

(もっと読む)

薄膜トランジスタ、その製造方法および表示装置

【課題】大きなオン電流を維持したままオフ電流を低減するとともに、製造が容易なLDD領域を備える薄膜トランジスタを提供する。

【解決手段】平面視において、ドレイン電極171をゲート電極121から所定の距離だけ離して形成することによって、LDD領域165となるオーミックコンタクト層161を水平方向に形成する。この場合、LDD領域165は、ゲート電極121の電位に基づく電界の影響を受けにくくなり、実質的にドレイン電極171の電位に基づく電界による電界集中のみを緩和する。したがって、TFT100は、結晶性シリコン膜からなるチャネル領域141cを形成することにより、大きなオン電流を維持することができると同時に、オフ電流を十分低減することができる。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

薄膜トランジスターの製造方法

【課題】逆スタガ型のTFTをマスク数を削減して形成する場合、アモルファスシリコンを用いる場合にはチャネルシリコン層とコンタクトシリコン層とを重ねて形成し、コンタクト層をエッチングすることでチャネル層を形成することができたが、ポリシリコンを用いる場合には、レーザーアニールを行う際に、チャネルシリコン層とコンタクトシリコン層とが熔融して混合してしまうため、この製造方法が使えないという課題があった。

【解決手段】第1多階調マスクを用いて形成した第1厚フォトレジスト層123Aをマスクとしてイオンドーピングを行い、半導体層111が露出している領域と、第1薄フォトレジスト層123Bとを透過させて半導体層111中にリンのドーピングを行う。次に第1厚フォトレジスト層123Aと、第1薄フォトレジスト層123Bとをマスクとして、半導体層111をエッチングすることで、フォトマスクの使用枚数を削減する。

(もっと読む)

半導体装置、およびその作製方法

【課題】アクティブマトリクス型表示装置等の半導体装置において、トランジスタの駆動能力を低下させることなく寄生容量の容量値を低減することを課題の一とする。または、寄生容量の容量値を低減した半導体装置を低コストに提供することを課題の一とする。

【解決手段】トランジスタのゲート電極と同一の材料層で形成される配線と、ソース電極またはドレイン電極と同一の材料層で形成される配線との間に、ゲート絶縁層以外の絶縁層を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗な電極部を有し、且つパターニング工程数の削減可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散層が形成された半導体基板の上に第1の金属層を形成する工程と、前記第1の金属層の上に開口部を有する絶縁層を形成する工程と、前記絶縁層の開口部において、前記第1の金属層の上に第2の金属層を形成する工程と、前記絶縁層を除去する工程と、前記第2の金属層の露出面に前記第2の金属層よりもイオン化傾向の小さい金属を含む第3の金属層を被覆する工程と、前記第3の金属層をマスクとして前記第1の金属層を除去することにより、前記第1の金属層と前記第2の金属層と前記第3の金属層とを有する電極配線を形成する工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

Cu合金膜および表示デバイス

【課題】薄膜トランジスタの半導体層との高い密着性、および優れたウェットエッチング性を示すCu合金膜を提供する。

【解決手段】薄膜トランジスタの半導体層と直接接触する表示デバイス用Cu合金膜であって、前記Cu合金膜は、下記(1)および(2)の要件を満足する酸素含有合金膜であることを特徴とする表示デバイス用のCu合金膜である。

(1)Cu合金膜は、Ni、Al、Zn、Mn、Fe、Ge、Hf、Nb、Mo及びWよりなる群から選ばれる少なくとも1種の元素を合計で0.10原子%以上5.0原子%以下含有する。

(2)Cu合金膜は、酸素含有量が異なる下地層と上層を有し、前記下地層は前記半導体層と接触しており、前記下地層の酸素含有量は0.1原子%以上30原子%以下であり、前記上層の酸素含有量は0.1原子%未満(0原子%を含む)である。

(もっと読む)

221 - 240 / 644

[ Back to top ]