Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

301 - 320 / 644

電子デバイス、及びその製造方法、並びに電子機器

【課題】比抵抗が小さく、透明導電膜との接触抵抗の上昇を回避可能であって、アルカリ系の薬液耐性に優れ、かつ良好な反射率特性を兼ね備えるAl合金膜を備える電子デバイスを提供すること。

【解決手段】本発明に係る電子デバイスは、基板上に、Al合金膜を少なくとも備える金属膜パターン10と、Al合金膜と少なくとも一部の領域で直接接続する透明導電膜パターン30とを備え、Al合金膜の最上層は、Ni,Co,Fe,Pd,Pt、Mo,及びWから選ばれる少なくとも1つの金属元素が添加され、かつ、O元素の組成比が、0.1at%以上、6.0at%以下であるO元素含有−Al合金膜が形成されている。

(もっと読む)

薄膜トランジスタ及びその作製方法、並びに表示装置及びその作製方法

【課題】従来よりも少ないマスク数で作製する薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の導電膜と、絶縁膜と、半導体膜と、不純物半導体膜と、第2の導電膜とを積層し、この上に3段階の厚さを有するレジストマスクを形成し、第1のエッチングを行って薄膜積層体を形成し、該薄膜積層体に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、その後レジストマスクを後退させて半導体層、ソース電極及びドレイン電極層を形成することで、薄膜トランジスタを作製する。3段階の厚さを有するレジストマスクは、例えば、4階調のフォトマスクにより形成する。

(もっと読む)

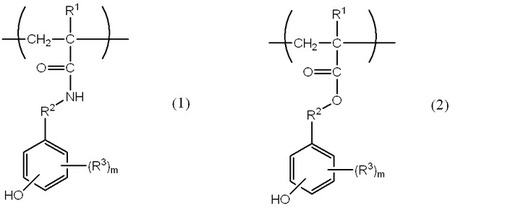

メッキ造形物製造用ポジ型感放射線性樹脂組成物、転写フィルムおよびメッキ造形物の製造方法

【課題】メッキ造形物の製造に好適なポジ型感放射線性樹脂組成物に関する。

【解決手段】(A)下記一般式(1)および/または(2)で表される構造単位(a)と、酸解離性官能基(b)とを含有する重合体、(B)感放射線性酸発生剤および(C)有機溶媒を含有し、かつ重合体(A)100重量部に対して、特定構造の感放射線性酸発生剤が1〜20重量部含有することを特徴とするメッキ造形物製造用ポジ型感放射線性樹脂組成物。 (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】微細なラインアンドスペースパターンを含むパターンを形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工材上に、第1の芯材、および前記第1の芯材下に位置し、前記第1の芯材よりも幅の大きい第2の芯材を形成する工程と、前記第1および第2の芯材の側面を覆うように被覆膜を形成する工程と、前記被覆膜を前記第1および第2の芯材の側面に位置する部分を残して除去し、側壁マスクに加工する工程と、前記側壁マスクをマスクとして前記第1および第2の芯材にエッチングを施し、前記第1の芯材、および前記第2の芯材の前記側壁マスクに上面を覆われていない部分を除去して、前記側壁マスク、および前記側壁マスクの直下に残った前記第2の芯材を含むエッチングマスクを形成する工程と、前記エッチングマスクをマスクとして前記被加工材にエッチングを施し、前記被加工材をパターン加工する工程と、を含む。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

電磁波検出素子

【課題】製造コストの増加を抑えつつ、信号配線の電子ノイズをより低減させた電磁波検出素子を提供する。

【解決手段】複数の信号配線3を基板1の複数の溝30内にそれぞれ設けており、電磁波の照射に応じて電荷を発生する半導体層6及び当該半導体層6に発生した電荷を収集する収集電極11を有するセンサ部103を基板1の上層に設けた。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極間にエアギャップを制御良く形成する。

【解決手段】本発明の半導体装置の製造方法では、半導体基板2上のゲート絶縁膜3上に浮遊ゲート電極用の多結晶シリコン層4を形成するときに、多結晶シリコン層4の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、この多結晶シリコン層4上に形成したゲート間絶縁膜5上に制御ゲート電極用の多結晶シリコン層9を形成するときに、多結晶シリコン層9の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、複数のゲート電極の側面が露出した状態で熱酸化処理を行なった後、エッチングすることにより、多結晶シリコン層4、9の各側面に凹部11、12を形成し、複数のゲート電極間に絶縁膜7を埋め込み、埋め込まれた絶縁膜7の中にエアギャップ8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】従来の半導体装置の製造方法には、さらなる効率化が困難であるという課題がある。

【解決手段】第1基板41に設けられた第1半導体層51の表示面側に、平面視で第1半導体層51の一部に重なる第1導電パターン107を形成する工程と、第1導電パターンをマスクとして第1半導体層51に不純物を注入する第1注入工程と、前記第1注入工程の後に、第1導電パターン107の一部を除去して、第1導電パターン107と第1半導体層51とが平面視で重なる領域である第1重畳領域113aを縮小する縮小工程と、前記縮小工程の後に、ゲート電極部57をマスクとして第1半導体層51に前記不純物を注入する第2注入工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】積層構造のゲート電極をもつ薄膜トランジスタにおいて、ゲート電極上の絶縁層のステップカバレージの低下を防止し、かつ、前記第1金属層のヒロック(hillock)の生成を防止する。

【解決手段】基板上に第1金属層43と第2金属層45を連続して蒸着し、さらに所定幅(W1)を持つ感光膜47を形成する(図5(a))。感光膜47をマスクとして第2金属層45を等方性のウェットエッチング方法で感光膜の幅(W1)よりも1μm乃至4μm程度小さな幅(W2)にパターニングする(図5(b))。次に、感光膜47をマスクとして第1金属層43を異方性エッチング方法で幅(W1)を持つようにパターニングして積層構造のゲート電極を形成する(図5(c))。1μm<W1−W2<4μmの関係にあればステップカバレージの低下とヒロックの両方を防止できる。

(もっと読む)

半導体発光素子及びその製造方法、ランプ

【課題】p型半導体層の上面に形成された透光性電極層の接触抵抗が十分に低く、駆動電圧(Vf)の低い半導体発光素子及びその製造方法を提供する。

【解決手段】基板101と、基板101上にn型半導体層104と発光層105とp型半導体層106とが順次形成されてなる積層半導体層20と、p型半導体層106の上面106aに形成された透光性電極層109とを具備する半導体発光素子1であって、透光性電極層109が、ドーパント元素を含み、透光性電極層109中のドーパント元素の含有量が、p型半導体層106と透光性電極層109との界面109aに近づくに従って徐々に減少しており、透光性電極層109に、界面109aから透光性電極層109内に向かってp型半導体層106を構成する元素が拡散してなる拡散領域が形成されている半導体発光素子1とする。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗率を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ耐食性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Coを0.05〜0.5原子%、およびGeを0.2〜1.0原子%含み、かつAl合金膜中のCo量とGe量が下記式(1)を満たすことを特徴とする表示装置用Al合金膜。

[Ge]≧−0.25×[Co]+0.2 …(1)

(式(1)中、[Ge]はAl合金膜中のGe量(原子%)、[Co]はAl合金膜中のCo量(原子%)を示す)

(もっと読む)

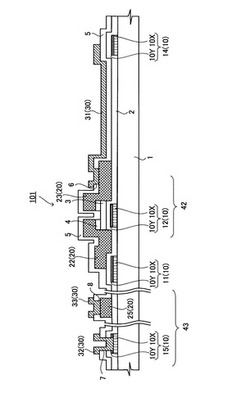

半導体装置及び半導体装置の作製方法

【課題】外部ストレスによる亀裂などの破損による形状不良や特性不良などの半導体装置の不良を低減することを目的の一とする。よって、信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程中においても上記不良を低減することで半導体装置の製造歩留まりを向上させることを目的の一とする。

【解決手段】一対の第1の耐衝撃層及び第2の耐衝撃層に挟持された半導体集積回路において、半導体集積回路と第2の耐衝撃層との間に衝撃拡散層を有する。外部ストレスに対する耐衝撃層と、その衝撃を拡散する衝撃拡散層とを設けることで、半導体集積回路の単位面積あたりに加えられる力を軽減し、半導体集積回路を保護する。衝撃拡散層は弾性率が低く、破断係数が高い方が好ましい。

(もっと読む)

TFTの製造方法及びTFT

【課題】生産性及びトランジスタ特性が向上するTFTの製造方法及びTFTを提供すること。

【解決手段】本発明にかかるTFTの製造方法では、レーザー光10を非晶質半導体膜に対して照射し、ゲート電極2によって反射させて再度非晶質半導体膜に照射する。これにより、ゲート絶縁膜3との界面部の非晶質半導体膜を結晶性を有する微結晶半導体膜4に変換する。そして、不純物濃度がゲート電極2とは反対側からゲート電極2側に向かって連続的に単調減少するように、微結晶半導体膜4に対して不純物元素11を注入する。

(もっと読む)

金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFT

【課題】生産性が向上し、かつ寸法精度が良い金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFTを提供すること。

【解決手段】本発明にかかる金属配線の製造方法では、まず、主成分金属に、主成分金属より酸化物の生成エネルギーが低い添加金属が添加された第2の金属膜30を成膜する。そして、第2の金属膜30を酸化させて金属酸化物を形成し、第2の金属膜30の表面に酸化層32を形成する。次に、酸化層32上にフォトレジスト31を形成して、第1のドライエッチング条件により、酸化層32をエッチングする。そして、第1のドライエッチング条件の場合と比較して、主成分金属の金属酸化物に対する選択比が高い第2のドライエッチング条件により、下層の第2の金属膜30をエッチングする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

有機半導体装置

【課題】製造工程を簡略化し、占有面積を低減したキャパシタ部とトランジスタ部を有する有機半導体装置の提供。

【解決手段】基板1と、基板1上に形成された凸部の少なくとも上面部を構成する第1の電極2と、第1の電極2上及び凸部の側面2b上に設けられる第1の絶縁膜3と、凸部の上方2aの第1の絶縁膜3上に設けられる第2の電極4と、凸部の側面2bの下方に隣接して基板1上に設けられる第3の電極5と、凸部の側面2b上の第1の絶縁膜3を覆い、第2の電極4及び第3の電極5と接するように設けられる有機半導体層6とを備え、第1の電極2と、第1の絶縁膜3と、第2の電極4とから、キャパシタ部20が構成され、第2の電極4及び第3の電極5からなるソース電極及びドレイン電極と、第1の電極2からなるゲート電極と、第1の絶縁膜3からなるゲート絶縁膜と、有機半導体層6からなる半導体層とから、トランジスタ部21を構成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】端部の勾配が急峻であり、所望の膜厚を確保することができ、マスクパターンとの形状の差が抑えられる導電膜を、エッチングを用いて作製する。

【解決手段】膜厚1μm以上10μm以下のアルミニウムまたはアルミニウム合金を含む導電膜を、ウェットエッチングを用いて所定の膜厚となるまでエッチングした後、残りをドライエッチングでエッチングすることで、サイドエッチングを抑え、なおかつマスクの膜厚が減少するのを抑える。サイドエッチングを抑え、なおかつマスクの膜厚が減少するのを抑えることで、膜厚1μm以上10μm以下といった厚膜のアルミニウムまたはアルミニウム合金を含む導電膜であっても、端部の勾配が急峻であり、所望の膜厚を確保することができ、マスクパターンとの形状の差が抑えられるようにエッチングすることが可能となる。

(もっと読む)

301 - 320 / 644

[ Back to top ]