Fターム[4M104DD91]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 基板へ不純物導入、拡散領域形成(析出後) (478)

Fターム[4M104DD91]の下位に属するFターム

電極(バリア層を含む)からの拡散 (55)

Fターム[4M104DD91]に分類される特許

101 - 120 / 423

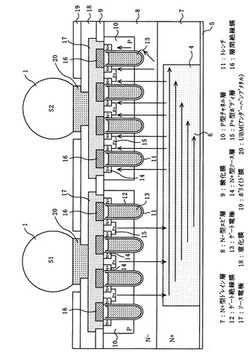

半導体装置及びその製造方法

【課題】電流が、縦方向、横方向、そして縦方向と連続的に流れる半導体装置において

縦方向並びに横方向の電流経路に係る電気抵抗を低減し、高効率、高性能な半導体装置を実現する。

【解決手段】本発明の半導体装置は、半導体基板の表面側にドレインを共有するMOS構造が2つ形成され、かつ、半導体基板の裏面側のN+型ドレイン層7の内部に、一方のMOS構造のドレイン領域から他方のMOS構造のドレイン領域まで、延在して形成された複数の堀状の開口部4を有する。堀状の開口部4はN+型ドレイン層7の内部の、N+型ドレイン層7とN−型エピ層8の境界近傍まで、深く形成されている。そして、堀状の開口部4の中には裏面電極5と電気的に接続された、N+型ドレイン層7に比べて抵抗の低い、金属電極6が形成されている。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 ジャンクションバリアショットキダイオード構造の特性を向上する。

【解決手段】 半導体装置の製造方法は、n型の半導体基板にp型半導体領域をその上面の一部に露出するように形成するp型領域形成工程と、半導体基板の上面に露出するn型半導体領域にショットキ接触するショットキ電極を形成する第1電極形成工程と、半導体基板の上面に露出するp型半導体領域にオーミック接触するオーミック電極を形成する第2電極形成工程を備えている。オーミック電極は、ショットキ電極とは異なる材料によって形成される。そして、第1電極形成工程は、第2電極形成工程よりも先に実施される。

(もっと読む)

半導体装置およびその作製方法

【課題】インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む酸化物半導体膜を用いる薄膜トランジスタにおいて、ソース電極またはドレイン電極のコンタクト抵抗を低減した薄膜トランジスタ及びその作製方法を提供することを課題の一つとする。

【解決手段】ソース電極層及びドレイン電極層とIGZO半導体層との間に、IGZO半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

固体撮像装置、その製造方法および撮像装置

【課題】本発明は、画素部のMOSトランジスタ上で異なる2層のシリサイドブロック膜の一部が重なるように形成して、白傷、暗電流を低減することを可能にする。

【解決手段】半導体基板11に、光電変換部21を備えた画素部12とその周辺に形成された周辺回路部13を有し、画素部12のゲート電極32の側壁にサイドウォール形成膜で形成された第1サイドウォール33と、周辺回路部13のゲート電極52の側壁にサイドウォール形成膜で形成された第2サイドウォール53と、光電変換部21上および画素部12のMOSトランジスタ30の一部上にサイドウォール形成膜で形成された第1シリサイドブロック膜71と、画素部12のMOSトランジスタ30上に、第1シリサイドブロック膜71の一部上に重なる第2シリサイドブロック膜72を有し、第1、第2シリサイドブロック膜71、72で画素部12のMOSトランジスタ30上が被覆されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、半導体基体との界面における組成の均一性に優れ、ショットキー接合層との十分に高い密着性が得られるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第一半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第二半導体領域6bと、第一半導体領域1aにオーミック接触するオーミック接合層7と、第二半導体領域6bにショットキー接触するショットキー接合層8とを備え、オーミック接合層7の二乗平均粗さが、20nm以下である半導体装置とする。

(もっと読む)

フォトマスクの製造方法及びプログラム

【課題】多重露光技術において、マスクパタン形成時における工程の複雑化を防止し、設計データに従った均一な形状を形成するためのマスクパタンを効率的に生成する。

【解決手段】目的となる設計データ101において、先端部分103a,104aで所定の離間距離をおいて対向する一対の線状設計パタン103,104について、設計データ上で仮想的に先端部分103a,104a間を接続する補助パタン105を配する処理を行い多重露光用マスクパタンを生成する。

(もっと読む)

半導体装置の製造方法

【課題】high−k膜を含む絶縁膜及びメタルゲートを有するMISFETにおいて、フォトレジストパターンをマスクとして、high−k膜上のTiN膜にパターン転写するためのドライエッチングをする際、high−k膜およびhigh−k膜上のTiN膜がプラズマによるダメージを受けるのを防ぐ。

【解決手段】SiN膜5および第2のTiN膜6を加工マスクとして使い、ウェットエッチングによりパターン転写をすることで、high−k膜3およびhigh−k膜3上のゲート電極である第1のTiN膜4が、プラズマに晒されることによるダメージを受けることを防ぎ、パターン転写の精密性を保持することができる。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】

基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】従来に比べて製造工程を簡易化することができ、かつ、絶縁膜が損傷を受けることを防止することができ、製造コストの低減と信頼性の向上を図ることのできる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】P型半導体層11上に、下側から順に第1ゲート絶縁膜2a、第2ゲート絶縁膜2b、第1金属膜3a、第2金属膜3b、第3金属膜3cが形成されたNチャンネルMISトランジスタ21、及び、N型半導体層10上に、下側から順に第1ゲート絶縁膜2a、第2ゲート絶縁膜2b、第1金属膜3a、第3金属膜3cが形成されたPチャンネルMISトランジスタ20を具備した半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度の向上を実現し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10に形成されたチャネル領域44上にゲート絶縁膜18を介して形成されたゲート電極20bと、ゲート電極の側壁部分に形成されたサイドウォール絶縁膜26と、ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層38と、ソース/ドレイン拡散層に埋め込まれ、半導体基板と格子定数が異なる半導体層52とを有し、半導体層は、半導体基板のうちのサイドウォール絶縁膜の下方領域に食い込むように形成された第1の突出部54と、半導体基板のうちのサイドウォール絶縁膜の直下の部分に食い込むように形成された第2の突出部56とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置およびその製造方法

【課題】非対称トランジスタの接合リークを抑制する。

【解決手段】半導体装置100は、シリコン基板101の上部に設けられたゲート電極115と、ゲート電極115の異なる側方においてシリコン基板101に設けられた第一不純物拡散領域103および第二不純物拡散領域105とを有するMOSFET110を含む。MOSFET110は、第一不純物拡散領域103の上部にエクステンション領域107を有するとともに第二不純物拡散領域105の上部にエクステンション領域107を有さず、第一不純物拡散領域103上に第一シリサイド層109を有するとともに、ゲート電極115側端部の近傍において第二不純物拡散領域105上にシリサイド層を有しない。

(もっと読む)

半導体装置の製造方法

【課題】 残留有機物の除去、及びゲート絶縁膜のダメージ回復を目的として、酸化性雰囲気でRTAを行うと、ゲート絶縁膜の端面から内側に向かってバーズビークが発生してしまう。

【解決手段】 (a)半導体基板(10)の上に絶縁膜(14)を形成する。(b)絶縁膜の上に導電膜(15)を形成する。(c)導電膜及び絶縁膜をパターニングする。(d)工程(c)の後、半導体基板の少なくとも表層部を加熱する。工程(d)において、半導体基板の表層部の温度が第1の温度に到達するまでの少なくとも一部の第1の期間は、半導体基板が配置された空間に酸素ガスと不活性ガスとを供給しておき、第1の温度を超えた後は、酸素ガスの供給を停止させておく。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】従来の半導体装置の製造方法には、さらなる効率化が困難であるという課題がある。

【解決手段】第1基板41に設けられた第1半導体層51の表示面側に、平面視で第1半導体層51の一部に重なる第1導電パターン107を形成する工程と、第1導電パターンをマスクとして第1半導体層51に不純物を注入する第1注入工程と、前記第1注入工程の後に、第1導電パターン107の一部を除去して、第1導電パターン107と第1半導体層51とが平面視で重なる領域である第1重畳領域113aを縮小する縮小工程と、前記縮小工程の後に、ゲート電極部57をマスクとして第1半導体層51に前記不純物を注入する第2注入工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

キャパシタ及び薄膜トランジスタを有する基板、これを具備した平板ディスプレイ装置及び該キャパシタ及び薄膜トランジスタを有する基板の製造方法

【課題】製造工程を単純化させて製造コストを低減できるキャパシタ及び薄膜トランジスタを有する基板、これを具備した平板ディスプレイ装置及び該キャパシタ及び薄膜トランジスタを有する基板の製造方法を提供する。

【解決手段】(i)同一層に配された、半導体層、及びドーピングされた半導体層から形成されて導電性を有する第1キャパシタ電極、(ii)半導体層及び第1キャパシタ電極を覆う絶縁膜、(iii)絶縁膜上に配された、前記半導体層の一部領域に対応するゲート電極、及び第1キャパシタ電極に対応する第2キャパシタ電極を具備し、ゲート電極の厚さは、第2キャパシタ電極の厚さより厚いことを特徴とするキャパシタ及び薄膜トランジスタを有する基板、これを具備した平板ディスプレイ装置及び該キャパシタ及び薄膜トランジスタを有する基板の製造方法である。

(もっと読む)

半導体装置

【課題】同一基板上に複数のトランジスタを備え、各トランジスタの動作特性を劣化させることなく、各々に適切な閾値電圧を設定することのできる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、素子分離領域2により分離された第1および第2のトランジスタ領域10、20を有する半導体基板1と、第1および第2のトランジスタ領域10、20において、半導体基板上1に形成された不純物拡散抑制層12、22と、不純物拡散抑制層12、22上に形成されたエピタキシャル結晶層13、23と、を有し、不純物拡散抑制層22の厚さは、不純物拡散抑制層12の厚さよりも厚く、チャネル領域11に含まれる導電型不純物は、エピタキシャル結晶層13中の領域における濃度が、半導体基板1中の領域における濃度よりも低く、チャネル領域21に含まれる導電型不純物は、エピタキシャル結晶層23中の領域における濃度が、半導体基板1中の領域における濃度よりも低い。

(もっと読む)

半導体装置

【課題】MOSFETを安定して動作させるとともに、SBD領域における耐圧の低下を防ぐことのできる半導体装置を提供する。

【解決手段】半導体装置は、MOSFET領域10とSBD領域20とが配置されているn+型半導体基板1と、n+型半導体基板1上に設けられたn型エピタキシャル層2とを備える。MOSFET領域10は、p型ベース領域3に設けられ第1の不純物濃度を有するp+型拡散領域5を備える。SBD領域20は、n型エピタキシャル層2の上面に設けられ第2の不純物濃度を有するp型拡散領域21を備える。p型拡散領域21の有する第2の不純物濃度は、p+型拡散領域5の有する第1の不純物濃度よりも低い。

(もっと読む)

101 - 120 / 423

[ Back to top ]