Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

281 - 300 / 992

半導体装置

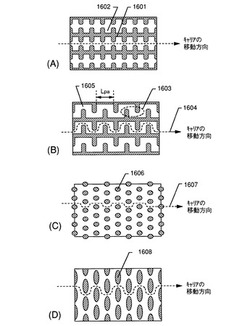

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスにおいてフォトレジスト構造等の追加工程を必要としない、非対称なDSS構造の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の側面に形成されたオフセットスペーサ13、23と、一方のオフセットスペーサ23の側面に形成されたゲート側壁27と、半導体基板2中のゲート絶縁膜21下に形成されたチャネル領域25と、半導体基板2内のチャネル領域25を挟む領域に形成され、チャネル領域25側に導電型不純物が偏析して形成されたエクステンション領域24aを有するソース・ドレイン領域24と、ソース・ドレイン領域24上にオフセットスペーサ13に接して形成されたシリサイド層16、及び、ゲート側壁27に接して形成されたシリサイド層26と、を有した半導体装置1とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属層にノッチ形状が形成されず、多結晶シリコン層から金属層へのシリコンの拡散を防止したMIPSゲート構造を有する半導体装置を提供する。

【解決手段】MIPSゲート構造を有する半導体装置の製造方法において、MIPSゲートの作製工程は、半導体基板上に、ゲート絶縁膜、メタル層、および多結晶シリコン層を順次堆積する工程と、多結晶シリコン層の上に形成したエッチングマスクを用いて、多結晶シリコン層をエッチングする工程と、メタル層を選択的にエッチングして、下方に向かって側壁がテーパ状に張り出したメタル層を残す工程と、多結晶シリコン層の側壁を含む平面から外方に突出したメッキ層のテーパ部を酸化して、酸化テーパ部とする酸化工程と、酸化テーパ部をエッチングで除去する除去工程とを含む。

(もっと読む)

電気的固体装置、電気光学装置、および電気的固体装置の製造方法

【課題】アルミニウム系の配線材料として用いた場合でも、十分な耐ヒロック性に備えるとともに、ドライエッチングを適用でき、さらに、レジストマスクを剥離する際に用いる剥離液によって、配線がエッチングされることのない電気的固体装置、電気光学装置、および電気的固体装置の製造方法を提供すること。

【解決手段】電気光学装置100において、素子基板10上に走査線3aなどの配線を形成するにあたって、ネオジウムを2atm%未満含有するアルミニウム合金膜を用いるとともに、走査線3aの上面および側面を酸化して表面保護膜31aを形成する。このため、走査線3aは、耐ヒロック性が高いとともに、表面保護膜31a、31eによってアルカリ性の剥離液から保護される。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属ゲート電極表面を低温で金属絶縁膜に変え、デバイスの、すなわち、回路・システムの信頼性を向上するデバイス構造、および、その製作方法を提供することを目的とする。

【解決手段】 本発明の半導体装置は、MOSデバイスのゲート電極を金属を用いて形成し、その側壁を金属絶縁膜に改質し、デバイスの信頼性を向上したことを特徴とする。また、良質な金属絶縁膜を、低温で形成したことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系結晶またはGe系結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、水素ガス雰囲気中において、圧力が第1の圧力であり、温度が第1の温度である条件下で、シリコン窒化物からなる部材を備えたSi系基板の前記部材に覆われていない領域の自然酸化膜および付着したシリコン窒化物を除去する工程と、水素ガス雰囲気中において、圧力を前記第1の圧力に保持したまま、温度を前記第1の温度から第2の温度に下げる工程と、水素ガス雰囲気中において、温度を前記第2の温度に保持したまま、圧力を前記第1の圧力から第2の圧力に下げる工程と、圧力を前記第2の圧力に下げた後、水素ガス、およびSiおよびGeのうちの少なくともいずれか1つを含む前駆体ガス雰囲気中において、前記Si系基板の表面にSiおよびGeのうちの少なくともいずれか1つを含む結晶をエピタキシャル成長させる工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルを含むゲート電極部を有する半導体装置において、ゲート電極部の側面に形成される膜の形成時およびその後の工程で、ゲート電極部に含まれるメタルの酸化を抑えることができる半導体装置を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、ゲート絶縁膜と、メタルゲートを有するゲート電極と、を含むゲート電極部と、ゲート電極部の下部のチャネル領域を挟んで半導体基板両側に形成されるソース/ドレイン領域と、ゲート電極部の側面に形成されるオフセットスペーサ膜と、を備え、オフセットスペーサ膜は、ゲート電極部の側面を連続的に被覆するホウ素と窒素を主成分とするBN膜と、BN膜上を連続的に被覆するシリコンと酸素を主成分とするシリコン酸化膜と、の積層膜からなる。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置

【課題】高温の酸化性雰囲気中でのSOD膜の改質を促進する。ライナー膜下部の素子や半導体基板が酸化されてダメージを受けることを防止する。

【解決手段】凹部と、凹部の内壁側面上に順に形成した、第1のライナー膜と、酸素原子を含有する第2のライナー膜と、凹部内に充填された絶縁領域と、を有し、第1のライナー膜は第2のライナー膜よりも耐酸化性が優れるものとした半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域7b及びp+型半導体領域8bを形成してから、半導体基板1上にNi1−xPtx合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域7b及びp+型半導体領域8bとを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層41aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で第1の熱処理を行ない、かつ、金属シリサイド層41a上に合金膜の未反応部分が残存するように、第1の熱処理を行なう。これにより、y>xとなる。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層41aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層41bを形成する。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域に高抵抗不純物領域(HRD

または低濃度不純物領域)を自己整合的に形成する方法を提供する。

【解決手段】ゲイト電極105上面にマスク106を残し、比較的低い電圧でポーラスな

第1の陽極酸化膜107をゲイト電極の側面に成長させる。この陽極酸化膜をマスクとし

てゲイト絶縁膜104’をエッチングする。必要に応じては比較的高い電圧でバリア型の

第2の陽極酸化膜108をゲイト電極の側面および上面に形成する。第1の陽極酸化膜を

選択的にエッチングする。不純物ドーピングをおこなうと、ゲイト電極の下部にはドーピ

ングされず、ゲイト電極に近い領域では、不純物濃度の低い高抵抗領域111,112と

なる。ゲイト電極から遠い領域では、不純物濃度の高い低抵抗領域110,113となる

。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電流損失を低減した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の金属材料は、結晶粒径が29μm以上の結晶粒を含む。また、導通部106の金属材料は、面積重み付けした平均結晶粒径が13μm以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性が高く良好な特性を有する半導体装置を提供する。

【解決手段】半導体基板101上に形成され、チャネル領域とチャネル領域を挟むソース/ドレイン・エクステンション領域108の少なくとも一部とを含むSiGe膜104aと、半導体基板の表面領域に形成され、ソース/ドレイン・エクステンション領域に接するソース/ドレイン・コンタクト領域110と、SiGe膜上に形成されたゲート絶縁膜105およびゲート電極106を有するゲート構造と、SiGe膜上に形成され、且つゲート構造の側面に形成された第1の側壁膜107と、SiGe膜上に形成され、且つ第1の側壁膜上に形成された第2の側壁膜109と、ソース/ドレイン・コンタクト領域上に形成され、且つSiGe膜の側面および第2の側壁膜上に形成された第3の側壁膜111と、ソース/ドレイン・コンタクト領域上に形成されたシリサイド膜112と、を備える。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート絶縁膜破壊が抑制された半導体装置を提供する。

【解決手段】ゲート電極給電用シリコンピラー5の表面を覆うゲート電極8と重なる位置に設けられたコンタクトホール13を備え、コンタクトホール13には、コンタクトホール13の底部から少なくともゲート電極8の上面よりも上方まで充填されたゲートリフトポリシリコン14と、ゲートリフトポリシリコン14上に配置されたゲートコンタクト15とが設けられていることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート間のピッチが狭い場合における短チャネル効果の劣化を抑制する。

【解決手段】基板上に、第1ゲートと、第1ゲートに隣接する第2ゲートを形成する工程、第1ゲートの側壁に第1サイドウォールを、第2ゲートの側壁に第2サイドウォールを形成する工程、第1ゲート、第1サイドウォール、第2ゲート、第2サイドウォールをマスクとして、基板に第1不純物の注入を行う工程、全面に絶縁膜を堆積した後、絶縁膜をエッチングして、第1サイドウォールの側面に第3サイドウォールを、第2サイドウォールの側面に第4サイドウォールを、第1ゲートと第2ゲートの間において第3サイドウォールと第4サイドウォールとが接触するように形成する工程、第1ゲート、第1及び第3サイドウォール、第2ゲート、第2及び第4サイドウォールをマスクとして、基板に第2不純物の注入を行う工程、第3及び第4サイドウォールを除去する工程、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】製品の歩留まりを向上することが可能な半導体装置を提供する。

【解決手段】半導体装置100は、埋め込み絶縁膜上に第1の方向に延びて形成され、シリコンまたはゲルマニウムの単結晶からなり、ソース・ドレイン拡散層となる部分にn型の不純物を含む第1のフィン層103aと、第1のフィン層の表面に選択的に形成され、n型の不純物を含みソース・ドレイン拡散層を構成する第1のエピタキシャル成長層112a,112bと、同様に、シリコンまたはゲルマニウムの単結晶からなり、ソース・ドレイン拡散層となる部分にp型の不純物を含む第2のフィン層103bと、第2のフィン層の表面に選択的に形成され、p型の不純物を含みソース・ドレイン拡散層を構成する第2のエピタキシャル成長層112c,112dと、第1のエピタキシャル成長層と第2のエピタキシャル成長層との間に形成された第1の分離絶縁膜107a,107bと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

281 - 300 / 992

[ Back to top ]