Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

321 - 340 / 992

半導体装置およびその製造方法

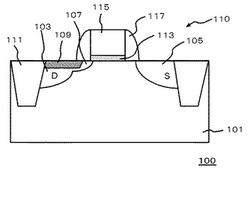

【課題】非対称トランジスタの接合リークを抑制する。

【解決手段】半導体装置100は、シリコン基板101の上部に設けられたゲート電極115と、ゲート電極115の異なる側方においてシリコン基板101に設けられた第一不純物拡散領域103および第二不純物拡散領域105とを有するMOSFET110を含む。MOSFET110は、第一不純物拡散領域103の上部にエクステンション領域107を有するとともに第二不純物拡散領域105の上部にエクステンション領域107を有さず、第一不純物拡散領域103上に第一シリサイド層109を有するとともに、ゲート電極115側端部の近傍において第二不純物拡散領域105上にシリサイド層を有しない。

(もっと読む)

半導体装置

【課題】ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】基板上の酸化珪素膜と、酸化珪素膜上のソース領域、ドレイン領域、ソース領域の上部に形成された第1のシリサイド、ドレイン領域の上部に形成された第2のシリサイド、及びチャネル形成領域を有する半導体層と、ゲイト絶縁膜と、多結晶珪素膜及び第3のシリサイドを有するゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに密着して形成された第1の金属配線と、第2のシリサイドに密着して形成された第2の金属配線と、を有し、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1乃至第3のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化された構造においても効果を発揮する歪みシリコン技術を適用した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板中の前記ゲート絶縁膜下に形成されたチャネル領域と、前記チャネル領域の両側に形成された第1の層、および前記第1の層の下層に位置し、ゲート電極中央側の端部の位置が前記第1の層よりも前記ゲート電極中央に近い第2の層を含み、前記チャネル領域に歪みを発生させる歪み付与層と、前記チャネル領域の両側に、少なくとも一部が前記歪み付与層と重なるように形成されたソース・ドレイン領域と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】FD−SOIの如き半導体層の厚みが薄い基板を使用してトランジスタを形成する際に、比較的簡便なプロセスでリーク電流の増加を回避しつつ、トランジスタの活性領域にシリサイド層を導入してトランジスタ寄生抵抗の低減を実現し得る半導体装置の製造方法を提供する。

【解決手段】SOI基板の半導体層の上にゲート酸化膜、ゲート電極材料を順次形成し、ゲート電極のパターニングを行う。ゲート電極の側壁部を覆う絶縁体からなるサイドウォールを形成する。半導体層のゲート電極を挟む位置にイオン注入してドレイン/ソース領域を形成する。サイドウォールを部分的にエッチングして、ゲート電極の側壁上部を露出させる。ドレイン/ソース領域とゲート電極の上面および露出した側壁部を覆うように金属膜を堆積させる。SOI基板に熱処理を施してゲート電極およびドレイン/ソース領域の表面にシリサイド層を形成する。

(もっと読む)

金属製のソースとドレインを有するトランジスタを製造するための方法

【課題】ソース・ドレイン領域のシリサイド化後に選択的エッチングを不要とする電界効果トランジスタ製造方法を提供する。

【解決手段】a)チャネル、ゲート及びハード・マスク118を含んでなる構造物を基板,誘電体層108の上に作るステップと、b)前記構造物とトランジスタの周囲領域を完全に覆う誘電体を形成するステップと、c)上記誘電体部分に、チャネルの側壁を露出させる二つの穴を形成するステップと、d)上記各穴の各壁部の上に第1の金属層132を蒸着するステップと、e)前記側壁をシリサイド化するステップと、f)前もってシリサイド化した部分に接してトランジスタのソース電極136とドレイン電極138を形成するように、第1の金属層の上に第2の金属層を蒸着するステップと、g)ハード・マスクに対しては阻止される、第2の金属層の化学機械研磨を行なうステップと、を有する製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域のゲート幅方向に与える応力を移動度が向上する方向に働かすとともに、ソース・ドレイン領域表面にシリサイド層を形成した際のリークを防止する。

【解決手段】半導体基板11に素子形成領域12を挟み、半導体基板11に埋め込まれるように素子分離領域13を形成する工程と、素子形成領域12上にそれを横切るようにダミーゲート52を形成する工程と、ダミーゲート52の両側の素子形成領域12にソース・ドレイン領域の接合位置が素子分離領域13の表面より深い位置にしてソース・ドレイン領域27、28を形成する工程と、半導体基板11上にダミーゲート52の表面を露出させて第1層間絶縁膜42を形成する工程と、ダミーゲート52を除去して溝29を形成する工程と、溝29内の素子分離領域13の上部を除去する工程と、溝29内の半導体基板11上にゲート絶縁膜21を介してゲート電極22を形成する工程とを備えている。

(もっと読む)

積層トレンチコンタクトを形成する方法および当該方法によって形成される構造

【解決手段】 マイクロ電子デバイスを形成する方法および対応して形成される構造を説明する。当該方法は、基板のソース/ドレインコンタクト上に配設されている第1のコンタクト金属と、第1のコンタクト金属の上面に配設されている第2のコンタクト金属とを含む構造を形成する段階を備えるとしてよい。第2のコンタクト金属は、基板上に配設されている金属ゲートの上面に配設されているILDの内部に配設されている。 (もっと読む)

半導体装置およびその製造方法

【課題】MISトランジスタを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面上に半導体層を積み上げて形成された一対のソース・ドレイン領域sdn,sdpと、その側壁を覆う側壁絶縁膜ISと、側壁絶縁膜ISに平面的に挟まれた位置のシリコン基板1の主面上に、ゲート絶縁膜IGを隔てて配置されたゲート電極GEと、ゲート電極GEの側方下部からソース・ドレイン領域sdn,sdpの側方下部に渡って形成されたエクステンション領域exn,expとを有する半導体装置であって、ソース・ドレイン領域sdn,sdpの側壁は順テーパ状の傾斜を有しており、側壁絶縁膜ISの側壁のうち、ゲート絶縁膜IGおよびゲート電極GEと隣り合う方の側壁は、順テーパ状の傾斜を有している。

(もっと読む)

半導体装置の製造方法

【課題】エッチングによって形成されるサイドウォールゲートのばらつきを抑制する技術を提供する。

【解決手段】第1の工程では、半導体基板の表面を露出する第1開口部を有する材料を形成する。第2の工程では、材料の上面と材料の側面と半導体基板の表面とに、第1絶縁膜と導電体膜とを順に形成する。第3の工程では、導電体膜表面に、第2開口部を有する第1導電体保護膜を形成し、第2開口部を第2絶縁膜で埋める。第4の工程では、第2絶縁膜をマスクに第1導電体保護膜を除去する。第5の工程では、第1導電体保護膜と第2絶縁膜とをマスクとして、導電体膜を除去する。第6の工程では、第2開口部の第2絶縁膜を除去した後、露出している導電体膜の表面に第2導電体保護膜を形成する。第7の工程では、第1導電体保護膜を除去した後、第2導電体保護膜をマスクにして、導電体を選択的に除去してゲートを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

半導体装置

【課題】同一基板上に複数のトランジスタを備え、各トランジスタの動作特性を劣化させることなく、各々に適切な閾値電圧を設定することのできる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、素子分離領域2により分離された第1および第2のトランジスタ領域10、20を有する半導体基板1と、第1および第2のトランジスタ領域10、20において、半導体基板上1に形成された不純物拡散抑制層12、22と、不純物拡散抑制層12、22上に形成されたエピタキシャル結晶層13、23と、を有し、不純物拡散抑制層22の厚さは、不純物拡散抑制層12の厚さよりも厚く、チャネル領域11に含まれる導電型不純物は、エピタキシャル結晶層13中の領域における濃度が、半導体基板1中の領域における濃度よりも低く、チャネル領域21に含まれる導電型不純物は、エピタキシャル結晶層23中の領域における濃度が、半導体基板1中の領域における濃度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース/ドレイン拡散層に形成されるシリサイド層のスパイクやコンタクトの突き抜けを抑制して、接合リークの発生を低減するとともに、シリサイド層を低抵抗化した半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10の上に形成されたトランジスタを有する。トランジスタのゲート電極は、ポリシリコン電極14とその上に形成されたシリサイド層32から構成される。さらに、低濃度ドーピング領域16、高濃度ドーピング領域からなるソース/ドレイン拡散層20、ソース/ドレイン拡散層20上のシリサイド層30を備える。シリサイド層30の表面は、半導体基板10の表面よりも上方に位置している。また、シリサイド層30はシリサイド化反応抑制金属を含み、シリサイド層30の表面から所定の深さに至る領域において、シリサイド層30の表面から基板側へ向かってシリサイド化反応抑制金属の濃度が高くなる濃度プロファイルを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線コンタクトのホールパターンと、ソース線コンタクトの溝パターンを同時に開口加工する際に、溝パターンにおける半導体基板の削れ量の増大を抑制する。

【解決手段】本発明の半導体装置は、半導体基板1上にメモリセルアレイを備え、各メモリセルにおけるホールパターンからなるビット線コンタクトをワード線方向に配列し、各メモリセルにおけるソース線コンタクトをワード線方向に延びる溝パターンから構成したものにおいて、半導体基板1の表面におけるソース線コンタクトを囲む選択ゲートトランジスタのゲート電極間の部位に、シリコン酸化膜12とRIEのバリヤ膜13とを積層して設け、半導体基板1の表面におけるビット線コンタクトを囲む選択ゲートトランジスタのゲート電極間の部位に、シリコン酸化膜12を設け、バリヤ膜が存在しないように構成した。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、ゲート構造の劣化を抑制した半導体装置の製造方法および半導体装置を提供することを目的とする。

【解決手段】本発明の一実施形態による半導体装置の製造方法は、Si基板1上にゲート絶縁膜3およびSiN4を積層して仮ゲートパターンを形成し、Si基板1に一部が埋め込まれたソース5およびドレイン5を仮ゲートパターンを挟んで離間して形成し、ソース5、ドレイン5、およびSiN4上にSiO24を形成し、SiO24を平坦化しSiN4を除去して形成されたゲート開口部の側面にSiN8を形成し、ゲート開口部にゲート電極材料9を埋め込むことを特徴とする。

(もっと読む)

二重仕事関数半導体デバイスの製造方法及びそのデバイス

【課題】金属ゲート電極を有する二重仕事関数半導体デバイスの製造方法を提供する。

【解決手段】該製造方法は、第1領域101及び第2領域102を有する基板100を設けること、第1領域に第1半導体トランジスタ107を作製すること、第2領域に第2半導体トランジスタ108を作製すること、第1サーマルバジェットを第1半導体トランジスタに備わる少なくとも第1ゲート誘電体キャッピング層114aに作用し、第2サーマルバジェットを第2半導体トランジスタに備わる少なくとも第2ゲート誘電体キャッピング層114bに作用すること、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】接合深さが深くなるが抑制され、低抵抗化された低濃度不純物領域を備えた半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、第1のゲート電極103a、第1の不純物を含む第1の不純物領域106a、並びに第1のゲート電極の側面上に形成された第1の内側サイドウォールスペーサ107a及び第1の外側サイドウォールスペーサ109aを有する内部トランジスタと、第2のゲート電極103b、第1の不純物と同一導電型の第2の不純物を含む第2の不純物領域106b、並びに第2のゲート電極103bの側面上に形成された第2の内側サイドウォールスペーサ107b及び第2の外側サイドウォールスペーサ109bを有する入出力トランジスタとを備えている。第2の内側サイドウォールスペーサ107bは、第2の外側サイドウォールスペーサ109bとの界面領域に第2の不純物を含有している。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

321 - 340 / 992

[ Back to top ]