Fターム[4M104FF02]の内容

Fターム[4M104FF02]に分類される特許

101 - 120 / 461

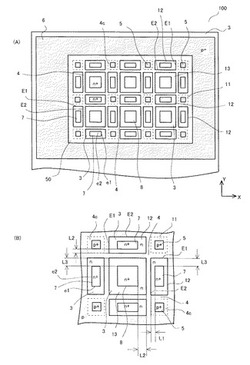

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体チップの割れや欠けを防止し、デバイス特性を向上することができる半導体装置および半導体装置の製造方法を提供すること。

【解決手段】半導体チップ10の素子端部の側面には、分離層3が設けられている。また、半導体チップ10の素子端部には、凹部4によってひさし部5が形成されている。コレクタ層6は、半導体チップ10の裏面に設けられ、凹部4の側壁22および底面23に延在し、分離層3に接続されている。コレクタ層6の表面全体には、コレクタ電極7が設けられている。凹部4の側壁22上のコレクタ電極7は、最表面の電極膜の厚さが0.05μm以下となっている。半導体チップ10の裏面に設けられたコレクタ電極7は、はんだ層11を介して、絶縁基板12上に接合されている。はんだ層11は、半導体チップ10の裏面の平坦部21に設けられたコレクタ電極7を覆うように設けられている。

(もっと読む)

p型拡散層形成組成物、並びに、太陽電池セルおよびその製造方法

【課題】結晶シリコン基板を用いた太陽電池セルの製造工程において、シリコン基板中の内部応力、基板の反りの発生を抑制しつつp型拡散層および裏面電極を形成することが可能なp型拡散層形成組成物、および、これを用いて形成された太陽電池セルの提供を提供する。

【解決手段】p型拡散層形成組成物を、金属粒子と、アクセプタ元素を含むガラス粒子と、樹脂と、溶剤と、を含んで構成する。また、半導体基板上に該p型拡散層形成組成物を塗布した後、熱処理することで形成されたp型拡散層および電極を備える太陽電池セルである。

(もっと読む)

半導体装置

【課題】小型化を実現し、かつ耐圧の高い半導体装置を提供すること。

【解決手段】活性領域10と分離領域30との間に設けられた耐圧構造部20は、順方向耐圧構造領域40と逆方向耐圧構造領域50とからなる。順方向耐圧構造領域40および逆方向耐圧構造領域50には、複数のフィールドリミッティングリング(FLR)41,51と、複数のフィールドプレート(FP)44,54が設けられている。複数のFP44のうち、最も逆方向耐圧構造領域50のFP(第1順方向FP)45は、分離領域30側に張り出すように設けられている。複数のFP54のうち、最も順方向耐圧構造領域40のFP(第1逆方向FP)55は、活性領域10側に張り出すように設けられている。順方向の電圧印加時、第1逆方向FP55は、分離領域30から伸びる空乏層を止める。逆方向の電圧印加時、第1順方向FP45は、活性領域10から伸びる空乏層を止める。

(もっと読む)

半導体装置、貼り合せ基板およびそれらの製造方法

【課題】低コストで高品質の半導体装置、および当該半導体装置の製造に用いる貼り合せ基板、およびこれらの製造方法を提供する。

【解決手段】半導体素子の製造方法は、単結晶半導体部材を準備する工程(S10)と、支持基材を準備する工程(S20)と、支持基材と単結晶半導体部材とを、炭素を含む接合層を介して接合する工程(S30)と、単結晶半導体部材の表面にエピタキシャル層を形成する工程(S40)と、エピタキシャル層を利用して半導体素子を形成する工程(S50)と、半導体素子を形成する工程(S50)の後、接合層を酸化することにより分解して支持基材から単結晶半導体部材を分離する工程(S60)と、支持基材から分離された単結晶半導体部材を分割する工程(S80)とを備える。

(もっと読む)

半導体デバイスとその製造方法

【課題】裏面電極/半導体基板の間のエネルギー障壁が低く、半導体デバイスのオン抵抗が低減され、裏面電極の露出面の耐腐食性が良好で、かつ、裏面電極と半導体基板との密着性が良好で、裏面電極の材料コストを抑えることが可能な半導体デバイスを提供する。

【解決手段】裏面電極300は、Si基板101側から順にTiシリサイド層301とTi層302とNi層303とAg層304とAu層305とが積層された積層構造、又はSi基板101側から順にTiシリサイド層301とNi層303とAg層304とAu層305とが積層された積層構造を有する。裏面電極300は、Si基板101にTi層302とNi層303とAg層304とを順次成膜した後にシンター処理を行ってTiシリサイド層301を生成し、その後Au層305を成膜して製造されたものであることが好ましい。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】簡便なプロセスの採用が可能で、過電流耐性の高い構成を有した炭化珪素半導体装置を得る。

【解決手段】中央のドット状の半導体領域5は、輪郭部分が太線で示されているが、当該太線で示されるリング状領域に、ドット状の半導体領域5より深い位置にp型不純物が達する電流制限部5a(大深度部)が形成されている。ドット状の半導体領域5のp型不純物の到達深さが0.2〜0.4μmであるのに対して、リング状の電流制限部5aでは、ドリフト層である半導体層1の厚さの3分の1以下となる深さに設定される。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

SiC半導体素子の製造方法

【課題】薄板化に伴うSiC基板の反りを修正するSiC半導体素子の製造方法の提供を目的とする。

【解決手段】本発明の半導体素子の製造方法は、(a)表面側に素子活性領域が形成されたSiC基板1を準備する工程と、(b)SiC基板1の表面を平坦面に固定し、裏面を研削する工程と、(c)SiC基板1の表面を平坦面に固定したまま、研削によるSiC基板の反りを相殺する応力を付与する内部応力層を、SiC基板内部に形成する工程とを備える。

(もっと読む)

半導体装置

【課題】IGBTにおいて、P型コレクタ層におけるキャリア濃度の変化を抑制し、オン電圧のばらつきを低減可能な技術を提供することを目的とする。

【解決手段】半導体装置は、表面側にMOSFET構造1が形成されたN型半導体基板2と、N型半導体基板2の裏面に形成されたP型コレクタ層4とを備える。そして、P型コレクタ層4上にストライプ状に互いに離間して形成された、AlとSiとのAl合金からなるAlSi電極7aを含む積層構造の裏面電極7を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、簡素な製造工程でありながら、ボイドを発生させずにトランジスタセルの高密度化を実現する半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体層60にトレンチ型のゲート90が形成され、該ゲート90の両側に拡散層50が形成されたトランジスタセルを複数含むセル部61と、該セル部61を囲むガードリング部62とを有する半導体装置の製造方法であって、

前記ゲート90及び前記拡散層50が形成された前記半導体層60の表面に、層間絶縁膜120を形成する工程と、

前記セル部61に形成された前記層間絶縁膜120を、エッチバックにより薄膜化する工程と、

前記層間絶縁膜120の前記拡散層50上の位置に、孔状又は溝状のコンタクト部130を形成する工程と、

前記層間絶縁膜120上に、金属膜140を形成する工程と、を含むことを特徴とする。

(もっと読む)

ショットキーバリアダイオード

【課題】順方向サージ耐圧と順方向降下電圧VFとのトレードオフ特性を改善することが可能で、かつ、逆方向漏れ電流IRが増加してしまうことのないショットキーバリアダイオードを提供する。

【解決手段】第1主面及び当該第1主面の反対面である第2主面を有し、炭化珪素からなるn型の半導体基体110と、半導体基体110における第1主面上に形成されたバリアメタル層118と、半導体基体110における第1主面側の表面に部分的に形成され、高濃度のp型不純物を含有する小数キャリア注入層128と、小数キャリア注入層128の直下にのみカーボンが導入されたカーボン導入層132とを備えるショットキーバリアダイオード100。

(もっと読む)

電力半導体装置およびその製造方法

【課題】本発明は、コレクタ電極に含まれるアルミニウムがコレクタ層へ拡散することを防止でき、かつ安定した電気特性を有する電力半導体装置およびその製造方法を提供することを目的とする。

【解決手段】基板の表面に形成されたエミッタおよびゲートと、該基板の裏面に形成されたコレクタ層と、該コレクタ層の該基板と接する面と反対の面に形成された酸化膜と、該酸化膜の該コレクタ層と接する面と反対の面に形成された、アルミニウムを含むコレクタ電極と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】スイッチング素子による高温の悪影響を回避して、誤点弧を防止する回路をスイッチング素子と同一の基板上に配置した半導体装置を提供する。

【解決手段】基板5上の導電体パターン51,52上にNチャネル型のMOSFET10、及びNチャネル型で半導体材料が炭化珪素からなるJFET30を各別に近接して配置し、MOSFET10のゲート電極13とJFET30のドレイン電極31とをリード線61で接続する。MOSFET10をオン/オフに制御する外部からの駆動信号がJFET30のソース電極32及びドレイン電極31間を伝播するときに、ソース電極32及びゲート電極33間のゲート電圧の低/高に応じてJFET30のチャネル抵抗を大/小に変更することにより、MOSFET10のドレイン電極11及びソース電極12間のスイッチング波形の前縁を、後縁に比較して緩やかな傾斜にする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置のオン抵抗をより低減させる。

【解決手段】第1導電型の半導体層と、前記半導体層の上側に、前記半導体層の主面に対して平行な方向に沿って周期的に配置された第1導電型の半導体ピラー領域と、前記第1導電型の半導体ピラー領域の表面に選択的に設けられた第2導電型のベース領域と、前記第2導電型のベース領域の表面に選択的に設けられたソース領域と、前記第1導電型の半導体ピラー領域間に設けられ、前記ベース領域の表面にまで達する第2導電型の半導体ピラー領域と、前記ソース領域に電気的に接続された第1の主電極と、前記半導体層の下側に設けられ、前記半導体層に電気的に接続された第2の主電極と、前記第1の主電極と前記第2の主電極との間の通電を制御する制御電極と、を備える。

(もっと読む)

光電変換装置用基板、およびそれを用いた光電変換装置、ならびにそれらの製造方法

【課題】微小凹部を形成することにより、光電変換装置の光電変換効率および安定性を向上させる。

【解決手段】ガラス基板2と、ガラス基板2の主表面の少なくとも一部を覆い、基板側とは反対側の表面に凹凸形状を有する透明導電膜3とを備えている。凹凸形状は、最大高さが50nm以上1200nm以下である凸部を有している。凸部の表面上に、局部山頂の間隔が2nm以上25nm以下である微小凹部が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

101 - 120 / 461

[ Back to top ]