Fターム[4M104FF02]の内容

Fターム[4M104FF02]に分類される特許

161 - 180 / 461

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】不純物を活性化又は拡散させる熱処理後の半導体基板の裏面への自然酸化膜の成長を抑制する。

【解決手段】第1導電型の低不純物濃度の半導体基板(例えば、n−型半導体基板1)に裏面側から第1導電型の不純物をドープした後で、半導体基板の裏面に裏面電極8を形成する。その後、ドープされた不純物を熱処理により活性化又は拡散させる。熱処理後の段階では既に裏面電極8が形成されているので、熱処理後において、半導体基板の裏面への自然酸化膜の成長を抑制することができる。

(もっと読む)

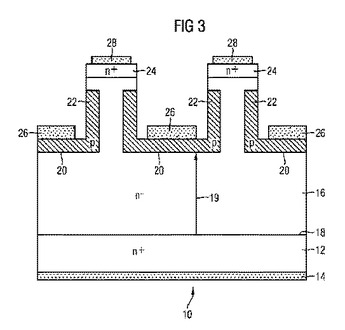

TJBSダイオードが組み込まれた電界効果トランジスタ

少なくとも1つのMOS電界効果トランジスタとダイオードとを含んでいる半導体デバイスであって、前記ダイオードはトレンチジャンクションバリアショットキーダイオード(TJBS)であり、モノリシックに組み込まれている構造体としてMOS電界効果トランジスタとトレンチジャンクションバリアショットキーダイオード(TJBS)を備えた構造が実現される。前記MOS電界効果トランジスタおよび前記トレンチジャンクションバリアショットキーダイオード(TJBS)のアバランシェ電圧は、前記MOS電界効果トランジスタがアバランシェにおいて動作可能であるように選択されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】過電圧に伴う破壊を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、互いに並列に接続され、ゲート電極10、ソース電極9及びドレイン電極15を備えた複数の縦型トランジスタ32と、前記複数の縦型トランジスタ32を個別に取り囲むダイオード31と、が設けられている。前記ソース電極9に前記ダイオード31のアノード11が接続され、前記ドレイン電極15に前記ダイオードのカソード1が接続されている。

(もっと読む)

半導体装置

【課題】オン電圧を低減した半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、前記第1の半導体層の上に設けられた第2導電型の第2の半導体層と、前記第1の半導体層の上に前記第2の半導体層と接して設けられた前記第1の半導体層よりも不純物濃度の高い第1導電型の第3の半導体層と、前記第2の半導体層に接続された第1の金属層と、前記第3の半導体層に接続され前記第1の金属層とは異なる金属からなる第2の金属層と、を有する第1の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】半導体装置において耐電荷性を向上させること。

【解決手段】素子活性部1とn+ドレイン領域2との間に第1の並列pn層12が設けられている。素子周縁部3に、第1の並列pn層12よりも繰り返しピッチの狭い第2の並列pn層15が設けられている。第2の並列pn層15と第1の主面との間にn-表面領域18が設けられている。n-表面領域18の第1の主面側に複数のp型ガードリング領域19,20,21が互いに離れて設けられている。複数のp型ガードリング領域19,20,21のうちの最も外側に位置するp型ガードリング領域19に、フィールドプレート電極23が電気的に接続する。素子周縁部3のp型最外周領域26にチャネルストッパー電極24が電気的に接続する。

(もっと読む)

半導体デバイス及びその形成方法

【課題】応力ライナによるコンタクト形成の問題が起きない、相補型金属酸化膜半導体(CMOS)デバイスの製造方法を提供する。

【解決手段】シリコン基板層上の二酸化シリコン層102と、凹んだソース/ドレイン・トレンチを有する相補型金属酸化膜半導体(CMOS)デバイスを準備し、凹んだソース/ドレイン・トレンチ内に窒化物応力ライナ104を堆積し、その上に酸化物層106を堆積する。CMOSデバイスをハンドリング・ウェハ上に置きシリコン基板層を除去し二酸化シリコン層102をエッチングしてソース/ドレイン領域170の一部に当接する開口部を形成しコンタクト180を形成する。

(もっと読む)

単極半導体部品と半導体装置の製造方法

本発明は、ドリフト層(16)を有する単極半導体部品の製造方法であって、少なくとも1つの広いバンドギャップ材料を含むドリフト層(16)の材料のエピタキシャル析出を手段として、ドリフト層(16)の成長方向(19)に沿って連続的に低下する電荷キャリアドーピング(n)の濃度を有するドリフト層(16)を形成する工程を含む方法に関する。エピタキシャル析出により形成されるドリフト層(16)に炭化ケイ素を使用することにより、下流工程におけるドープ材原子の拡散による電荷キャリアドーピング(n)の連続的に低下する濃度のその後の変化を抑制する。製造方法は特に、単純なおよび/または費用効果的なやり方で、ドリフト層(16)を含む単極半導体部品であって比較的低い順方向損失と比較的高い逆バイアス電圧との有利な比を有する単極半導体部品を実装するために使用されることができる。単極半導体部品は能動半導体部品または受動半導体部品であることができる。本発明はさらに、半導体装置(10)に関する。  (もっと読む)

(もっと読む)

半導体装置

【課題】薄い半導体チップの両側の表面に多数の電極が形成された両面マルチ電極チップが好適に実装されてなる半導体装置を提供する。

【解決手段】半導体チップ21の両側の表面S1,S2にそれぞれ複数の電極D1,D2が形成された両面マルチ電極チップ11が実装されてなる半導体装置であって、両面マルチ電極チップ11が、外部に露出しないように多層配線基板60に埋め込まれ、両面マルチ電極チップ11の複数の電極D1,D2が、前記多層配線基板の配線層H3,H1に接続されてなる半導体装置100とする。

(もっと読む)

酸化物薄膜トランジスタ及びその製造方法

【課題】素子の劣化及び均一度の低下を防止する酸化物薄膜トランジスタ及びその製造方法を提供する。

【解決手段】酸化物薄膜トランジスタの製造方法は、基板110上にゲート電極121を形成する段階と、基板110上にゲート絶縁膜115を形成する段階と、ゲート絶縁膜115上にチャネル領域の側面にテーパを有する1次アクティブ層124aを形成し、1次アクティブ層124a上にソース/ドレイン電極を形成する段階と、ソース/ドレイン電極122、123の上部に、非晶質酸化亜鉛系半導体からなる2次アクティブ層124bを、1次アクティブ層124aのテーパと接触するように形成する段階とを含み、1次アクティブ層124aは、ソース/ドレイン電極122、123のウェットエッチング中に低い選択比でエッチングされることにより、側面にテーパが形成される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】凹凸の大きいステップバンチングに対しても平坦化可能で、かつ平坦化にあたりCMP研磨などの研磨工程を必要としない炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】炭化珪素基板の表面上に、活性領域となり表面にステップバンチングが生じやすいC/Si比を有する第1の炭化珪素層を形成する第1工程と、前記第1の炭化珪素層の表面上に、表面が平坦となるC/Si比を有する第2の炭化珪素層を形成する第2工程と、前記第2の炭化珪素層をエッチング除去する第3工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体デバイスとその製造方法

【課題】本発明は、エミッタ電極などの電極とリードフレームの接続に伴う接続抵抗を低減した信頼性の高い半導体デバイスとその製造方法を提供することを目的とする。

【解決手段】半導体層の表面に形成された電極と、該電極上に形成され、リードフレームとはんだ付け可能な付加電極と、該付加電極とともに該電極を覆い、かつ、該半導体層を覆うように該付加電極の表面に開口部を設けて形成されたパッシベーション膜とを備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】製造コストを上げることなく、かつ、貫通穴が原因となって生じる歩留を向上させ、薄膜デバイスに適用可能な半導体装置を提供する。

【解決手段】半導体装置100は、表面から裏面までを貫通する貫通穴を有するアンドープGaN層102と、アンドープGaN層102の表面上および貫通穴内に形成された、導電性を有するアルミニウム層103とを備え、アルミニウム層103における貫通穴内に形成された領域のうち、裏面側に露出している絶縁領域106は、化学変化により絶縁化されている。

(もっと読む)

トレンチゲートパワー半導体装置及びその製造方法

【課題】従来のトレンチゲートパワー半導体装置よりも信頼性が高く、かつ、ESD耐量も高いトレンチゲートパワー半導体装置を提供する。

【解決手段】平面的にみて所定の第1ピッチaでストライプ状に配列された複数本の溝120,122を備えるトレンチゲートパワー半導体装置100であって、複数本の溝120,122のうち最も外側の溝122においては、当該溝122が延在する第1方向(y方向)に垂直な第2方向(x方向)に沿ってかつ当該溝122の外側に向かって突出する複数本の補助溝124が、第1ピッチaの0.5倍以上、1.5倍以下の値に設定された所定の第2ピッチbで第1方向(y方向)に沿って形成されているトレンチゲートパワー半導体装置。

(もっと読む)

薄膜トランジスタおよび画像表示装置

【課題】本発明は、ゲート電極とソース電極間の絶縁性を向上させ、ゲート電極とソース電極間のリーク電流を低減させることにより、確実に動作する薄膜トランジスタおよび画像表示装置を提供する。

【解決手段】基板と、前記基板上に形成されたゲート電極と、ゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層および前記ゲート絶縁膜上に形成され、前記半導体層の直上に離間して形成された第1の開口部および第2の開口部を有する保護膜と、前記保護膜上に形成され、前記保護膜の第1の開口部で前記半導体層と電気的に接続されたソース電極と、前記保護膜上に形成され、前記保護膜の第2の開口部で前記半導体層と電気的に接続されたドレイン電極を備える薄膜トランジスタにすることにより、ゲート電極とソース電極との間の絶縁膜の膜厚が実質的に増すこととなり、絶縁性を向上させることができる。

(もっと読む)

逆耐圧を有する縦型窒化ガリウム半導体装置

【課題】逆阻止能力を有し、低オン抵抗で高速スイッチング特性を有する素子を提供すること。

【解決手段】シリコン基板101と、シリコン基板101上に形成されたバッファ層102,103と、バッファ層102、103上に形成された窒化ガリウム半導体層104と、シリコン基板101の裏面からシリコン基板101ならびにバッファ層102、103を貫通して窒化ガリウム半導体層104に達する深さで形成されたトレンチ溝112と、このトレンチ溝112の中に形成された金属膜113と、を備え、金属膜113と窒化ガリウム半導体層104とがショットキー接合を形成する逆耐圧を有する窒化ガリウム半導体装置とする。

(もっと読む)

161 - 180 / 461

[ Back to top ]