Fターム[4M104FF02]の内容

Fターム[4M104FF02]に分類される特許

81 - 100 / 461

半導体装置及びその製造方法

【課題】微細化されたN+型ソース層とソース電極のコンタクト抵抗が低減されたパワーMOSトランジスタの実現を図る。

【解決手段】N型ドリフト層2の表面にP型ボディ層6を形成し、該P型ボディ層6の表面にN+型ソース層7を形成する。N+型ソース層7上を被覆する層間絶縁膜8に第1のコンタクトホール9を形成し、N+型ソース層7の一部を露出する。第1のコンタクトホール9の底面に露出したN+型ソース層7の表面からP型ボディ層6内まで第2のコンタクトホール10を形成する。第2のコンタクトホール10の底面に露出したP型ボディ層6の表面にP+型コンタクト層11を形成する。第1のコンタクトホール9の底面にフォトリソグラフィ工程のマスク合わせ精度のばらつき幅より小さい幅のN+型層7aを形成し、第1、第2のコンタクトホール9、10内をタングステン層12等で埋設する。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置

【課題】薬液に関する問題を低減するとともに、洗浄効果を高めるSiC半導体装置の製造方法およびSiC半導体装置の製造装置を提供する。

【解決手段】SiC半導体装置の製造方法は、SiCの表面に酸化膜を形成する工程(ステップS3)と、酸化膜を除去する工程(ステップS5)とを備え、酸化膜を形成する工程(ステップS3)では、オゾンガスを用いる。酸化膜を除去する工程(ステップS5)では、ハロゲンプラズマまたは水素プラズマを用いることが好ましい、

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

Mo系スパッタリングターゲットおよびその製造方法ならびにこれを用いたCIGS系薄膜太陽電池

【課題】 スパッタリング中の異常放電を抑制できる、アルカリ金属化合物が微細に分散

したMo系スパッタリングターゲットおよびその製造方法を提供する。

【解決手段】 本発明は、KとNbとの複合酸化物でなる粉末とMo粉末との焼結体であ

って、前記複合酸化物を0.4〜9.0質量%含有し、Mo母相中に内接円直径が20μ

m以下の凝固した前記複合酸化物が分散するMo系スパッタリングターゲットである。ま

た、本発明のMo系スパッタリングターゲットは、加圧容器に充填し、前記複合酸化物の

溶融温度以上、Moの溶融温度以下で加圧焼結することにより得られる。

(もっと読む)

半導体装置

【課題】スイッチング損失を低減した半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、ベース層と、ベース層上に設けられた第2導電形半導体層と、第2導電形半導体層の表面からベース層側に向けて延び、ベース層には達しない複数の第1のトレンチの内壁に設けられた第1の絶縁膜と、第1の絶縁膜を介して第1のトレンチ内に設けられると共に第2導電形半導体層の表面に接する第1の電極とを備えている。第2導電形半導体層は、第1のトレンチで挟まれた第1の第2導電形領域と、第1の第2導電形領域とベース層との間および第1のトレンチの底部とベース層との間に設けられ、第1の第2導電形領域よりも第2導電形不純物量が少ない第2の第2導電形領域とを有する。

(もっと読む)

半導体上からホットメルトエッチングレジストを剥離する改良された方法

【課題】シート抵抗率の増大およびアルミニウム電極の腐蝕を抑制する剥離剤配合物を提供する。

【解決手段】ホットメルトエッチングレジストが、半導体ウェハ上の反射防止コーティングもしくは選択的エミッタに選択的に適用される。無機酸含有エッチング剤を用いて、反射防止コーティングおよび選択的エミッタの露出部分がエッチング除去されて、半導体基体を露出させる。このホットメルトエッチングレジストは次いで、半導体の電気的一体性を悪化させないアルカリ剥離剤を用いて半導体から剥離される。次いで、露出した半導体は金属化されて、電流トラックを形成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】逆方向耐圧を向上させることができる半導体装置を提供する。

【解決手段】一導電型の半導体層100と、絶縁体層130と、絶縁体層中に設けられた半導体層210と、半導体層210に設けられた能動素子20と、半導体層100の前記一主面201に設けられた他の導電型の半導体領域112と、半導体領域112内に設けられた他の導電型であって半導体領域112よりも高不純物濃度の半導体領域114と、絶縁体層130に設けられたスルーホール144内に半導体領域144に接続して設けられた導電体154と、絶縁体層130上または中に設けられた導電体214であって、導電体154の周囲に設けられ、外側端部が半導体領域114よりも外側にある導電体214と、導電体154と導電体214とを接続して設けられた導電体192と、半導体層100に接続して設けられた導電体152,120と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】IGBT等においては、ドリフト領域やフィールドストップ領域における少数キャリアのライフタイムを制御して、スイッチング特性を改善するため、ウエハへの電子線照射が行われている。この電子線照射によって、デバイスの閾値電圧がシフトするため、電子線照射後に水素アニールを施すことにより、閾値電圧の回復を図っている。しかし、ボンディングダメージ等を低減するため、デバイス表面のモリブデン系バリアメタルをTiW系バリアメタルに変更すると、水素アニールによる閾値電圧の回復率が低下する問題が発生した。

【解決手段】本願発明はシリコン系半導体ウエハのデバイス主面側にパワー系絶縁ゲート型トランジスタの主要部を形成する半導体装置の製造方法において、デバイス主面上にTiW系のバリアメタルをスパッタリングにより形成するに際して、TiWターゲットのチタン濃度を、8重量%以下で、且つ、2重量%以上とするものである。

(もっと読む)

半導体装置の製造方法

【課題】非酸化雰囲気下でなくても、良好なオーミック電極を形成可能な技術を提供する。

【解決手段】オーミック電極を有する半導体装置の製造方法であって、半導体基板50上に金属層30eを形成する工程と、金属層30e上に透過膜30fを形成する工程と、透過膜30fを通して金属層30eに電磁波を照射して、金属層30eを加熱する工程と、透過膜30fを除去する工程を有する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体整流装置

【課題】十分なサージ電流耐性を有し、かつ、信頼性の向上するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】第1導電型の第1のワイドバンドギャップ半導体領域16と、第1の半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域18とを備えている。また、少なくとも一部が第2の半導体領域に接続され、第1の半導体領域に挟まれて形成され、第2の半導体領域より幅の狭い、複数の第2導電型の第3のワイドバンドギャップ半導体領域32を備えている。ここで、第3の半導体領域の長手方向を第1導電型の半導体層の表面に投影した方向が、第1導電型の半導体層の表面から裏面に向かう方向に対し、90±30度の角度を有している。また、第3の半導体領域の間隔が、第1導電型のワイドバンドギャップ半導体層の厚さをdとする場合に2d×tan18°以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイオードと電極材料とのコンタクト抵抗を低減した半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、シリコンを含むダイオードと、前記ダイオードに対して積層された金属層及び可変抵抗膜と、前記ダイオードと前記金属層との間に設けられた、チタンとシリコンと窒素とを含む層と、を備えた。前記チタンと前記シリコンと前記窒素とを含む前記層は、前記窒素よりも前記チタンまたはチタンシリサイドを多く含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】MPS構造又はJBS構造を有し、低い順方向降下電圧VF及び高い逆方向耐圧VRを両立させることが可能で、さらには、逆回復時間trrが短く、かつ、逆方向リーク電流IRが低い半導体装置を提供する。

【解決手段】n−型半導体層114と、n−型半導体層114の第1主面側表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114の第1主面側表面上におけるp+型拡散領域120が形成されていない領域に形成され、n−型半導体層114との間でショットキー接合を形成するバリアメタル層130と、バリアメタル層130を覆うようにn−型半導体層114の第1主面側全面に形成され、p+型拡散領域120との間でオーミック接合を形成するオーミックメタル層140と、p+型拡散領域120の直下にのみライフタイムキラーが導入された局所ライフタイム制御領域150とを備える半導体装置100。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置が有する保護膜や層間絶縁膜にかかる電界を抑制し、半導体装置の絶縁破壊耐圧を向上する。

【解決手段】半導体装置は、基板1と、基板の上方に形成されたキャリア走行層4と、キャリア走行層の上に形成された化合物半導体層5,6,7と、化合物半導体層の上に形成されたソース電極10と、基板の裏面から基板を貫通し、キャリア走行層の内部まで形成された第1の溝12と、第1の溝の内部に形成されたドレイン電極14と、ソース電極10と第1の溝12との間に位置し、化合物半導体層の上に形成されたゲート電極11と、ソース電極の斜め下方であってソース電極と第1の溝との間に位置し、基板の裏面から基板を貫通し、キャリア走行層4の内部まで形成された第2の溝13と、を備える。

(もっと読む)

半導体装置およびその製法

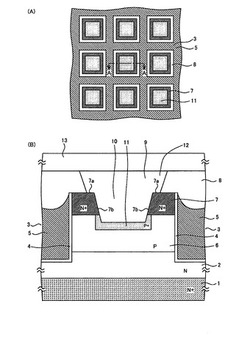

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

81 - 100 / 461

[ Back to top ]