Fターム[4M104FF02]の内容

Fターム[4M104FF02]に分類される特許

21 - 40 / 461

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】エピ基板を用いずに形成可能な半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は,シリコン基板と,半導体素子と,高濃度層と,ニッケルシリサイド層と,金属層と,を具備する。シリコン基板は,互いに対向する第1,第2の主面を有し,第1導電型の不純物を第1の濃度含有する。MOS型半導体構造は,第1の主面側に配置される。高濃度層は,第2の主面側に配置され,前記不純物を前記第1の濃度より大きい第2の濃度含有する。ニッケルシリサイド層は,前記高濃度層上に配置され,硫黄又はアンチモンを含む。金属層は,ニッケルシリサイド層上に配置される。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の十分な低減を可能とする半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法は、少なくとも一方の主面を含む領域が単結晶炭化珪素からなる基板を準備する工程と、一方の主面上に活性層23を形成する工程と、基板の前記一方の主面とは反対側の他方の主面を含む領域を研削する工程と、他方の主面を含む領域を研削する工程において形成されたダメージ層22Cを除去する工程と、ダメージ層22Cが除去されることにより露出した主面に接触するように裏面電極を形成する工程とを備え、一方の主面は{0001}面に対するオフ角が50°以上65°以下となっている。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

ジャンクションバリアショットキーダイオード

【課題】ジャンクションバリアショットキーダイオードの耐圧を低下させることなく、リーク電流の低減とオン電流の増大を両立したダイオードを提供する。

【解決手段】本発明は、ジャンクションバリアショットキーダイオードにおいて、pn接合を形成するp型領域の側部に存在するpn接合の傾きが、当該p型領域の底部に存在するpn接合の傾きより急峻である。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】炭化珪素半導体装置の製造において、上面が平坦な終端構造とリセス状のアライメントマークとを少ないマスク数で形成すると共に、アライメントマークのリセスの深さを最適化する。

【解決手段】ハーフトーン露光法を用いて、SiCエピタキシャル層2に達する第1の開口部12aとSiCエピタキシャル層2に達しない第2の開口部とを有するレジストパターン11を、SiCエピタキシャル層2上に形成する。エッチングにより、第1の開口部12aに露出したSiCエピタキシャル層2にリセス状のアライメントマーク9を形成すると同時に第2の開口部12bをSiCエピタキシャル層2に到達させる。その後、イオン注入により、第2の開口部12bに露出したSiCエピタキシャル層2に、終端領域8を形成する。

(もっと読む)

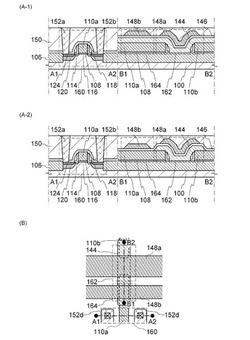

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

太陽電池及びその製造方法

【課題】改善された光電変換効率を有する太陽電池を提供する。

【解決手段】太陽電池1は、光電変換部10と、第1の電極21と、第2の電極22とを備える。第1の電極21は、光電変換部10の一主面10aの上に配されている、第2の電極22は、光電変換部10の他主面10bの上に、第1の電極21よりも小面積に配されている。第1の電極21は、第1の第1電極導電層21aと、第2の第1電極導電層21cとを含む。第1の第1電極導電層21aは、光電変換部10の一主面10aの上に配されている。第2の第1電極導電層21cは、第1の第1電極導電層21aの上に配されている。第1の第1電極導電層21aは、第2の第1電極導電層21cよりも高い光反射率を有する。第2の第1電極導電層21cは、第1の第1電極導電層21aよりも低い電気抵抗を有する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

光電変換装置

【課題】裏面電極層の硫化による反射率の低下を抑制し、光電変換装置の長期的な性能を向上させる。

【解決手段】光電変換ユニットであるa−Siユニット202及びμc−Siユニット204と、光電変換ユニットに形成された裏面電極層26とを設け、裏面電極層26は、銀を含む第2領域26bと、第2領域26b上に積層された阻止領域である第3領域26cと、第3領域26c上に積層され、第2領域26bより薄い犠牲領域である第4領域26dと、第4領域26d上に積層された保護領域である第5領域26eと、の積層構造を含み、第3領域26cは、第5領域26eより硫黄を透過し難い材料から構成し、第4領域26dは、第3領域26cより硫黄と化学反応し易い材料から構成する。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素ショットキーダイオードの製造において、ダイオードの順方向特性、特に障壁高さφBを安定させて、リーク電流のばらつきを低減させることが可能な半導体装置を提供する。

【解決手段】エピタキシャル層2上に乾式熱酸化によりシリコン酸化膜OX1を形成し、SiC基板1の裏面にオーミック電極3を形成し、その後、SiC基板1をアニールしてオーミック電極3とSiC基板1の裏面との間にオーミック接合を形成し、シリコン酸化膜OX1を除去した後、エピタキシャル層2上にショットキー電極4を形成する。その後、シンターを行い、ショットキー電極4とエピタキシャル層との間にショットキー接合を形成する。

(もっと読む)

SiC半導体デバイス及びその製造方法

【課題】SiC半導体デバイスにおいて、裏面電極の剥離を十分に抑制することができる製造方法と、裏面電極の剥離が防止された新規な裏面電極構造を有するSiC半導体デバイスを提供する。

【解決手段】SiC半導体上へチタン及びニッケルを含む層を形成して、加熱によりチタンカーバイドを含むニッケルシリサイド層を形成させ、析出した炭素層を逆スパッタにより除去することにより、後工程でニッケルシリサイド上に形成される金属層の電極が剥離することを抑制する。炭素層を除去する前のニッケルシリサイド表面の、析出した炭素の量とチタンカーバイドの炭素量の関係が、所定の条件のときに、さらに剥離防止の効果を向上させることができる。

(もっと読む)

21 - 40 / 461

[ Back to top ]