Fターム[4M104FF06]の内容

Fターム[4M104FF06]の下位に属するFターム

T、Y、逆L型、逆T型 (276)

台形 (304)

階段状 (86)

フィールドプレート又はその変形 (254)

Fターム[4M104FF06]に分類される特許

41 - 60 / 655

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】窒化物半導体層上の層間絶縁膜の開口部が、電界の集中が緩和される形状に安定して精度良く形成された窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層30と、窒化物半導体層30上に配置された第1の絶縁膜41と、第1の絶縁膜41上に配置された第2の絶縁膜42と、窒化物半導体層30上に互いに離間して配置された第1及び第2の主電極51,52と、第1及び第2の主電極51,52間で第2の絶縁膜42上に配置され、第1及び第2の絶縁膜に設けられた開口部を介して窒化物半導体層に接続するフィールドプレート60とを備える窒化物半導体装置であって、開口部において、窒化物半導体層30の表面と第1の絶縁膜41の側面とのなす第1の傾斜角が、窒化物半導体層30の表面と第2の絶縁膜42の側面を延長した線とのなす第2の傾斜角よりも小さく形成されている。

(もっと読む)

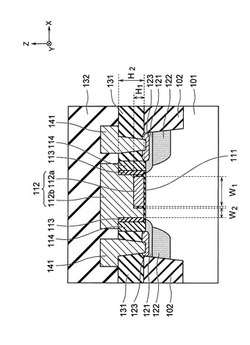

半導体装置及びそれを用いた電力変換装置

【課題】低損失、高耐圧、出力電圧のdV/dtの制御が容易で、製造が容易なIGBTを提供する。

【解決手段】第1導電型の第1半導体層と、第1半導体層の表面の第2導電型の第2半導体層と、第1半導体層の表面に形成されたトレンチと、第1半導体層の表面の半導体凸部と、半導体凸部の表面形成された第3半導体層と、第3半導体層の表面の第4半導体層と、トレンチの内壁に沿って設けられたゲート絶縁層と、トレンチの内壁に沿って設けられた第1層間絶縁層と、ゲート絶縁層を介して第4半導体層に対向する第1導電層と、第1層間絶縁層の第2導電層と、第2導電層の表面を覆う第2層間絶縁層と、第3半導体層と第4半導体層の表面に形成され、前記第4半導体層に電気的に接続される第3導電層と、第3導電層と第3半導体層を接続するコンタクト部と、第2半導体層の表面に形成された第4導電層とを備え、半導体凸部の表面の一部が第1半導体層である。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

ジャンクションバリアショットキーダイオード

【課題】ジャンクションバリアショットキーダイオードの耐圧を低下させることなく、リーク電流の低減とオン電流の増大を両立したダイオードを提供する。

【解決手段】本発明は、ジャンクションバリアショットキーダイオードにおいて、pn接合を形成するp型領域の側部に存在するpn接合の傾きが、当該p型領域の底部に存在するpn接合の傾きより急峻である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

41 - 60 / 655

[ Back to top ]