Fターム[4M104FF06]の内容

Fターム[4M104FF06]の下位に属するFターム

T、Y、逆L型、逆T型 (276)

台形 (304)

階段状 (86)

フィールドプレート又はその変形 (254)

Fターム[4M104FF06]に分類される特許

161 - 180 / 655

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

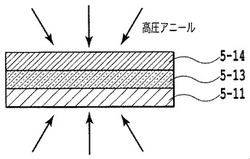

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

半導体装置

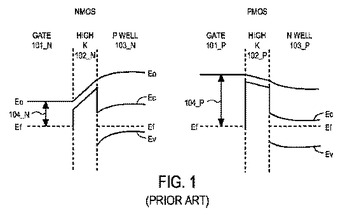

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体発光装置

【課題】局所的な電流集中を防止して均一な発光分布を得ることができる半導体発光装置を提供する。

【解決手段】半導体発光装置は、支持基板と、支持基板上に設けられた光反射性を有する反射電極と、反射電極上に設けられた発光層を含むAlGaInP系半導体膜と、半導体膜上に設けられた表面電極と、を含む。表面電極は、半導体膜上に分散配置された複数の電極片からなるオーミック電極を含む。反射電極は、オーミック電極を構成する電極片の各々を挟んだ両側において電極片に沿うように設けられた線状のライン電極および複数の島状のドット電極からなる。ライン電極とドット電極との距離をa、オーミック電極とドット電極の水平距離をb、互いに隣接するドット電極間の距離をcとしたときに、b>a且つ0.8(a2+2ab)1/2<c<2.4(a2+2ab)1/2を満たすように表面電極および反射電極が配設される。

(もっと読む)

電極構造体の製造方法および太陽電池

【課題】スパッタリングを利用した場合でも、電極構造体に、微細な凹凸構造を欠点なく正確に、かつ簡便に形成することのできる電極構造体の製造方法、ならびに電極構造体に欠点のない微細な凹凸構造が正確に形成されてなる太陽電池を提供する。

【解決手段】表面に微細な凹凸構造を有するスタンパー1の表面上に、導電体層2を剥離可能に形成し、スタンパー1上の導電体層2と、硬化性材料4とを接触させ、その状態で硬化性材料4を硬化させて、微細な凹凸構造を有する凹凸基層5を形成するとともに、凹凸基層5と導電体層2とを接着し、スタンパー1と、凹凸基層5に接着された導電体層2とを分離し、もって凹凸基層5上に導電体層2を転写して形成し、このようにして、微細な凹凸構造を有する電極構造体10を製造する。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

接続されたナノ構造体及びそのための方法

種々の材料及びアプローチの1以上を用いてナノ構造体を接続する。種々の例示的実施形態で、ナノ構造体間の接続部で2つ以上のナノ構造体が接続される。ナノ構造体は、接続部で接触するかほぼ接触してよく、接続材料を接続部で堆積及び核形成させてナノ構造体同士を結合する。種々の用途で、核形成した接続材料はナノ構造体間の伝導率(熱的及び/又は電気的)を向上させる。いくつかの実施形態では、接続材料は更に、例えばナノ構造体に沿って成長することにより及び/又はナノ構造体にドープすることにより、ナノ構造体自身の伝導率を上昇させる。  (もっと読む)

(もっと読む)

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

161 - 180 / 655

[ Back to top ]