Fターム[4M104FF06]の内容

Fターム[4M104FF06]の下位に属するFターム

T、Y、逆L型、逆T型 (276)

台形 (304)

階段状 (86)

フィールドプレート又はその変形 (254)

Fターム[4M104FF06]に分類される特許

101 - 120 / 655

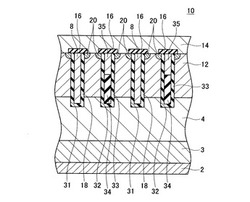

半導体装置

【課題】半導体装置の寄生容量成分を好適に調整する。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】安定したリカバリ耐量が得られる半導体装置を提供する。

【解決手段】表面電極21のうち抜き取り部2bに形成されたコンタクトホール20bから露出するコンタクト領域23と対向する部分をそれぞれコンタクト部21dとし、コンタクト部21dと表面パッド5とを結ぶ最短距離の線分L1上にそれぞれ切り込み部21cを形成する。これによれば、コンタクト部21dから表面パッド5までのホールが流れる経路が長くなって抵抗が高くなるので、コンタクト領域23にホールが集中することを抑制することができ、安定したリカバリ耐量を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造工程数を大幅に増加することなく高性能な薄膜トランジスタを備えた薄膜トランジスタ回路基板、及び、薄膜トランジスタ回路基板の製造方法を提供する。

【解決手段】 絶縁基板上に配置されたゲート電極と、前記ゲート電極の上に配置されたゲート絶縁膜と、前記ゲート絶縁膜の上に配置されたポリシリコンによって形成され、前記ゲート電極の直上に位置するチャネル領域、前記チャネル領域に隣接するとともに前記チャネル領域よりも高濃度の不純物を含む低濃度不純物領域、及び、前記低濃度不純物領域に隣接するとともに前記低濃度不純物領域よりも高濃度の不純物を含む高濃度不純物領域を含む半導体層と、前記チャネル領域及び前記低濃度不純物領域の上に配置され、前記チャネル領域の直上の膜厚が前記低濃度不純物領域の直上の膜厚よりも厚い保護膜と、前記高濃度不純物領域に電気的に接続された電極と、を備えたことを特徴とする薄膜トランジスタ回路基板。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

半導体装置および電力変換装置

【課題】低損失と高耐圧を保持しながら、ターンオンスイッチング期間中におけるdv/dtのゲート駆動回路による制御性を向上できる半導体装置を提供する。

【解決手段】第1導電型の第1半導体層4と、その表面付近に形成された第2導電型の第2半導体層2と、これに電気的に接続する第1主電極11と、第1半導体層4に隣接し第2半導体層2とは逆側の表面付近に形成された第2導電型の第3半導体層6と、この上部に選択的に設けられた第1導電型の第4半導体層7と、第3半導体層6及び第4半導体層7に電気的に接続する第2主電極14と、側面が第4半導体層7と第3半導体層6に接し第1半導体層4に達するトレンチ17と、この側面に沿ってポリシリコンのサイドウオールにより形成されたゲート電極9と、トレンチ17内でゲート電極9から離れて設けられ第2主電極14と電気的に接続するポリシリコン電極18が設けられている。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い信頼性を有する、半導体装置およびその製造方法を提供すること。

【解決手段】n型半導体基板の一方の主面に、p型ベース領域とn型エミッタ領域と所要の位置にゲート絶縁膜を介して載置されるゲート電極とからなるMOSゲート構造と該MOSゲート構造を沿面方向に取り巻く耐圧構造部とを有し、他方の主面に1μm以下の浅い逆阻止接合を有するp型コレクタ層を備える半導体装置において、前記コレクタ層の他方の主面上に、バッファ絶縁層を介して被覆されるコレクタ電極が、前記バッファ絶縁層に設けられたコンタクトホールを通して前記コレクタ層と導電接触する半導体装置とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧が高く破壊等が生じにくい、信頼性の高い半導体装置を提供する。

【解決手段】基板上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層14と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスの底面は、中央部分23aが周辺部分23bに対し高い形状であることを特徴とする半導体装置。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

高耐圧トランジスタ及びその製造方法

【課題】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法を提供する。

【解決手段】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法において、半導体基板の所定部位が酸化された第1絶縁膜パターン、及び第1絶縁膜パターンを少なくとも部分的に取り囲む第2絶縁膜パターンを形成する。基板上に導電性物質を蒸着して、第1端部は第1絶縁膜パターン上に位置し、第2端部は第2絶縁膜パターン上に位置するゲート電極を形成した後、基板表面の所定部位に不純物を注入してソース/ドレイン領域を形成する。ゲート電極のエッジ部分に集中される電界を緩和して高い降伏電圧を有するトランジスタを製造することができ、熱酸化膜パターンとCVD酸化膜パターンをゲート酸化膜として使用することで、MOSトランジスタにおいて電流特性及びON抵抗特性を改善することができる。

(もっと読む)

半導体装置

【課題】表示装置に用いられるトランジスタは、より高耐圧なものが求められており、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図る。

【解決手段】チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられたトランジスタを有する半導体装置である。バッファ層は、チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にあって、特にドレイン端近傍の電界を緩和して、トランジスタの耐圧を向上させるように設けられる。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

化合物半導体装置

【課題】電流コラプス現象が抑制され、且つフィールドプレート電極による電界集中を緩和する効果の低下が抑制された化合物半導体装置を提供する。

【解決手段】III族窒化物半導体層と、III族窒化物半導体層上に配置された絶縁膜7と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたドレイン電極4と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたソース電極3と、ドレイン電極とソース電極間においてIII族窒化物半導体層の上面から膜厚方向に第2の距離T3の位置に絶縁膜を介して配置されたゲート電極5と、ドレイン電極とゲート電極間においてIII族窒化物半導体層の上面から膜厚方向に第1の距離T1より短い第2の距離T2の位置に絶縁膜を介して配置されたフィールドプレート電極6とを備える。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

101 - 120 / 655

[ Back to top ]