Fターム[4M104FF06]の内容

Fターム[4M104FF06]の下位に属するFターム

T、Y、逆L型、逆T型 (276)

台形 (304)

階段状 (86)

フィールドプレート又はその変形 (254)

Fターム[4M104FF06]に分類される特許

141 - 160 / 655

整流器ブリッジ回路

【課題】本発明の課題は、ロードダンプ時の動作において、すなわち負荷の遮断が急に行われる場合であっても適切な整流器ブリッジ回路を提供することである。

【解決手段】前記課題は、請求項1に従う回路によって解決される。

(もっと読む)

有機電子デバイス用電極

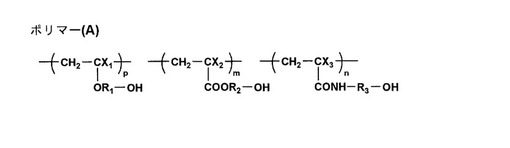

【課題】透明性、導電性且つ生産後のロール状態での保存性が良好な有機電子デバイス用電極の提供。

【解決手段】透明基材上に、導電性の金属細線パターンと、導電性ポリマー層を設けた有機電子デバイス用電極において、該金属細線パターンの金属細線の厚みをaとし、開口部における該導電性ポリマー層の厚みをbとしたとき、以下式1〜式3で表される条件を満たし、且つ、導電性ポリマー層がπ共役系導電性高分子とポリアニオンとを含んでなる導電性ポリマーおよび下記ポリマー(A)を有する有機電子デバイス用電極。0.2≦a≦2.0(式1)0.2≦b≦2.0(式2)−0.2≦b−a≦1.8(式3) (もっと読む)

(もっと読む)

半導体装置

【課題】IGBTにおいて、P型コレクタ層におけるキャリア濃度の変化を抑制し、オン電圧のばらつきを低減可能な技術を提供することを目的とする。

【解決手段】半導体装置は、表面側にMOSFET構造1が形成されたN型半導体基板2と、N型半導体基板2の裏面に形成されたP型コレクタ層4とを備える。そして、P型コレクタ層4上にストライプ状に互いに離間して形成された、AlとSiとのAl合金からなるAlSi電極7aを含む積層構造の裏面電極7を備える。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】動作不良や動作速度の低下の発生を従来よりも抑制できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】窒素が導入されたニッケルからなるニッケル層28をナノワイヤ5の周辺に形成して熱処理することにより、ナノワイヤ5に形成されたソース15及びドレイン16をシリサイド化させつつ、窒素によりゲート電極被覆領域ER1までシリサイド化されることを抑制できることから、従来よりもゲート電極被覆領域ER1にチャネル17を確保でき、かくして動作不良や動作速度の低下の発生を従来よりも抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

新規な電極

化合物半導体装置

【課題】閾値電圧の高い良好なノーマリオフ特性を有する化合物半導体装置を提供する。

【解決手段】キャリア走行層21とキャリア供給層22を有し、二次元キャリアガス層211が形成される化合物半導体層2と、化合物半導体層2上に互いに離間して配置され、二次元キャリアガス層211とオーミック接続する第1の主電極3及び第2の主電極4と、第1の主電極3と第2の主電極4間で、化合物半導体層2上に配置された金属酸化物半導体膜8と、金属酸化物半導体膜8上に配置された、金属酸化物半導体膜8に接するチタン膜又はチタンを含む化合物膜を有する制御電極5とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、電極表面を平坦化した高い信頼性を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】n形ベース層2と、n形ベース層2の表面に設けられたp形ベース領域3と、p形ベース領域3の表面に選択的に設けられたn形エミッタ領域4と、p形ベース領域3およびn形エミッタ領域4とゲート絶縁膜を介して対向するゲート電極5と、p形ベース領域3およびn形エミッタ領域4に電気的に接続されたエミッタ電極21と、エミッタ電極21の表面に形成された凹部31を埋め込んだ絶縁部材25と、エミッタ電極21と絶縁部材25との上に設けられたエミッタ電極23と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】トランジスタの閾値電圧を高くする。

【解決手段】フローティング電極110は半導体層102上に形成されており、絶縁層はフローティング電極110上に形成されている。バイアス電極134は、絶縁層を介してフローティング電極110の一部に対向することにより、フローティング電極110と容量結合し、かつフローティング電極110が半導体層102にチャネル領域を形成しない大きさの電圧が印加される。制御電極132は、絶縁層を介してフローティング電極110の他の部分に対向することにより、フローティング電極110と容量結合し、かつトランジスタのオン/オフを制御するための制御電圧が入力される。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法

【課題】デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】互いに異なる極性を有する複数の半導体層20,22を含み、ソース電極28とドレイン電極32との間にデュアル・デプレション領域が存在し、該複数の半導体層は、上部物質層26、中間物質層22、下部物質層20を含み、中間物質層の極性は、上部物質層及び下部物質層の極性と異なる高電子移動度トランジスタである。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

ヘテロ接合障壁領域を含む半導体デバイス及びその製造方法

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるチャネル保護膜6d(5d)に鋭角なエッジ部6p(5p)を設けて、そのエッジ部6d(5d)でソース電極6i(5i)と不純物半導体膜6g(5g)の積層体を破断するようにして、その積層体がチャネル保護膜6d(5d)の上面に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

141 - 160 / 655

[ Back to top ]