Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

61 - 80 / 590

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

ショットキーダイオードおよびPNダイオード

【課題】耐量の大きいダイオードを提供する。

【解決手段】ショットキーダイオードであって、窒化物半導体で形成された半導体層と、半導体層上に形成され、半導体層にショットキー接続されたショットキー電極と、を備え、ショットキーダイオードに逆バイアスがかかったときに、ショットキー電極の端部の下方の半導体層において空乏化する領域は、ショットキー電極の他の一部の下方の半導体層において空乏化する領域より長いショットキーダイオードを提供する。

(もっと読む)

ノーマリーオフ型高電子移動度トランジスタ

【課題】 ノーマリーオフ型高電子移動度トランジスタを提供する。

【解決手段】 ノーマリーオフ型トランジスタは、III−V半導体材料の第1の領域、第1の領域上のIII−V半導体材料の第2の領域、第2の領域上のIII−V半導体材料の第3の領域、および第3の領域の少なくとも1つの側壁に隣接するゲート電極を含む。第1の領域はトランジスタのチャネルを提供する。第2の領域は第1の領域のバンドギャップより大きなバンドギャップを有し、チャネル内に2D電子ガス(2DEG)を引き起こす。第2の領域は第1の領域と第3の領域との間に挿入される。第3の領域は、トランジスタのゲートを提供し、トランジスタが正の閾値電圧を有するようにチャネル内の2DEGを空乏化するのに十分な厚さを有する。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

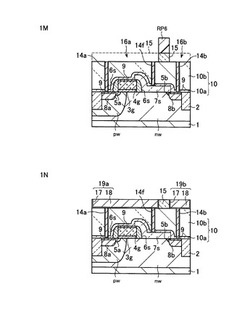

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置

【課題】本発明は、トレンチの設計自由度が損なわれることなく、プロセス条件に制約されることなく、電気的特性を向上することができる半導体装置を提供する。

【解決手段】半導体装置10は、第1の半導体領域1内のトレンチ15の底部に第4の半導体領域4を介して配設され、隣り合う同士において相互に離間され、第1の半導体領域1よりも高い不純物密度を有する第1の導電型の第5の半導体領域5を備える。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタと回生素子とを含み、優れたリカバリ特性によりスイッチング損失が低減された半導体装置を提供すること。

【解決手段】電界効果型トランジスタと回生素子とを含み、前記電界効果型トランジスタは、第1の導電型を有する第1の半導体層と、前記第1の半導体層の表面に配置された第2導電型を有する第2の半導体層と、前記第2の半導体層の表面に配置された前記第1導電型を有する第3の半導体層と、前記第1の半導体層と前記第2の半導体層と前記第3の半導体層とに隣接するように配置された絶縁膜を介して配置されたゲート電極と、第1の金属層と、第2の金属層と、を備え、前記回生素子は、前記第1の金属層と電気的に接続されるアノード端子と、前記第2の金属層と電気的に接続されるカソード端子と、を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】水素を用いた熱分解において、水素濃度を規定してエッチング速度を制御することで、半導体装置の製造方法の加工精度を向上させる。

【解決手段】半導体装置1の製造方法は、基板10に窒化物半導体で形成された第1層(障壁層25)および第2層(キャップ層26)を順に堆積させる堆積工程と、窒素および水素の混合雰囲気中で加熱して第2層をエッチングする熱エッチング工程とを備える。熱エッチング工程では、水素濃度が1%以上20%以下であることが望ましい。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

半導体デバイス

【課題】低シート抵抗化、リーク電流の低減、および、オーミック電極の接触抵抗の低減を実現する。

【解決手段】基板と、基板上に設けられ第1の窒化物系化合物半導体からなるチャネル層と、チャネル層上に設けられたバリア層と、バリア層上に設けられた第1電極と、チャネル層の上方に設けられた第2電極とを備え、バリア層は、チャネル層上に設けられ第1の窒化物系化合物半導体よりバンドギャップエネルギーが大きい第2の窒化物系化合物半導体からなる障壁層と、第2の窒化物系化合物半導体よりバンドギャップエネルギーが小さい第3の窒化物系化合物半導体からなり量子準位が形成された量子準位層とを有する半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および順方向電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有し、表面12側に側壁22および底壁20を有する台形トレンチ17が形成されたSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。また、各台形トレンチ17の底壁20のエッジ部24を、曲率半径Rが0.01L<R<10L・・・(1)(式(1)において、Lはトレンチ17の幅方向に沿って対向するエッジ部24間の直線距離を示している。)を満たすように、台形トレンチ17の外方へ向かって湾曲する形状に形成する。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置

【課題】順方向電圧降下の増大が抑制され、且つ順方向サージ耐量の高い、整流機能を有する半導体装置を提供する。

【解決手段】互いに対向する第1の主面110から第2の主面120に向かって延伸し、且つ底部が第2の主面120に達しない複数の溝部15が形成された第1導電型の半導体積層体10と、それぞれの外縁領域の一部が溝部15の側面に露出するように半導体積層体10の第1の主面110に互いに離間して埋め込まれた第2導電型の複数のアノード領域20と、アノード領域20の形成されていない領域において半導体積層体10とショットキー接合を形成し、且つアノード領域20とオーミック接合を形成して、半導体積層体10の第1の主面110に配置されたアノード電極30と、半導体積層体10の第2の主面120に配置されたカソード電極40とを備える。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

非晶質酸化物薄膜トランジスタ及びその製造方法、その薄膜トランジスタを含むディスプレイパネル

【課題】本発明の実施例は非晶質酸化物薄膜トランジスタ及びその製造方法、ディスプレイパネルを開示する。

【解決手段】前記非晶質酸化物薄膜トランジスタは、ゲート電極、ゲート絶縁層、半導体活性層、ソース電極及びドレイン電極を含む。前記半導体活性層はチャネル層とオーミック接触層を含み、前記チャネル層は前記オーミック接触層に比べ酸素含有量が高い。また、前記チャネル層は前記ゲート絶縁層と接し、前記オーミック接触層は二つの独立したオーミック接触領域に分けられ、かつ前記二つの独立したオーミック接触領域はそれぞれ前記ソース電極、ドレイン電極と接する。

(もっと読む)

61 - 80 / 590

[ Back to top ]