Fターム[4M104GG12]の内容

Fターム[4M104GG12]に分類される特許

201 - 220 / 697

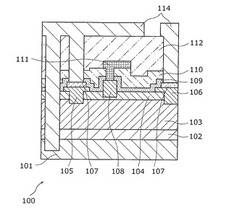

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

窒化物半導体デバイス

【課題】 窒化物半導体デバイスを提供する。

【解決手段】 一実施形態では、デバイスはIII族窒化物チャネル層(3)とIII族窒化物チャネル層(3)上のIII族窒化物障壁層(4)とを含み、III族窒化物障壁層(4)は第1部分(4−1)と第2部分(4−2)とを含み、第1部分(4−1)は第2部分(4−2)より薄い厚さを有する。pドープIII族窒化物ゲート層部(5)は、III族窒化物障壁層(4)の少なくとも第1部分(4−1)上に配置され、ゲートコンタクト(10)はpドープIII族窒化物ゲート層部(5)上に形成される。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法

【課題】デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】互いに異なる極性を有する複数の半導体層20,22を含み、ソース電極28とドレイン電極32との間にデュアル・デプレション領域が存在し、該複数の半導体層は、上部物質層26、中間物質層22、下部物質層20を含み、中間物質層の極性は、上部物質層及び下部物質層の極性と異なる高電子移動度トランジスタである。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

高電子移動度トランジスタ

【課題】 HEMTにおいて、2次元電子ガス層の電気抵抗の増加が抑制された正孔排出用電極を提供すること。

【解決手段】 HEMT10は、ゲート電極34とドレイン電極32の間のヘテロ接合層27に接触する正孔選択通過膜43と、その正孔選択通過膜43に接触する正孔排出用電極46を備えている。正孔選択通過膜43は、へテロ接合層27に接触する第1部分領域42と正孔排出用電極46に接触する第2部分領域44を有している。第2部分領域42のp型不純物の濃度は、第1部分領域44のp型不純物濃度よりも濃い。

(もっと読む)

半導体装置

【課題】ボンディングメタル層の材料によるショットキ界面の劣化を抑制または防止して、デバイス特性を改善する。

【解決手段】ショットキダイオードは、半導体基板10と、この半導体基板10にショットキ接触するショットキ金属層15と、ショットキ金属層15上に形成されたボンディングメタル層16とを含む。ショットキ金属層15は、金属窒化物層32bを含む金属窒化物含有多結晶金属層32からなるバリア層と、これに積層された金属層31とを有している。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

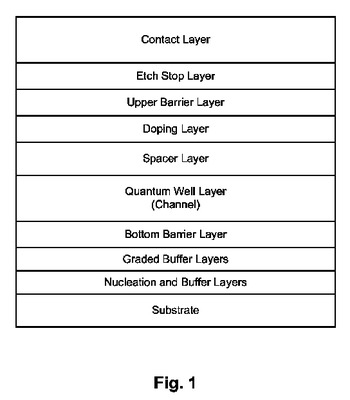

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

ガリウム窒化物又は他の窒化物ベースのパワーデバイスのためのゲルマニウムを含む低オーミックコンタクト

基板(120)、基板の上のIII族窒化物層(102、104,406)、及び、III族窒化物層の上の電気的コンタクト(108a、108b)を含む装置。電気的コンタクトは、導電性材料の複数層(110〜116)を有するスタックを含み、スタック内の前記層の少なくとも1つがゲルマニウムを含む。スタック内の層は、アルミニウム銅を含むコンタクト層(116)を含み得る。スタックは、チタン又はチタン合金層、アルミニウム又はアルミニウム合金層、及び、ゲルマニウム又はゲルマニウム合金層、を含み得る。スタック内の少なくとも1つの層は、約1%から約5%の間のゲルマニウム含有量を有するアルミニウム又はチタン合金を含み得る。

(もっと読む)

(もっと読む)

201 - 220 / 697

[ Back to top ]