Fターム[4M106AA02]の内容

半導体等の試験・測定 (39,904) | 対象 (8,684) | チップ (1,932)

Fターム[4M106AA02]に分類される特許

141 - 160 / 1,932

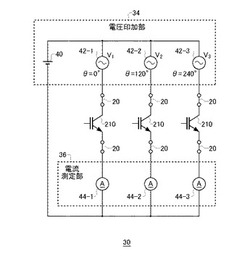

測定装置

【課題】測定時におけるスイッチング素子の破損の可能性を低くする。

【解決手段】ウエハに形成された複数のスイッチング素子のリーク電流を測定する測定装置であって、ウエハに形成された複数のスイッチング素子のそれぞれの端子と電気的に接続するプローブと、ウエハに形成された複数のスイッチング素子のそれぞれにプローブを介して互いに異なる位相で変化する変化電圧を印加する電圧印加部と、オフ状態における複数のスイッチング素子のそれぞれに流れるリーク電流を測定する電流測定部とを備える測定装置を提供する。

(もっと読む)

半導体装置の不良解析方法

【課題】差画像解析を用いた半導体装置の不良解析を短時間で、効率よく高精度に行う。

【解決手段】良品、および不良品サンプルの半導体装置にテストパターンの掃引を開始して顕微鏡により発光画像を取得する。取得した発光画像を囲う反応ボックスを設定してレイアウト座標系の位置データに変換し、良品サンプルの反応ボックスと不良品サンプルの反応ボックスとが重なっている面積を計算する。重なっている面積がしきい値より少ない反応ボックスを差分ボックスと判定し、その差分ボックスを発光解析コントローラに表示する。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用セラミック配線基板に設けられた測定端子とSiウェハの表面に形成された測定パッドとの位置ずれが小さく、基板表面の研磨性に優れ、かつ耐薬品性の良好なプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 前記絶縁基体は、前記主結晶相の割合を100質量%としたときに、前記セラミック焼結体が、前記SiをSiO2換算で1.0〜3.0質量%、前記AlをAl2O3換算で0.4〜1.0質量%、前記MnをMn2O3換算で1.0〜4.0質量部、前記TiをTiO2換算で2.0〜8.0質量部含有する。

(もっと読む)

配線構造、半導体装置及び不良箇所特定方法

【課題】不良箇所の特定の容易化を実現し得る配線構造、半導体装置及び不良箇所特定方法を提供することにある。

【解決手段】基板10上に形成された第1の配線14と、第1の配線上に形成され、第1の領域において第1の配線と重なり合う第2の配線20とを有し、第1の配線は、第1の領域外に突出する第1のタブ部16を有している。

(もっと読む)

合成画像形成方法及び画像形成装置

【課題】本発明は、合成画像を形成する場合に、重複領域のパターンの状態に応じて、適正に合成画像を形成することを目的とする合成画像形成方法、及び合成画像形成装置の提供を目的とする。

【解決手段】上記目的を達成するための一態様として、複数の画像を合成して合成画像を形成する合成画像形成方法、及び装置であって、複数の画像間の重複領域について、当該重複領域中に含まれるパターンの属性情報を作成し、当該パターンの属性情報に基づいて、合成対象となる画像を選択し、当該選択に基づいて画像合成を行う方法、及び装置を提案する。また、他の一態様として、重複領域内の属性情報を用いて、複数段階で画像合成を行う方法、及び装置を提案する。

(もっと読む)

プローブピン及びプローブピンの製造方法

【課題】均一な厚さで絶縁被覆され、各プローブ間の被膜厚のばらつきが小さく、高温雰囲気でも絶縁膜相互の融着が生じることない電着被膜にて被覆され、且つ、変形することなく先端部の電着被膜部が剥離されているプローブピンを提供する。

【解決手段】分子骨格中にシロキサン骨格を有し、分子中にアニオン性基を有するブロック共重合ポリイミドを含む絶縁体が金属細線110の表面に電着塗装されて電着被膜部130を形成しており、金属細線110の少なくとも一方の端部の電着被膜部130が、極性溶媒にて剥離除去されている。

(もっと読む)

プローブカード

【課題】プローブに加える荷重を低く維持したまま、狭小の有効スペースでプローブのストローク長さを長くし、かつ、プローブが安定して伸縮動作することができるプローブカードを提供する。

【解決手段】本発明のプローブカード1のプローブ2においては、ばね部として、ドーナツ形状の楕円板状に形成された第1ビーム部4および第2ビーム部5が傾斜配置されている。また、プローブ2は、第1ビーム部4の上端部および第2ビーム部5の下端部をヒンジ部Hとして2個のビーム部を連結させ、シングルアームパンタグラフ形状に形成されている。

(もっと読む)

半導体装置、半導体装置の検査方法、及び、半導体装置の製造方法

【課題】半導体装置の製造工程の増大を抑制しつつ、パッドの針跡を容易に確認できるようにする。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に形成された回路素子と、半導体基板1上に形成され、回路素子と電気的に接続されたパッド(接続パッド4)と、を有している。パッドは、平面視において、導体が存在する実体パターン41と、前記導体が存在しない開口パターン42と、を含む所定のパターン形状に形成されている。

(もっと読む)

積層デバイスの製造方法

【課題】歩留まりよく積層デバイスを製造可能な積層デバイスの製造方法を提供する。

【解決手段】半導体ウエーハをm枚(mは3以上の整数)準備する半導体ウエーハ準備ステップと、m枚の半導体ウエーハにおいて、良品、不良品マップ12A、12B、12C、12Dを半導体ウエーハ毎に作成するマップ作成ステップと、該m枚の半導体ウエーハから該所定数nの半導体ウエーハを選択して積層し、半導体デバイス中に不良品半導体デバイス16bが含まれる数が最も少なくなる組み合わせを検出する組み合わせ検出ステップと、該組み合わせ検出ステップで検出した半導体ウエーハの組み合わせに従って、該所定数nの半導体ウエーハを形成する積層ウエーハ形成ステップと、該積層ウエーハ形成ステップで形成した該積層ウエーハを該分割予定ラインに沿って分割して、該所定数nの半導体デバイスが積層された積層デバイスを形成する分割ステップと、を具備する。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用セラミック配線基板に設けられた測定端子とSiウェハの表面に形成された測定パッドとの位置ずれが小さく、耐薬品性試験においてもビアホール導体の抵抗変化の小さいプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 ムライト質焼結体からなる絶縁基体の内部に、モリブデンを主成分とするビアホール導体を備えているプローブカード用セラミック配線基板であって、前記ビアホール導体がモリブデン100質量部に対して、チタンをTiO2換算で0.8〜8.2質量部、マンガンをMnO換算で1.4〜3.4質量部含む。

(もっと読む)

欠陥検査方法、欠陥検査装置及び欠陥検査システム

【課題】ウェハで検出された欠陥の座標を適正に変換する。

【解決手段】ウェハ端部の表面画像を取得し(ステップS1)、取得された表面画像を用いて、ウェハ端部の欠陥を、そのウェハに設定されている第1原点からの座標によって検出する(ステップS2)。更に、取得された表面画像を用いて、ウェハ上にある複数のスクライブラインのうち、一のスクライブラインを検出する(ステップS3)。そして、検出されたその一のスクライブラインに基づき、ウェハ端部の欠陥の、第1原点からの座標を、ウェハ上の複数のスクライブラインに設定されている第2原点からの座標に変換する(ステップS4)。

(もっと読む)

プローブ装置及びプローブ測定方法

【課題】プローブの複数端子と被測定物の位置関係を簡便且つ適正に求める。

【解決手段】プローブ装置10は、複数端子を含むプローブ11、そのプローブ11を保持する保持部12、保持部12に設けられ、プローブ11に向かって光13aを照射する照射部13を含む。更に、プローブ装置10は、照射部13から照射される光13aによって被測定物20上に投影されるプローブ11の複数端子の影を含んだ像を取得する取得部14を含む。取得部14で取得される像から、プローブ11の各端子と被測定物20との位置関係が求められる。

(もっと読む)

試験装置

【課題】被試験デバイスへ過剰な電流が流入することを防ぐ。

【解決手段】被試験デバイスを試験する試験装置であって、前記被試験デバイスに供給する電源電圧を発生する電源部と、前記電源部から前記被試験デバイスに至る経路上に設けられた誘導負荷部と、前記誘導負荷部に対して前記被試験デバイスと並列に接続された第1半導体スイッチと、前記被試験デバイスに対する電源電圧の供給を遮断する場合に、前記第1半導体スイッチをオンとする制御部とを備える試験装置を提供する。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用セラミック配線基板に設けられた測定端子とSiウェハの表面に形成された測定パッドとの位置ずれが小さく、異物付着による外観不良が無くかつかつ耐薬品性に優れたプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 ムライトを100質量部としたときに、前記MnをMn2O3換算で2.0〜4.0質量部、前記TiをTiO2換算で4.0〜8.0質量部および前記MoをMoO3換算で0.4〜1.2質量部含有するとともに、前記粒界部に、W−Mo合金を有し、かつ前記セラミック焼結体は、X線回折において、前記ムライトのメインピークの回折強度に対するMo−W合金のメインピークの回折強度の比が0.17〜0.90である。

(もっと読む)

ウエハー検査システム

【課題】リレー回路板により、テスト結果信号の分流を行い、イメージ信号はイメージ処理装置に直接伝送して処理を行うウエハー検査システムを提供する。

【解決手段】ウエハー検査システムは、ウエハー9に対して検査を行い、各プローブ2022はウエハー9に触れ、電気信号を伝送及び受信し、照明器203は開口2021を通して光をウエハー9上に照射し、テストサーバー204は検査の関連プロセス及びデータ処理の執行を制御し、テスト回路板210はテスト信号を発信し、結果信号を受信し、判断を行い、ロードボード208は制御回路板209と少なくとも1個のテスト回路板210に連接し、少なくとも1個のリレー回路板207はプローブカード202、ロードボード208、少なくとも1個のイメージ処理カード206にそれぞれ連接し、伝送データの伝送方向を切り替える。

(もっと読む)

プローブカードの検査方法及びこれに用いる検査用ボード

【目的】 本発明の目的は、検査時間を短縮することができるプローブカードの検査方法及びこれに用いる検査用ボードを提供する。

【構成】 プローブカードの検査方法は、共通電極120A、120Bと、共通電極120Aに電気的に接続されたプローブ130A1〜A4と、共通電極120Bに電気的に接続された複数のプローブ130B1〜B4とを備えたプローブカード100の検査方法であって、共通電極120A、120Bに電力を供給しつつ、プローブ130A1〜A4を一本毎に検査電極220A1〜A4に、プローブ130B1〜B4を一本毎に検査電極220B1〜B4に略同時に接触させる。

(もっと読む)

コンタクトプローブピン

【課題】導電性と耐久性を兼ね備えた炭素皮膜を、先端が分割された基材に対して形成するようなコンタクトプローブピンにおいて、使用環境が高温になる様な状況下においても、Sn付着を極力低減し、長期間に亘って安定な電気的接触を保つことのできるコンタクトプローブピンを提供する。

【解決手段】先端が2つ以上の突起に分割され、該突起で被検面に繰り返し接触するコンタクトプローブピンであって、少なくとも前記突起の表面には、金属および/またはその炭化物を含有する炭素皮膜が形成されていると共に、前記突起の頂部における曲率半径が30μm以上である。

(もっと読む)

半導体集積回路

【課題】例えばクラック発生などに起因する大量生産段階での低歩留りという問題を防止できる半導体集積回路を提供する。

【解決手段】パッドメタルの下に回路を有する半導体集積回路において、パッド開口部分のパッドメタルの少なくとも下全面に、互いに同一の電位を有する配線メタルを形成し、当該配線メタルの電位を上記パッドメタルと異なる電位に設定した。また、上記配線メタル、及び上記配線メタル以外の電位を有する別の配線メタルは、上記パッドメタルよりも下層に形成される。さらに、上記半導体集積回路の複数のパッドにおいて、バッド開口部分のパッドメタルの少なくとも下全面に形成された複数の配線メタルは互いに同一の電位に設定される。

(もっと読む)

コンタクトプローブピンおよび検査方法

【課題】導電性と耐久性を兼ね備えた炭素皮膜を、先端が分割された基材に対して形成するようなコンタクトプローブピンにおいて、使用環境が高温になる様な状況下においても、Sn付着を極力低減し、長期間に亘って安定な電気的接触を保つことのできるコンタクトプローブピン、およびコンタクトプローブピンを用いた有用な検査方法を提供する。

【解決手段】本発明のコンタクトプローブピンは、先端が2つ以上の突起に分割され、該突起で被検面に繰り返し接触するコンタクトプローブピンであって、少なくとも前記突起の表面には、金属および/またはその炭化物を含有する炭素皮膜が形成されており、前記突起の各頂部には、被検面に接触する方向に対して略垂直方向の平坦面を有すると共に、当該平坦面の合計面積が500μm2以上、5000μm2以下である。

(もっと読む)

プローブおよびプローブの製造方法

【課題】プローブ本体と微小カンチレバーとの間の結合力を向上させることができるとともに、プローブ本体からオーバーハングした微小カンチレバーを所望の形状や寸法に形成することができるプローブおよびプローブの製造方法を提供する。

【解決手段】本発明のプローブ1においては、プローブ本体2および微小カンチレバー3が1回のめっき処理により一体形成される。また、本発明のプローブ1の製造方法は、下地層形成工程、シード膜形成工程、第1レジスト層形成工程、親水処理工程、第2レジスト層形成工程、プローブ形成工程および除去工程を備える。上記の親水処理により、第2レジスト層14となるドライフィルムレジストは第1レジスト層13の表面13aに熱圧着させることなく粘着力のみにより固着している。

(もっと読む)

141 - 160 / 1,932

[ Back to top ]