Fターム[4M106AB01]の内容

半導体等の試験・測定 (39,904) | チェック素子の細部 (1,099) | FET、MOS (226)

Fターム[4M106AB01]の下位に属するFターム

Fターム[4M106AB01]に分類される特許

1 - 20 / 182

絶縁膜評価方法およびテスト素子

半導体装置

【課題】酸化物半導体の分野は近年注目されはじめた分野である。そのため、酸化物半導

体層を用いたトランジスタの電気特性と、酸化物半導体層の物性値と、の相関関係が未だ

明らかになっていない。よって、酸化物半導体層の物性値を調整することによって、トラ

ンジスタの電気特性を向上させることを第1の課題とする。

【解決手段】少なくとも、ゲート電極と、酸化物半導体層と、前記ゲート電極と前記酸化

物半導体層との間に挟まれたゲート絶縁層と、を有し、前記酸化物半導体層は、比誘電率

が13以上(又は14以上)である半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の検査方法

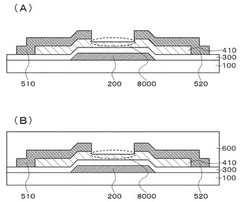

【課題】狭いゲート電極間にコンタクトを配置することなく、オーバーラップ容量を測定する。

【解決手段】この半導体装置は、下記のような第1TEGパターン(不図示)を備えている。第1TEGパターンは、素子分離領域500と、素子分離領域500に形成された開口部(不図示)と、開口部上に設けられ、互いに平行に延伸した複数のゲート電極300と、開口部のゲート電極300で覆われていない部分に形成された拡散領域200と、を備えている。ここで、ゲート電極300の一方の端部は、開口部の外縁よりも内側に配置されている。また、第1コンタクト240は、ゲート電極300の一方の端部と、開口部の外縁の間に位置して、拡散領域200に接続している。一方、第2コンタクト340は、ゲート電極300に接続している。

(もっと読む)

電気特性取得評価方法

【課題】電気特性取得評価方法に関し、試料側にもプローブ側にも問題を発生させることなく安定な電気特性取得評価を行う。

【解決手段】積層体の表面側電極に対するコンタクトホール21を露出する工程と、前記露出したコンタクトホール21に導電性物質を埋め込んで凸状構造22を形成する工程と、前記凸状構造22を含む領域にカンチレバーを間欠接触測定方式で接触させて前記凸状構造22の位置を認識する工程と、前記凸状構造22の中心軸の方向に前記カンチレバーを押しつけて電気特性を取得する工程とを設ける。

(もっと読む)

半導体装置、半導体装置の検査方法及び製造方法

【課題】コンタクト周りのキラー欠陥検査を容易にするパターンを有する半導体装置、半導体装置の検査方法及び製造方法を提供する。

【解決手段】半導体基板の第1導電型領域の表面に設けられ、それぞれ第1の方向に延在する複数の第2導電型領域と、複数の第2導電型領域とそれぞれ複数の個所で交差することにより各第2導電型領域にソースとドレインが直列に接続された複数のMOSトランジスタを形成するゲート配線と、複数のMOSトランジスタとゲート配線との表面を覆う絶縁膜と、絶縁膜の表面から複数のMOSトランジスタのソースドレイン領域にそれぞれ設けられた複数の第1のコンタクトと、絶縁膜の表面からゲート配線の各領域に共通に接続された第2のコンタクトと、を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを向上可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、半導体基板上に形成される検査用トランジスタおよび製品用トランジスタのソースおよびドレインを活性化させるアニール処理を行うアニール工程と、アニール工程後における検査用トランジスタのゲート、ソースおよびドレインをシリサイド化させる検査用サリサイド工程と、検査用サリサイド工程後における検査用トランジスタの特性を測定する測定工程と、測定工程によって測定された特性と所望の特性との差分とに基づいて製品用トランジスタの特性を所望の特性へ近付ける特性調整アニール処理を行う特性調整アニール工程と、特性調整アニール工程後における製品用トランジスタのゲート、ソースおよびドレインをシリサイド化させる本サリサイド工程とを含む。

(もっと読む)

半導体素子の検査方法及び半導体検査装置

【課題】電界効果トランジスタにおける電流コラプスの発生の有無を迅速に判定する。

【解決手段】電界効果トランジスタ101をオン状態にするとともに、電界効果トランジスタ101のドレインに第1電圧を印加した状態において、電界効果トランジスタ101の第1オン抵抗を算出する第1の工程と、電界効果トランジスタ101をオフ状態にし、前記第1電圧よりも大きい第2電圧を、電界効果トランジスタ101のドレインに印加する第2の工程と、電界効果トランジスタ101をオン状態にするとともに、電界効果トランジスタ101のドレインに前記第2電圧を印加した状態において、電界効果トランジスタ101の第2オン抵抗を算出する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGパターンを有する半導体基板を用いて、ダイシング時の不良を抑制した半導体装置を提供する。

【解決手段】ダイシングにより半導体チップ2aに個片化される、または個片化された半導体基板と、半導体基板上に形成された層間絶縁層と、層間絶縁層内に設けられ、半導体チップ2aの周縁部に沿って形成されたシールリング5aと、一端がシールリング5aに接続し、他端が半導体チップ2aの外周の端面に向けて延在するTEG配線7を備えている。

(もっと読む)

半導体装置製造工程におけるチャージアップ検出方法

【課題】絶縁ゲート型電界効果トランジスタを製造する途中で、絶縁ゲート型電界効果トランジスタに悪影響を与えるチャージアップが生じているのを検出することができる半導体装置製造工程におけるチャージアップ検出方法を提供する。

【解決手段】絶縁体10上の半導体層12に、素子分離領域18によって素子分離された絶縁ゲート型電界効果トランジスタ用の第1の活性層16と検出素子用の第2の活性層16とを形成し、前記第1の活性層と第2の活性層上に第1および第2の絶縁膜22をそれぞれ形成し、少なくとも第1および第2の絶縁膜22上に第1および第2の導体24をそれぞれ形成し、第1および第2の導体24に電荷が供給される処理を行い、その後、第2の活性層16の形状を検出する。

(もっと読む)

評価素子、半導体装置および半導体装置の製造方法

【課題】活性領域と素子分離絶縁膜との段差を精度よく評価する技術を提供する。

【解決手段】半導体基板10に形成されたトレンチに埋め込まれた素子分離絶縁膜18と、前記半導体基板10に形成され不純物を含む活性領域36と、前記活性領域36と前記素子分離絶縁膜18との間の段差を測定するための前記活性領域36の幅W1〜W7が異なる複数の段差測定部52a〜52gと、を具備する評価素子によって前記段差を測定し、この測定結果に基づき、ゲート寸法を調整する。

(もっと読む)

半導体装置の評価方法

【課題】pチャネル型電界効果トランジスタのNBTIをウエハ面内において漏れなく評価することにより、信頼性評価の充実を図り、信頼性の高いpチャネル型電界効果トランジスタを提供する。

【解決手段】劣化過程、回復過程、および再劣化過程をストレス試験の1サイクルとし、1つのpチャネル型電界効果トランジスタに対して上記1サイクルを複数回繰り返し行い、複数の劣化過程におけるしきい値電圧の劣化量または動作電流の劣化量を抽出して回復レス劣化評価を行い、複数の回復過程におけるしきい値電圧の劣化量および動作電流の劣化量を抽出して回復レス劣化評価を行う。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】保護ダイオードの有無に拘らず、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】テストエレメントグループ10において、電界効果型トランジスタからなるn個の素子DUT1〜DUTnが規則的に配置されている。ドレイン線DLおよびソース線SLがそれぞれ、全ての素子DUT1〜DUTnに対して共通化されており、その一方で、ウェル線WLが素子DUT1〜DUTnごとに1つずつ設けられている。選択対象の素子(選択素子DUTx)の素子特性を測定する際には、基板バイアス効果を利用して、非選択対象の素子(非選択素子DUTy)に流れるオフリーク電流を小さくする。

(もっと読む)

素子評価用半導体集積回路

【課題】 インバータ等の論理ゲートからなる大規模なゲートチェーンを有し、そのゲートチェーンにおいて不良の原因となっている論理ゲートを特定することが容易な素子評価用半導体集積回路を提供する。

【解決手段】 多段接続された複数の論理ゲートからなるゲートチェーンと、モニタ信号線MONと、ゲートチェーンにおける各論理ゲートの出力ノードとモニタ信号線MONとの間に各々介挿され、当該モニタユニットMUaを指示する制御信号が与えられることにより、モニタ信号線MONに当該出力ノードの電圧に依存した信号を発生させる複数のモニタユニットMUaと、ゲートチェーンにおける複数の論理ゲートの出力ノードを順次モニタ対象とし、モニタ対象とする論理ゲートの出力ノードに接続されたモニタユニットを指示する制御信号を発生するモニタユニット選択手段を有する。

(もっと読む)

トランジスタ対の特性評価装置および特性評価方法

【課題】ソース電極を共通とするトランジスタ対の、各ドレイン電極から出力される電圧の差を評価するトランジスタ対の特性評価装置であって、その特性差を高精度でかつ簡便に測定できる特性評価装置および特性評価方法を提供することを課題とする。

【解決手段】2つの可変抵抗を有し、各可変抵抗の一方の端部は共通に接続され、他端部はそれぞれ各ドレイン電極に接続するドレイン端子を有し、各ドレイン端子の出力を測定する測定装置を有することを特徴とする。

(もっと読む)

半導体装置の評価方法、評価装置、及びシミュレーション方法

【課題】RTNに関する絶縁膜の品質判定、製造工程の良否判定、回路設計などをより高精度に実施すること。

【解決手段】本発明に係る半導体装置の評価方法は、ゲート絶縁膜を有するMIS型FETを備える半導体装置の評価方法であって、複数のMIS型FETのRTNを測定し、RTNの測定結果に基づいて、ゲート絶縁膜中のトラップの位置、トラップのエネルギー、RTNの時定数、及びRTN振幅のうち少なくとも2つパラメータを抽出し、当該2つのパラメータの相関関係を求めるものである。

(もっと読む)

検査方法及び装置

【課題】検査対象の電気特性を測定する場合に、検査対象の電気特性に影響を与えることなく、SEM画像の高倍率化、高分解能化及びリアルタイム性を実現する。

【解決手段】試料上の検査対象における目標位置の像を含む高画質且つ高倍率の第1の画像を取得する。次に、試料上の検査対象における目標位置の像とプローブの像を含む低画質且つ低倍率の第2の画像を取得する。次に、第2の画像に第1の画像データを組み込むことによって、第2の画像の倍率と同一の倍率の粗寄せ観察用の画像を生成する。プローブが検査対象における目標位置に近接するまで、粗寄せ観察用画像の生成を繰り返す。

(もっと読む)

半導体素子の特性測定方法および半導体装置の製造方法

【課題】ウェハの厚み方向他方側の電極に、ウェハの厚み方向一方側から通電することができ、半導体素子の電気的特性を精度良く測定することができる半導体素子の特性測定方法およびそれを用いる半導体装置の製造方法を提供する。

【解決手段】半導体ウェハ1の厚み方向一方X1側の表面部に形成されたゲート電極およびソース電極から離隔して、電極接触部14が半導体ウェハ1の厚み方向他方X2側でドレイン電極2と接触し、端子接触部12が半導体ウェハ1の厚み方向一方X1側に露出するように、半導体ウェハ1の端部に測定用端子10を配置する。測定用端子10の端子接触部12にプローブ端子15を接触させるとともに、ゲート電極およびソース電極にプローブ端子を接触させて、MOSFETの電気的特性を測定する。

(もっと読む)

不純物量予測方法及び不純物量予測装置

【課題】製品ウェハにおけるトランジスタ寸法での、金属不純物量を予測可能とする不純物量予測方法を提供する。

【解決手段】不純物量予測方法は、半導体基板上に設けられたトランジスタのパターンを用いてTDDB寿命及び反転膜厚として第1寿命及び第1膜厚を測定するステップ(S1)と、予め求められたゲート絶縁膜中の不純物量とTDDB寿命及び反転膜厚との関係と、測定された前記第1寿命及び前記第1膜厚とに基づいて、前記半導体基板内のゲート絶縁膜中の不純物量を予測するステップ(S2)とを具備する。

(もっと読む)

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】小さな面積でより多くの素子を搭載することができ、さらに、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】各グループGNにおいて、全ての入力端子INが共通のドレインソース線DSLに接続されている。各グループGNにおいて、全ての出力端子OUTが入力端子INに非接続のドレインソース線DSLに、他の出力端子OUTと非共有で接続されている。さらに、一のグループGNにおける共通のドレインソース線DSLと、他のグループGNにおける共通のドレインソース線DSLとが互いに異なっている。

(もっと読む)

1 - 20 / 182

[ Back to top ]