Fターム[4M118EA01]の内容

Fターム[4M118EA01]の下位に属するFターム

Fターム[4M118EA01]に分類される特許

161 - 180 / 2,074

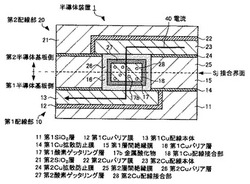

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

固体撮像装置および電子機器

【課題】固体撮像装置において、光学的な混色やMgフレアを抑制するとともに、感度を向上させる。

【解決手段】半導体基板に設けられ、フォトダイオードを含む画素が複数配列された画素領域と、半導体基板の一方の板面側に設けられる配線層と、画素領域に配列される複数の画素の各画素に対応して設けられる複数のカラーフィルタに区分されるカラーフィルタ層と、半導体基板とカラーフィルタ層との間にて、互いに隣接する画素間の境界部分に設けられる画素間遮光部と、を備え、複数の画素は、カラーフィルタの色により、互いに隣接する画素として、カラーフィルタの色が互いに異なる異色画素の組み合わせ、およびカラーフィルタの色が互いに同じである同色画素の組み合わせを有し、画素間遮光部は、異色画素の組み合わせにおける前記境界部分に偏在する。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体基体同士が張り合わされた構成を有する半導体装において、接合精度の向上を可能とする。

【解決手段】第1半導体基体31と、第2半導体基体45とを備え、第1半導体基体31の第1主面31A側と、第2半導体基体45の第1主面45A側が接合されている。そして、第1半導体基体31の第1主面31A側、第2半導体基体45の第1主面45A側、第1半導体基体31の第2主面31B側、及び、第2半導体基体45の第2主面45B側から選ばれる少なくとも1つ以上に形成されている反り補正層13,14を備える半導体装置79を構成する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】固体撮像装置の画質の向上を図る。

【解決手段】本実施形態の固体撮像装置は、半導体基板10の撮像領域21内に設けられ、少なくとも1つの光電変換素子30を含む単位セルと、半導体基板10の黒基準領域29内に設けられ、少なくとも1つの光電変換素子40を含む黒基準セルと、半導体基板10上の絶縁膜71を介して単位セルの上方に設けられるレンズ60と、絶縁膜71を介して黒基準セルの上方に設けられ、表面に凹凸部62を有する第1の遮光膜61と、を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】裏面照射型CMOSイメージセンサーのリーク電流を抑制可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、半導体基板の上にエピタキシャル半導体層4をエピタキシャル成長させる工程と、前記エピタキシャル半導体層4に光電変換部を形成する工程と、前記光電変換部の形成後に、前記エピタキシャル半導体層4の上に配線層を形成する工程と、前記配線層の上に支持基盤23を接合する工程と、前記接合の後に、前記半導体基板を前記接合とは反対面側からエッチングする工程を含む。半導体装置の製造方法は、前記エッチングする工程の後に、前記エピタキシャル半導体層4の前記反対面側にアモルファスSi層26を形成する工程と、前記アモルファスSi層の上に、反射防止膜、カラーフィルタを順に形成する工程を含む。

(もっと読む)

固体撮像素子およびその製造方法

【課題】クロストークを防止するために設けられた区画層を有する固体撮像素子において、高画質化のために受光部サイズが小型化された場合であっても、感度特性の劣化を抑制し、良好な画質の実現を図ることを目的とする。

【解決手段】半導体基板11と、半導体基板11内に行列状に配置され、光電変換する複数の受光部12と、半導体基板11の上側に配置され、受光部12それぞれの上方に対応する部位に開口を有し、前記開口と開口の間の部位により受光部12の上方を受光部12毎に区画する区画層20と、前記開口内部に配されたカラーフィルタ層24と、を備え、区画層20は、区画本体層21と、区画本体層21上に積層された密着層22および金属層23とで構成され、最上位に配された金属層23は、金属から成る。

(もっと読む)

固体撮像装置およびカメラ

【課題】出力部の変換効率を向上させて、高感度の固体撮像装置を提供する。

【解決手段】固体撮像装置は、信号電荷を生成する複数の受光部102と、前記信号電荷を転送する転送部104と、転送部104から転送される信号電荷を蓄積する浮遊拡散層22と、浮遊拡散層22の信号電荷を電圧に変換する出力部23と、転送部22と出力部23とに接する分離領域とを備え、分離領域は、第1導電型不純物を含む第1分離領域241と、第1分離領域241よりも高濃度の第1導電型不純物を含む第2分離領域242を有し、前記第1分離領域は、前記浮遊拡散層に隣接する。

(もっと読む)

固体撮像装置

【課題】グローバル電子シャッター機能を備えながら、高い感度および高い画質を有するMOS型の固体撮像装置を提供する。

【解決手段】固体撮像装置は、半導体基板101、フォトダイオード105、接続ダイオード175、蓄積ダイオード106、オーバーフロードレイン109を有する。フォトダイオード105は、半導体基板101内におけるZ軸方向の上主面側に、当該主面に沿う状態で、且つ、互いの間に間隔をあけた状態で二次元形成されている。蓄積ダイオード106は、半導体基板101内におけるZ軸方向の下主面側に、設けられている。オーバーフロードレイン109も、半導体基板101内におけるZ軸方向の下主面側に、設けられている。フォトダイオード105に接続された接続ダイオード175は、蓄積ダイオード106およびオーバーフロードレイン109の各々に対し、ゲートを介して配されている。

(もっと読む)

固体撮像装置

【課題】画質の劣化を抑制する。

【解決手段】本実施形態の固体撮像装置は、フォトダイオード形成領域50内に設けられ、少なくとも1つの不純物層55を含むフォトダイオード5と、フォトダイオード形成領域50内に設けられ、フォトダイオード5の下方に設けられる空洞59とを、含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】グレーティング技術によりポテンシャルを形成する場合に、ポテンシャルのばらつきを抑制することを目的とする。

【解決手段】

半導体装置の製造方法は、半導体基板上にレジスト層を形成する工程と、グレーティングマスクを用いてレジスト層を露光する工程と、 露光されたレジスト層を現像し、勾配を有するレジストマスクを形成する工程と、レジストマスクを介して、半導体基板にイオンを注入することで不純物領域を形成する工程と、を具備する。イオンを注入する工程において、520keV以上でイオン注入を行う。

(もっと読む)

イメージセンサ

【課題】画像処理速度が速いとともに、画像間の境界が曖昧になるのを抑制することのできるイメージセンサを提供する。

【解決手段】入射された伝播光を電気信号に変換する複数の画素と、複数の画素のうちの少なくとも一部の画素間を接続するように設けられ、入射された伝播光を近接場光に変換するとともに近接場光を伝播する近接場光導波路と、を備えている。

(もっと読む)

CMOSイメージ・センサー及びその製造方法

【課題】n型イオン注入領域を二重に形成することにより、素子の均一度の低下なく、良好な電荷移送効率を確保できるCMOSイメージ・センサー及びその製造方法を提供する。

【解決手段】素子分離膜22が形成された半導体基板21上にトランスファー・ゲート23を形成し、トランスファー・ゲート23に整列するフォトダイオード用第1のn型イオン注入領域24を形成し、フォトダイオード用第1のn型イオン注入領域24を含むフォトダイオード用第2のn型イオン注入領域24を形成し、フォトダイオード用第1のn型イオン注入領域24と一部が重なるフォトダイオード用p型イオン注入領域26を、半導体基板21の表面とフォトダイオード用第1のn型イオン注入領域24との間に形成し、トランスファー・ゲート23の両側壁にスペーサ27を形成し、トランスファー・ゲート23の他側にフローティング拡散領域28を形成する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、及び電子機器

【課題】縦型の転送トランジスタを備える固体撮像装置において、飽和電荷量のばらつきが低減され、歩留まりの向上が図られた固体撮像装置を提供する。また、その固体撮像装置を用いた電子機器を提供する。

【解決手段】基板30と、基板30に形成され、入射した光の光量に応じた信号電荷を生成、蓄積する光電変換部PDを備える。また、光電変換部PDの深さに応じて基板30の一方の面側から深さ方向に形成された溝部29に埋め込まれて形成された縦型の転送ゲート電極20を備える。そして、縦型の転送ゲート電極20を備える固体撮像装置において、光電変換部PDに蓄積された信号電荷をオーバーフローさせるオーバーフローパス27が、転送ゲート電極20の底部に形成されている。

(もっと読む)

高アスペクト比のトレンチ構造を有する半導体デバイスの製造方法

【課題】開口部が数μm、アスペクト比が5以上のトレンチ壁面に高濃度の不純物がドーピングされた縦型pn接合を形成する技術を確立する。

【解決手段】開口部の最小寸法が10μm以下、アスペクト比5以上、かつ壁面の凹凸が0.2μm以下のSiトレンチ壁面に対し不純物をドープし、さらに、不純物がドープされたトレンチ壁面を、900℃以上の熱処理でリフローが生じるSiO2膜により被覆し、このSiO2膜を固体拡散源としたトレンチ壁面にpn接合膜を形成する高アスペクト比のトレンチ構造を有する半導体デバイスの製造方法。前記ドープに先立ち、トレンチ壁面の熱酸化処理を行い、この熱酸化処理によって形成された熱酸化膜を除去する処理によりトレンチ壁面の凹凸を0.1μm以下に抑える。

(もっと読む)

撮像装置及び製造方法

【課題】複数の撮像素子をタイル状につなぎ合わせた大面積撮像装置において、ダイシング後の切断面に欠損が無く、画素配列に欠落を生じない素子端部の構造及びその製造方法を提供する。

【解決手段】つなぎ合わせ端部の受光領域の構造が素子分離領域の一部であって密接する互いの素子分離領域の幅の合計がつなぎ合わせ領域以外の素子分離領域の幅と同等もしくはそれよりも狭く形成する。

(もっと読む)

光電変換装置およびその製造方法

【課題】回路層に対するIa族元素の拡散を防止しながら光電変換効率を向上する。

【解決手段】回路層20は、基板10の面上に形成されてトランジスター12を含む。光電変換素子14は、第1電極41および第2電極42との間に介在するカルコパイライト型半導体の光電変換層43を含む。供給層34は、回路層20と光電変換層43との間に形成されてIa族元素を含む。光電変換層43に対するIa族元素の拡散で光電変換効率が向上する。保護層32は、供給層34と回路層20との間に形成されて回路層20に対するIa族元素の拡散を防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、基板の表側に配置される回路素子及び導電線と、基板の裏側に配置される電子回路との間に生じる寄生容量を低減するための技術を提供する。

【解決手段】基板と、基板の上に配置された画素アレイと、基板の上に配置され、画素アレイの回路素子に電気的に接続された第1導電パッドと、電子回路を接続するために基板の下に配置された第2導電パッドと、基板と第1導電パッドとの間に配置された絶縁層と、基板と絶縁層との間に配置された第3導電パッドと、絶縁層を貫通する第1コンタクトホールを通り、第1導電パッドと第3導電パッドとを接続する第1導電部材と、基板を貫通する第2コンタクトホールを通り、第2導電パッドと第3導電パッドとを接続する第2導電部材とを備える半導体装置が提供される。

(もっと読む)

光電変換装置、撮像システム及びその製造方法

【課題】 フローティングディフュージョン部の容量の増大を抑制することが可能な光電変換装置を提供する。

【解決手段】 光電変換素子と、フローティングディフュージョン部と、転送トランジスタと、増幅トランジスタとが配された半導体基板と、第1の配線層と、第2の配線層とを含む複数の配線層と、を有する光電変換装置において、転送トランジスタのゲート電極と、前記第2の配線層とがスタックコンタクト構造で接続されている。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法および撮像装置

【課題】暗電流を抑制することができる固体撮像素子を提供する。

【解決手段】固体撮像素子は、光電変換が行われるフォトダイオードが形成された有効領域と、遮光膜により遮光された光学的黒領域とが形成された半導体基板と、前記有効領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第1の膜と、前記遮光領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第2の膜と、を備え、前記第1の膜が有する層の数が前記第2の膜が有する層の数と異なる。

(もっと読む)

固体撮像装置

【課題】接合リーク電流が生じる原因となるシリサイド材料のスパイクを防止し、画像欠陥である白キズ及びRTSノイズを低減できるようにする。

【解決手段】固体撮像装置は、シリコンからなる半導体基板の上に形成され、入射光を光電変換するフォトダイオード、フォトダイオードで得られた信号を転送するための転送トランジスタ、及び信号を増幅するための画素内トランジスタを含む複数の単位画素11が一次元状又は二次元状に配列された感光領域10を備えている。画素内トランジスタは、ゲートパターン13とシリサイドが形成された拡散層12とを含み、拡散層12の表面の少なくとも一辺の近傍にダミーパターン14が形成されている。

(もっと読む)

161 - 180 / 2,074

[ Back to top ]