Fターム[4M119BB20]の内容

MRAM・スピンメモリ技術 (17,699) | 記憶素子の種類 (1,713) | その他の記憶素子 (116)

Fターム[4M119BB20]に分類される特許

101 - 116 / 116

磁気抵抗メモリ装置

【課題】

磁壁を安定に移動することができる多値磁気メモリ装置を提供する。

【解決手段】

磁気抵抗メモリ装置は、

磁化方向が第1の方向に固定された固定磁化層と、

前記固定磁化層上に形成されたトンネルバリア絶縁層と、

前記トンネルバリア絶縁層を介して前記固定磁化層に対向する自由磁化層であって、前記トンネルバリア絶縁層に接する活性部と、前記活性部両側に配置された2つの待機部とを有し、内部に渦型構造の磁壁と該磁壁の一方側で前記第1の方向に磁化した第1の磁区と該磁壁の他方側で前記第1の方向と逆の第2の方向に磁化した第2の磁区とを含み、前記活性部、前記2つの待機部のそれぞれに対応して前記磁壁をピン止めする機能を有する3つのピン止め構造を備えた自由磁化層と、

を有する。

(もっと読む)

データストレージ装置及びその方法

データがナノワイヤにおける単磁区において符号化される種類のシリアル磁気大容量ストレージ装置及び関連のデータストレージ方法。本発明において、磁壁ピン止め部位を形成するために、その全長方向に沿って多数のノッチ(12)を備えるナノワイヤ(10)が提供される。ノッチは、加熱電極によって群(A、B、C)でアドレス指定される。ナノワイヤに沿った動作磁界(I−1)の配列及び逆配列に同期して、ヘッド−ヘッド及びテイル−テイル磁壁(16、18)をホストするノッチを交互に加熱することにより、磁区(14)は、加熱及び交互の動作磁界の協調作用下で、1ノッチ間分だけ磁区が延長され、ナノワイヤに沿って移動される。相互接続及び製造の観点から、この方式は、基板の平面からほぼ制限なしに拡縮され、何百あるいは何千もの積層したナノワイヤ層を提供することができ、格納された情報の非常に濃い3Dネットワークを実現できる。  (もっと読む)

(もっと読む)

磁気抵抗効果素子を用いたメモリおよびその駆動方法

【課題】クロスポイント型のMRAMは回りこみ電流による誤読出しを抑制するために選択トランジスタやダイオードをセル内に必要とするため、セルを小型化することが困難であった。また、1方向のみの駆動電流で書き換えを行うことが困難であった。

【解決手段】非対称性および非線形性を有する磁気抵抗効果素子により、磁気抵抗効果素子のみメモリセルを構成できセル面積の小型化とクロスポイント型のメモリを実現する。さらに、磁気抵抗効果素子の構成と駆動電流方向の組み合わせを適正化することで1方向のみの駆動電流で書き換え可能な不揮発メモリを実現する。

(もっと読む)

磁気抵抗効果素子,および磁気抵抗効果素子の製造方法

【課題】ピン層,スペーサ層,フリー層の積層構造を用いない磁気抵抗効果素子を提供する。

【解決手段】磁気抵抗効果素子が,磁化方向が実質的に固着された第1の磁性層と,前記第1の磁性層上に配置され,かつ酸化物,窒化物,酸窒化物,金属のいずれか1つからなる薄膜層と,前記薄膜層上に配置され,かつ磁化方向が実質的に固着された第2の磁性層と,を具備する。薄膜層が外部磁場を検知することで,磁気抵抗効果素子の磁気抵抗が変化する。

(もっと読む)

磁気メモリ、及びその駆動方法

【課題】高記録密度の磁気メモリを実現する。

【解決手段】情報記録媒体としての磁性細線1に対し、リザーブ領域95の長さに等しい長さで、等間隔に記録素子16a〜16dまたは再生素子17a〜17dを配置している。例えば情報の記録時に、端子21aと端子21cとを選択して電圧を印加し、記録領域94a内の磁壁をリザーブ領域95に向かって移動させると、リザーブ領域95の長さ分、磁壁を移動させる間に、全磁区が、記録素子16aおよび16bのどちらかを通過する。情報の再生時についても、記録領域94bの磁区についても、同じことがいえる。したがって、記録領域94a・94bの全磁区の記録再生を可能としながら、従来より遥かに高密度の記録再生を可能にする。

(もっと読む)

ナノ磁気メモリ素子とその製造方法

【課題】セルサイズの負担が小さいメモリ素子を具現して集積度を向上させることができる。ナノ磁気メモリ素子を提供する。

【解決手段】ナノ磁気メモリ素子のナノワイヤを経て第1電極から第2電極に流れるワード線電流によって磁性ナノドットが摂動された後に再配列される過程で形成される誘導電流の大きさを制御し、前記ナノ磁気メモリセルに複数のデータを書き込み/読み出すことを特徴とするナノ磁気メモリ素子。

(もっと読む)

半導体記憶装置及びその製造方法並びにそのデータ書込み方法及びデータ読出し方法

【課題】高速性及び記憶保持特性に優れた半導体記憶装置及びその製造方法並びにそのデータ書込み方法及びデータ読出し方法を提供する。

【解決手段】半導体記憶装置1は、半導体基板22上に形成された下部電極55と、下部電極55上に形成され、電気磁気効果を示す電気磁気効果層53と、電気磁気効果層53上に形成された上部電極51と、上部/下部電極51、55間に電圧を印加して所定方向に揃えられた電気磁気効果層53の磁化方向に基づいて残留磁化の方向が決まる磁気記憶層57とを有している。

(もっと読む)

改善された接合形態を有するナノ接合

【課題】接合ワイヤーの初期スピンモーメント方向に関係なく接合ワイヤー間の磁壁の厚さが一定のナノ接合を提供する。

【解決手段】本発明は、2個の接合ワイヤーが接合されるナノ接合であって、接合される接合領域を含む接合面が四分円形を有する第1の接合ワイヤーと、前記第1の接合ワイヤーと前記接合領域で接合し、前記第1の接合ワイヤーの四分円の接合面と原点対称する四分円形の接合面を有する第2の接合ワイヤーとを含むことを特徴とする。

(もっと読む)

電界制御磁性素子及び電界制御磁気メモリ素子

【課題】 電界制御磁気素子及び電界制御磁気メモリ素子に関し、常磁性元素の強磁性化或いは強磁性元素の常磁性化を室温において電気的に制御する。

【解決手段】 電極1/絶縁膜2/遷移金属からなる導電体層3の積層構造を有するとともに、導電体層3に絶縁膜2を介して電圧を印加してフェルミ準位の位置を移動させることによって、常磁性−強磁性遷移或いは強磁性−常磁性遷移を制御する。

(もっと読む)

磁気メモリ素子

【課題】メタルラインを利用し、情報の書き込みと読み取りとの機能を具現した磁気メモリ素子を提供する。

【解決手段】プラスチック基板上で磁化方向がスイッチングされる連続したマグネチックドメインD1〜D8が形成され、並んで配置された複数の第1メタルライン100と、第1メタルライン100と直交して配置され、第1メタルライン100を覆うトンネルを形成する複数の第2メタルライン200と、第1メタルライン100に連結され、マグネチックドメインD1〜D8をドラッギングする電流を供給する第1入力部500と、第2メタルライン200に連結され、トンネル内のマグネチックドメインD1〜D8の磁化方向をスイッチングする電流を印加する第2入力部600と、第2メタルライン200に連結され、トンネルを通過するマグネチックドメインウォールによる起電力をセンシングするセンシング部700とを具備する磁気メモリ素子である。

(もっと読む)

分子量子メモリ

分子量子メモリを実現する装置、システム及び方法が開示される。一実施形態において、偏極電子源(104)及び逆極性の偏極電子源(106)が、プローブアセンブリの少なくとも1つのプローブ先端(117、119)に選択的に結合される。そして、この少なくとも1つのプローブ先端は、偏極電子電流源(104、106)から選択的に得られた時間変化する偏極電子電流を用いて情報が分子に書き込まれ得るように、分子に電気的に結合される。  (もっと読む)

(もっと読む)

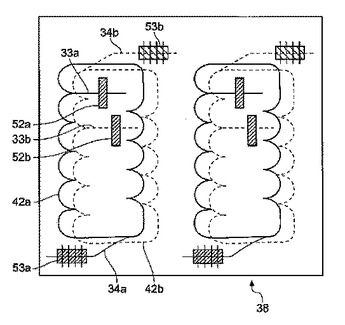

ナノ構造磁気抵抗ネットワークおよび磁界検出方法

【課題】複数の磁気抵抗素子のパラメータを安定化することによって、磁気検出特性が容易に適合できる磁気抵抗ネットワークを提供する。

【解決手段】複数の磁気抵抗素子(10)を備えるタイプの、磁界(Hext,Hp)に応答する磁気抵抗ネットワークであって、1つ又はそれ以上の磁気抵抗素子(10)は、ナノ狭窄の形状を持つ少なくとも1つの磁気抵抗素子を備え、ナノ狭窄は、少なくとも2つの磁気材料からなるパッド(12,13)を備え、パッドは、互いに実質的に反対方向に配向した個々の磁化(16,17)に関連付けられ、ナノチャネル(11)を通じて接続されており、ナノチャネル(11)は、ドメイン壁(15)を配置することが可能であり、ドメイン壁は、ナノ狭窄の電気抵抗を、前記ナノチャネル(11)に関して、センサデバイスに形成されたドメイン壁(15)の位置の関数として決定する。

(もっと読む)

新規な相変化磁性材料

本発明は、相変化材料成分及び強磁性材料成分を含む、情報記録用媒体において使用される相変化磁性複合材材料に関連し、この場合、前記材料は磁気効果及び相変化効果の両方を示し、光学媒体、相変化ランダムアクセスメモリ(PCRAM)デバイス、磁気ランダムアクセスメモリ(MRAM)デバイス、固体メモリデバイス、センサーデバイス、論理デバイス、認知デバイス、人工ニューロンネットワーク、三レベルデバイス、制御デバイス、SOC(システムオンチップ)デバイス及び半導体のために使用可能である。 (もっと読む)

メモリアクセス

磁気論理装置は、電気回路用の一般的に平面的な第1基板と、前記第1基板上に積層された配置で形成される、磁気回路用の一般的に平面的な複数の第2基板とを有することができる。各々の第2基板は、その上に磁気回路が形成されており、各々の磁気回路は、複数の論理素子、データ書き込み素子及びデータ読み取り素子を有することができる。前記各々の磁気回路のデータ書き込み素子は、前記第1基板のそれぞれの磁気電気的書き込み素子の平面的な位置に相当することができ、前記各々の磁気回路のデータ読み取り素子は、前記第1基板のそれぞれの磁気電気的読み取り素子の平面的な位置に相当することができる。  (もっと読む)

(もっと読む)

MSMバイナリスイッチメモリ素子

【課題】クロスポイントメモリアレイにおける、回り込み電流に起因する読み取り障害を防止する。

【解決手段】メモリ素子100を用いてクロスポイントメモリアレイを作成する。メモリ素子100は、抵抗メモリ下部電極102、抵抗メモリ物質104、抵抗メモリ上部電極106、MSM下部電極108、半導体層110、MSM上部電極112がこの順に積層されてなる。ここで、MSM下部電極108、半導体層110、MSM上部電極112はMSMバイナリスイッチを形成する。MSMバイナリスイッチは、逆バイアス下において、高い抵抗値を示す。MSMバイナリスイッチと抵抗メモリ物質104が直列に接続された構成を有するメモリ素子100を用いて、クロスポイントメモリアレイを作成することにより、望ましくない方向に電流が流れるのを防ぐ。

(もっと読む)

カーボンナノチューブアレイをベースとするスペーサー層を有するスピントロニックデバイス及び該デバイスの製造方法

本発明は、配向されたカーボンナノチューブアレイから形成される層を利用するスピントロニックデバイスと、該デバイスを含むエレクトロニックデバイス(スピンバルブやスピントンネルジャンクション、スピントランジスタ等)とに関する。スピントロニックデバイスは、底部電極と、第一の強磁性層と、CNTアレイと、第二の強磁性層と、上部電極とを含む。 (もっと読む)

101 - 116 / 116

[ Back to top ]