Fターム[5B005KK13]の内容

階層構造のメモリシステム (9,317) | 適用環境 (907) | 要求元 (807) | CPU (641) | マルチCPU (447)

Fターム[5B005KK13]の下位に属するFターム

共有外部メモリを有するもの (262)

Fターム[5B005KK13]に分類される特許

41 - 60 / 185

処理ユニットのローカルメモリ読み出し

【解決手段】

処理ユニットのローカルメモリに対する効率的な読み出しを可能にするためのシステム、装置及び方法がここに開示される。ある実施形態においては、処理ユニットは、インタフェース及びバッファを含む。インタフェースは、(i)他の処理ユニットのローカルメモリの領域におけるデータの一部分に対する要求を送ると共に(ii)要求に応答して領域からの全てのデータを受信するように構成される。バッファは、他の処理ユニットのローカルメモリの領域からのデータを記憶するように構成される。

(もっと読む)

汎用使用のための処理ユニット内部メモリ

【解決手段】

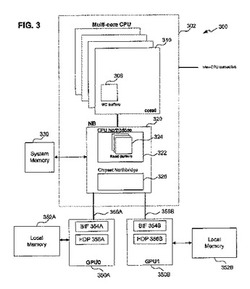

汎用使用のための内部メモリを有するグラフィクス処理ユニット(GPU)及びそのアプリケーションがここに開示される。そのようなGPUは、第1の内部メモリと、第1の内部メモリに結合される実行ユニットと、第1の内部メモリを他の処理ユニットの第2の内部メモリに結合するように構成されるインタフェースと、を含む。第1の内部メモリは積層ダイナミックランダムアクセスメモリ(DRAM)又は埋め込みDRAMを備えていてよい。インタフェースは第1の内部メモリをディスプレイデバイスに結合するように更に構成されていてよい。GPUは第1の内部メモリを中央処理ユニットに結合するように構成される別のインタフェースを含んでいてもよい。またGPUはソフトウエアにおいて具現化され且つ/又はコンピューティングシステム内に含まれていてよい。

(もっと読む)

投機的バージョニング・キャッシュにおけるチェックポインティングのための方法、コンピュータ・プログラム、およびデータ処理システム(投機的バージョニング・キャッシュにおけるチェックポインティング)

【課題】 データ処理システム(100)の投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1030)を生成するための機構を提供する。

【解決手段】 機構は、データ処理システム(100)内でコードを実行し、コードは、投機的バージョニング・キャッシュ(310、1210)内のキャッシュ・ラインにアクセスする。さらに機構は、投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1030)を生成する必要性を示す第1の条件が発生するかどうかを決定する(1350)。チェックポイント(1310)は、投機的キャッシュ・ラインに対応するキャッシュ・ラインへの変更のロールバックを必要とする第2の条件の発生に応答して、非投機的となる、投機的キャッシュ・ラインである。機構は、第1の条件が発生した旨の決定に応答して、投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1310)も生成する。

(もっと読む)

キャッシュメモリ結合性を伴うプロセッサコアの割当

複数のプロセッサコアとプロセッサコアの少なくともいくつかによって共有されるキャッシュメモリとを有するマルチコアプロセッサに関係する技法を全体的に説明する。マルチコアプロセッサを、キャッシュメモリ結合性のそれぞれのレベルを処理コアのそれぞれに別々に割り当てるように構成することができる。  (もっと読む)

(もっと読む)

マルチプロセッサ仮想マシン環境においてアドレス変換をサポートする方法及び装置

【課題】ゲスト変換データ構造におけるどのエントリが仮想マシンによって修正されたかを判定する。

【解決手段】判定は、シャドウ変換データ構造におけるエントリに関連付けられた属性、及び仮想マシン・モニタによってメンテナンスが行われるシャドウ変換データ構造から抽出されたメタデータに基づいて行われる。方法は、ゲスト変換データ構造における修正されたエントリに対応するシャドウ変換データ構造におけるエントリを、ゲスト変換データ構造における修正されたエントリと同期化させる工程と、アクティブ・エントリ・リストにおける各エントリを複数のプロセッサの何れが保有するかを識別するシャドウ変換データ構造における対応するエントリに関連付けられた属性に少なくとも部分的に基づいて、アクティブ・エントリ・リストにおいてどのエントリを保つかを判定する工程とを含む。

(もっと読む)

プリフェッチ・モジュールを備える信号処理システムおよび集積回路、並びにそのための方法

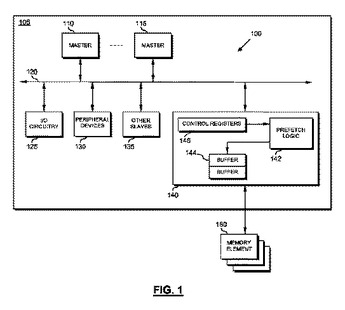

信号処理システム(100)は、少なくとも1つのマスタ・デバイス(110、115)と、少なくとも1つのメモリ素子(160)とを備え、さらに、少なくとも1つのマスタ・デバイス(110、115)から少なくとも1つのメモリ素子(160)へのメモリアクセス要求に応じて、少なくとも1つのメモリ素子(160)からのプリフェッチを実行するように構成されたプリフェッチ・モジュール(142)を備える。プリフェッチ・モジュール(142)は、少なくとも1つのマスタ・デバイス(110、115)からメモリアクセス要求を受信すると、メモリアクセス要求が関連するアドレスに少なくとも部分的に基づいて、そのメモリアクセス要求に関連する命令情報およびデータ情報の少なくとも一方のプリフェッチの許可を設定するように構成されている。  (もっと読む)

(もっと読む)

I/Oのための多重レベルアドレストランスレーションを含むI/Oメモリ管理ユニット及び計算負荷軽減

【解決手段】

I/Oデバイスによるシステムメモリへの要求を制御するように構成される入力/出力メモリ管理ユニット(IOMMU)は、システムメモリ内に記憶されるトランスレーションデータを用いてI/Oデバイス生成の要求に関連するアドレスをトランスレートするために2レベルのゲストトランスレーションを行い得る制御論理を含む。トランスレーションデータは、幾つかのエントリを有するデバイステーブルを含む。制御論理は、所与の要求を生成するI/Oデバイスに対応するデバイス識別子を用いることによって、その要求に対するデバイステーブルエントリを選択してよい。トランスレーションデータはまた、ゲストページテーブルのセットと、入れ子にされたページテーブルのセットとを含むI/Oページテーブルの第1のセットを含んでいてよい。所与の要求に対して選択されたデバイステーブルエントリは、ゲストトランスレーションテーブルのセットへのポインタを含んでいてよく、そして最後のゲストトランスレーションテーブルは、入れ子にされたページテーブルのセットへのポインタを含む。

(もっと読む)

キャッシュメモリ

【課題】少ないハードウェアコストで、マルチプロセス環境や仮想マシン利用環境にも適用可能なキャッシュメモリの分割管理技術を提供する。

【解決手段】コアID・RAM203は、メモリアクセス要求708により特定されるキャッシュブロックの各キャッシュウェイに対応させて、メモリアクセス要求の要求元を識別するためのコアIDを記憶する。置換コアID決定回路711及び置換ウェイマスク生成回路703は、キャッシュミスの発生時に、置換ウェイ候補709を決定する。LRU選択回路704は、置換ウェイ候補709から置換ウェイ指示情報710を選択して出力する。キャッシュ制御部718は、キャッシュミスが発生した場合に、コアID・RAM203に記憶されているコアIDを、メモリアクセス要求708に付加されたコアID702によって更新する。

(もっと読む)

周辺相互接続におけるI/O及び計算負荷軽減デバイスのための2レベルのアドレストランスレーションを用いるIOMMU

【解決手段】

コンピュータシステムのシステムメモリへのI/Oデバイスによる要求を制御するためのIOMMUは、制御論理及びキャッシュメモリを含む。制御論理は、I/Oデバイスからの要求において受信されるアドレスをトランスレートしてよい。要求が処理アドレス空間識別子(PASID)プレフィックスを伴うトランザクション層プロトコル(TLP)パケットを含む場合には、制御論理は2レベルのゲストトランスレーションを実行してよい。従って、制御論理は、ゲストページテーブルのセットにアクセスして、要求において受信されるアドレスをトランスレートしてよい。最後のゲストページテーブル内のポインタは、入れ子にされたページテーブルのセット内の第1のテーブルを指し示す。制御論理は、入れ子にされたページテーブルのセットにアクセスしてシステムメモリ内の物理ページに対応するシステム物理アドレス(SPA)を得るために、最後のゲストページテーブル内のポインタを用いてよい。キャッシュメモリは完了したトランスレーションを記憶する。

(もっと読む)

二重化情報処理システム及び同期化方法

【課題】ライトバック方式のキャッシュメモリを備えた2台の情報処理システムによって構成される二重化情報処理システムにおいて、通常処理の処理効率を低下させることなく、同期化に要する時間を短縮すると共に、同期化中および同期化後の処理能力を向上させる。

【解決手段】待機系情報処理システム200を二重化情報処理システムに組み込むために、動作系情報システム100と待機系情報処理システム200とを同期化させる際、キャッシュコピー手段300は、ライトバック方式の動作系キャッシュメモリ101の内容をライトバック方式の待機系キャッシュメモリ201にコピーし、主記憶コピー手段400は、動作系主記憶装置102の内容を待機系主記憶装置にコピーする。その後、動作系、待機系CPU103、203がタイミングを合わせて同一の処理を開始する。

(もっと読む)

ガベージコレクション中の分散キャッシュの可用性

ガベージコレクション中の分散キャッシュへのアクセスを管理する技法について、本明細書に記載する。ガベージコレクションが、ノードに関して実施されるべきであるとき、ノードは、一次状態にある、ノードに含まれるデータモジュール(複数可)のインスタンスを二次状態に置くことを要求する要求をデータマネージャに送り得る。データマネージャは、データモジュール(複数可)の状態を二次状態に変えることができる。データマネージャは、別のノードに含まれるデータモジュール(複数可)の別のインスタンスの状態を一次状態に変えることができる。ガベージコレクションがノードに関して完了すると、ノードは、二次状態に置かれたデータモジュール(複数可)が一次状態に戻されることを要求する別の要求をデータマネージャに送ることができる。データマネージャは、こうしたデータモジュール(複数可)を一次状態に戻すことができる。  (もっと読む)

(もっと読む)

弱く順序付けられたストレージシステムにおいてメモリバリアコマンドを発行するための方法および装置

メモリアクセスの順序を強制するための効率的な技法が、説明される。メモリアクセス要求は、メモリバリアコマンドを生成するように構成されていないデバイスから受信される。サロゲートバリアは、メモリアクセス要求に応じて生成される。メモリアクセス要求は、読取り要求とすることができる。メモリ書込み要求の場合には、サロゲートバリアは、書込み要求が処理される前に生成される。サロゲートバリアはまた、読取り要求と同じアドレスに対する先行する書込み要求を条件としてメモリ読取り要求に応じて生成されることも可能である。コヒーレンシは、あたかもメモリバリアコマンドがメモリバリアコマンドを生成しないデバイスから受信されたかのように、階層的メモリシステムの内部で強制される。  (もっと読む)

(もっと読む)

画像処理装置

【課題】パターンメモリとして安価なメモリを使用する場合でも、効率的にパターンメモリからデータを読み出して処理を行うことができる画像処理装置を提供する。

【解決手段】キャッシュ制御回路52は、キャッシュメモリ51内のデータを対象とするリードリクエストが与えられた場合には、そのリードリクエストの対象であるデータをキャッシュメモリ51から読み出して出力し、キャッシュメモリ51に格納されていないデータを対象とするリードリクエストが与えられた場合には、当該データを含む1ページ分のデータをパターンROM204から読み出して、キャッシュメモリ51内の書き換え対象の記憶エリアに格納する。その際、リードリクエストの対象であるデータに連続するデータがキャッシュメモリ51内に格納されている場合に、その連続するデータが格納された記憶エリアを書き換え対象とする。

(もっと読む)

複数ノード間での通信方法、相互接続ポートおよび相互接続システム

【課題】複数のノード間での通信方法を開示する。

【解決手段】各ノードは、複数のプロセッサおよび相互接続チップセットを含み、第1のノード内のプロセッサからデータ要求を発行し、拡張ポート(またはスケーラビリティポート)を通してこのデータ要求を他のノードに渡す。また、データ要求に応答してメモリのアクセスを開始し、各ノード内の各プロセッサのプロセッサキャッシュをスヌープする。従って、該要求を発行するプロセッサを持つノード内の(あるいは別のノードの)プロセッサキャッシュまたはメモリ内のデータの格納場所を識別する。さらに、ルータシステムにて2つの直接結合されたノード間でデータを要求する方法と、相互接続システム内の3またはそれ以上のノード間でのデータ要求方法と、相互接続システム内のクロスケースの解消方法と、ノードを直接またはプロトコルエンジンを通して結合するための相互接続システムも開示する。

(もっと読む)

マルチプロセッサシステム

【課題】複数のプロセッサが周辺装置を共有しても、当該周辺装置に割り当てられたアドレス空間の重複に起因する誤動作を確実に防止し得るマルチプロセッサシステムを提供する。

【解決手段】マルチプロセッサシステム1は、複数のプロセッサとバスを介して接続されたアドレス変換部35を有する。アドレス変換部35は、複数のプロセッサのうちアクセス要求を発したプロセッサからのアドレス情報を共有メモリ空間内のアドレス情報に変換する。共有メモリ空間は、複数のプロセッサにそれぞれ対応する複数のアドレス領域を有している。アドレス変換部35は、アクセス要求を発した当該プロセッサからのアドレス情報を、当該プロセッサに対応する当該アドレス領域内のアドレス情報に変換する。

(もっと読む)

キャッシュにおけるウエイ割り当て及びウエイロックのための方法

【解決手段】

コンピュータシステムの共有キャッシュメモリにおけるデータ割り当てのためのシステム及び方法が検討される。共有セットアソシアティブキャッシュの各キャッシュウエイは、多重ソース、例えば1つ以上のプロセッサコア、グラフィクス処理ユニット(GPU)、入力/出力(I/O)デバイス、又は多重の異なるソフトウエアスレッドにアクセス可能である。共有キャッシュ制御器は、受信したメモリ要求の対応するソースに基いてキャッシュウエイの各々へのアクセスを別々に有効にし又は無効にする。1つ以上の構成及び状態レジスタ(CSR)が、共有キャッシュウエイの各々へのアクセス可能性を変更するために用いられるエンコードされた値を記憶している。CSR内に記憶される値を変更することによる共有キャッシュウエイのアクセス可能性の制御が、共有キャッシュ内の擬似RAM構造を作り出すこと、及び共有キャッシュが動作を継続している間におけるパワーダウンシーケンスに際して共有キャッシュのサイズを徐々に減少させることのために用いられ得る。

(もっと読む)

情報処理装置及びその制御方法

【課題】仮想メモリ領域を管理するオペレーティングシステムを実行する第1制御手段と第1制御手段と通信可能な第2制御手段を有する情報処理装置において、オペレーティングシステムにより管理される仮想メモリ領域の管理外の記憶手段に記憶されたデータ対して、第1制御手段が高速にアクセスする。

【解決手段】第1のCPU201は、キャッシュに対応する物理メモリの仕様情報を作成して第2のCPU221へ転送し(S904)、第2のCPU221は、その仕様情報に従って第1のCPU201が参照するキャッシュに対応する物理メモリ203に対して、デバイスに記録されているデータを転送する(S910)。

(もっと読む)

インターフェース装置、演算処理装置、インターフェース生成装置、および回路生成装置

【課題】演算装置同士を最小の記憶素子数で接続することが可能で、キャッシュメモリに記憶するデータ数を最小にしても確実にアドレス指定によるデータ転送を行えるようにする。

【解決手段】バッファに保存した書込みデータを書込みアドレスの順序に並び替えてストリームデータとして出力するストリーム変換装置130と、キャッシュメモリ140と、読出しに関するアドレス情報で指定されたデータがキャッシュメモリに既にロードされているかを判定し、ロードされていない場合には、ロード信号を出力し、ロードアドレスを出力する制御装置150と、ロードアドレスを用いて、読出しアドレスで指定されたデータがキャッシュメモリのどの記憶素子に保存されているかを求め、求めた値をキャッシュアドレスとしてキャッシュメモリに出力し、キャッシュメモリから入力されたキャッシュデータを読出しデータとして出力するアドレス変換装置160と、を有する。

(もっと読む)

キャッシュメモリ制御回路およびキャッシュメモリ管理方法

【課題】キャッシュメモリを有効に利用することができるキャッシュメモリ制御回路およびキャッシュメモリ管理方法を提供すること

【解決手段】本発明にかかるキャッシュメモリ制御回路は、セットアソシアティブ方式によって、メインメモリ71に記憶されるデータをキャッシュメモリに記憶するキャッシュメモリ制御回路である。キャッシュメモリに記憶するデータのメインメモリ71上のアドレスを示すアドレス情報を含み、セットアドレスのそれぞれに対応するエントリと、メインメモリ上のアドレス値であって、セットアドレス以外の値のいずれかに応じて、エントリ内をさらに区分してアドレス情報を格納するか否かを示し、エントリのそれぞれに対応するフラグを格納するキャッシュ情報格納部を備える。

(もっと読む)

情報処理装置及びプロセッサ並びに情報処理方法

【課題】情報処理装置について、装置構成を複雑化させることなく、動作の高速化と高信頼性を実現する。

【解決手段】本発明の一例である情報処理装置1は、プロセッサ2と、プロセッサ2に使用される不揮発性メモリ3と、プロセッサ2から不揮発性メモリ3への書き込みが発生した場合に、書き込み位置の重複回数を抑えるために当該書き込み位置がずれるように書き込みアドレスを発生させるアドレス発生手段16と、書き込みの新しさを表わす順序情報19を発生させる順序発生手段17と、アドレス発生手段16によって発生された書き込みアドレスに対して、順序発生手段17によって発生された順序情報19を対応付けて、書き込み情報21を記憶する書き込み制御手段18とを具備する。

(もっと読む)

41 - 60 / 185

[ Back to top ]