Fターム[5B018GA03]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | 試験、診断、検査 (262)

Fターム[5B018GA03]に分類される特許

81 - 100 / 262

メモリ制御装置及びその遅延量測定方法

【課題】 量産に適用されるような一般的なテスタでも遅延回路の遅延量の測定が可能なメモリ制御装置及びその遅延量測定方法を提供することを課題とする。

【解決手段】 本メモリ制御装置は、半導体記憶装置にデータを書き込むメモリ制御装置であって、入力信号を遅延させて出力する複数の遅延回路を有し、通常動作時に、前記複数の遅延回路は、互いに独立し、個々の遅延回路に入力される信号を個々に遅延して出力し、テスト動作時に、前記複数の遅延回路は、テスト用入力信号が全ての遅延回路を経由し、それぞれの遅延量の合計分だけ遅延するように接続され、遅延後の前記テスト用入力信号は、テスト用出力信号として、前記メモリ制御装置の外部に出力されていることを要件とする。

(もっと読む)

計算機システム

【課題】マルチコアCPUモジュールを搭載し、メインCPU上で動作しているアプリケーション処理を中断することなく、サブCPUでメモリ診断を行う計算機システムを得る。

【解決手段】計算機システム1は、マルチコアCPUモジュール4を搭載し、メインCPU2とサブCPU3上で、それぞれ、OS1とOS2が動作し、OS1はアプリケーション11と障害対処処理を行う障害対処処理部14を動作させ、OS2は、定期的にメモリ5の診断を行うメモリ診断処理部13と、メモリ診断処理部13の診断結果を障害対処処理部14に通知する障害監視処理部12とを動作させ、障害対処処理部14は、メモリ障害の通知を受けると、計算機システム1を停止させるようにする。

(もっと読む)

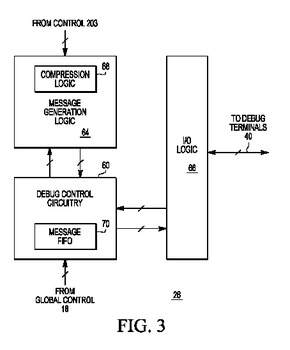

デバッグ用のアドレス変換トレースメッセージ生成

データ処理システム(10)及び方法は、外部デバッグツールをリアルタイムトレース機能を有するように許可することによってデバッグメッセージを生成する。データプロセッサ(20、22、24)は複数のデータ命令を実行し、情報記憶のためにメモリ(30)を使用する。デバッグ回路26はアドレス変換トレースメッセージを含むデバッグメッセージを生成する。仮想形態及び物理形態との間にアドレスを変換するようにアドレス変換を実行するために、メモリ管理ユニット(16)はアドレス変換論理(205)を有する。デバッグ回路(26)は、1つ以上のアドレス変換マッピングは変更される時に通信を受信するためにメモリ管理ユニット(16)に接続されるメッセージ生成回路(64)を含む。メッセージ生成回路(64)は、アドレスマッピングの変更を検出したことに応答してアドレス変換トレースメッセージを生成し、デバッグ回路(26)の外部にアドレス変換トレースメッセージを与える。  (もっと読む)

(もっと読む)

録画機器及びメモリチェック方法

【課題】これから使用されるメモリに対してのみ選択的にメモリチェックを行うことで、起動から使用開始までにかかる時間を短縮できるようにした録画機器を提供する。

【解決手段】録画再生機器10は、複数のメモリで構成される記録媒体14と、記録媒体14へのデータの記録を制御する記録媒体制御部13と、録画再生機器10に関する管理情報を記憶するシステム制御部15とを備える。記録媒体制御部13は、システム制御部15に記憶された管理情報に基づいて、記録媒体14を構成する複数のメモリの中から、使用が予定されるメモリを選択し、選択したメモリに対してのみメモリチェックを行う。例えば、記録媒体制御部13は、管理情報に基づいて、複数のメモリに対して未記録か否かを判定し、未記録と判定されたメモリを、前記使用が予定されるメモリとして選択する。

(もっと読む)

半導体記憶装置及びその自己テスト方法

【課題】テストコストの低減に対して有利な半導体記憶装置及びその自己テスト方法を提供する。

【解決手段】半導体記憶装置は、不揮発性メモリ11と前記不揮発性メモリの入出力データを格納するバッファ13とを備える主記憶部1と、揮発性メモリを備える前記主記憶部のバッファ部2と、データ入出力ピンを有する自己テストインターフェイス50と、前記主記憶部と前記バッファ部とを制御する制御部30とを具備し、前記制御部は、前記データ入出力ピンを介して自己テストインターフェイスから前記バッファへデータを格納し(S1)、前記バッファの格納データを、前記揮発性メモリへ書き込み(S2)、前記揮発性メモリから読み出したデータを前記バッファへ格納し(S4)、前記バッファの格納データを前記自己テストインターフェイスから読み出し、判定させる(S5)。

(もっと読む)

制御装置、制御システム及び制御方法

【課題】制御装置間で他の制御装置が実行するコンピュータプログラムを送受信して相互に役割を代替することが可能な構成とする場合に、制御装置が搭載される製品の検査のために記憶してあり、製品の完成後は不要となる検査用コンピュータプログラムが占める記憶領域を、製品完成後に有効に利用して、メモリを効率的に使用することができる制御装置、制御システム及び制御方法を提供する。

【解決手段】記憶部11bを備えるECUは、検査用プログラム15bを以後実行する可能性が無と判断した場合、記憶部11bにおける検査用プログラム15bが占める領域を上書可能領域に設定し、記憶部11aを備えるECUから送信される制御用プログラム13aを受信した場合、これを上書可能領域に記憶して実行することにより、同じ処理を異なるECUで実行可能な構成とする。

(もっと読む)

メモリ制御システム、メモリ制御方法、メモリ制御プログラム及び記録媒体

【課題】メモリ動作を決定する複数のパラメータを適切な値に調整する。

【解決手段】複数のパラメータが取り得る値の複数の組み合わせを管理するパラメータ管理部11aと、パラメータ管理部11aによって管理されている複数の組み合わせを複数のパラメータに順次設定するパラメータ設定部11dと、パラメータ設定部11dによって複数の組み合わせが複数のパラメータに順次設定される都度、メモリ2とメモリコントローラ12との間のメモリ動作の試験を行い、その試験の判定結果を蓄積するパラメータ試験部11bと、パラメータ試験部11bに蓄積された試験の判定結果に基づいて、複数の組み合わせの中の1組を決定するパラメータ決定部11cと、を備え、パラメータ設定部11dは、パラメータ決定部11cによって決定された複数の組み合わせの中の1組を複数のパラメータに設定する。

(もっと読む)

情報処理装置及びストレージシステム性能確認方法

【課題】ホストコンピュータがすべてのメディアに対して実効的なデータ記録スピード(処理速度)を確認し、ホストアプリケーションの実現可能な性能を判断できるようにする。

【解決手段】当該情報処理装置で動作させるアプリケーションで使用するシーケンスを生成し、前記シーケンスを前記情報処理装置とデータ通信可能に接続しているメディアへ送信する。そして、前記メディアによる前記シーケンスの実行時間の測定開始時及び測定終了時を受信して、前記シーケンスの実行時間を測定しスピード確認結果データを生成する。前記生成されたスピード確認結果データから、前記アプリケーションで実行可能な性能を判定する。

(もっと読む)

要求処理装置、要求処理システムおよびアクセス試験方法

【課題】他のシステム構成要素の組み付け状態に依存することなく、記憶装置に対するアクセス試験を簡易な構成で効率的に実行すること。

【解決手段】システムチップ3は、IOリクエスト処理部33内部のリクエスト応答処理部46が受信した応答を、シリアルインタフェース34で折り返してラッチ41に格納する。試験リクエスト処理部42は、ラッチ41に格納された応答を新たなリクエストに変換し、リクエスト保持部44に格納することで再使用する。

(もっと読む)

アドレスバスのテスト方法及びテスト装置

【課題】アドレスバスとデータバス夫々のバス幅の相対的な関係に依存せずにアドレスバスのテストをすること。

【解決手段】複数のメモリセルを有するメモリ装置20へ伝送される複数ビットのアドレスパタンの伝送路であるアドレスバス15aのテスト方法は、次のステップを含む。全ビットが第1論理値であるアドレスパタンにより特定されるメモリセルに対して第1論理値を書き込み、あるビットがその他の全てのビットとは異なり第2論理値である複数のアドレスパタン夫々により特定されるメモリセルに対して第1論理値を書き込み(S1)、第1のアドレスパタンにより特定されるメモリセルに対して第1論理値とは異なる値の第2論理値を書き込み(S5)、第2のアドレスパタンにより特定され、かつ第1論理値が読み出されるべきメモリセルからの第2論理値の読み出しに基づいてアドレスバスの不良を検出する(S4)。

(もっと読む)

アドレス線の試験方法及び試験装置

【課題】

試験時間の短縮化を図ったフラッシュメモリのアドレス線及び試験装置の試験方法及び試験装置を提供することを課題とする。

【解決手段】

全ての記憶を第1データ値にする第1工程と、特定のアドレス線を第1アドレス値に、その他のアドレス線を第2アドレス値に設定し、設定されたアドレスが示す記憶単位のうち特定の記憶を第2データ値とし、他の記憶は第1データ値とする書き込みを記憶単位に行う第2工程と、特定のアドレス線以外の他のアドレス線を第1アドレス値に設定し、特定の記憶と記憶単位上の位置が異なる記憶を第2データ値として、第2工程を行う第3工程と、第2工程と第3工程を繰り返し行った後に、全てのアドレス線を第2アドレス値に設定したアドレスが示す記憶単位を検査する第4工程とを有する。

(もっと読む)

RAM診断装置、そのプログラム

【課題】特にリアルタイム性が必要な処理がRAM診断処理によって妨害されないようにする。

【解決手段】RAM診断管理テーブル11には、RAM1内の各エリア毎に、そのエリアに格納するデータのデータ種別、ポインタ、診断トリガー、診断手法、診断間隔(診断周期)やタスクレベル等の各種属性情報等からなる管理情報が記憶される。特に、各データ種別毎に適切な診断手法が予め決定されて登録されている。割込関連データ処理部12等の各種機能部は、RAM診断管理テーブル11が示す内容に応じた診断処理を実行する。また、診断処理にはタスクレベルが割り当てられ、診断処理中であってもよりタスクレベルが高い処理が発生した場合には、割り込みを行わせる。

(もっと読む)

コンピュータ装置、プロセッサ診断方法、及びプロセッサ診断制御プログラム

【課題】プロセッサの不良機能を確実に特定して、各種の診断テストの正常な実行を担保すること。

【解決手段】第1のプロセッサと、第2のプロセッサと、メインメモリとを有するコンピュータ装置であって、第2のプロセッサによりメモリ診断プログラムを実行させることにより、メインメモリを診断し、メインメモリ内の不良領域を特定するメモリ診断手段と、メインメモリのうち、メモリ診断手段により特定された不良領域を除く領域に、第1のプロセッサの有する複数の機能を診断するためのプロセッサ診断プログラムを展開する診断プログラム展開手段と、展開されたプロセッサ診断プログラムを第2のプロセッサにより実行させることにより、第1のプロセッサの有する複数の機能のうち、実行不能な機能である不良機能を特定する不良機能特定手段と、を有する。

(もっと読む)

データ処理装置

【課題】出力端子やテストパターン数、テスト時間を増やさずに、エラーの発生を確実に通知することができるデータ処理装置を提供する。

【解決手段】データ処理装置は、メモリと、誤り検出回路と、タイミング調整回路と、端子とを具備する。誤り検出回路は、メモリの出力に基づいて誤りを検出して誤り検出信号を出力する。タイミング調整回路は、誤り検出信号に含まれるパルス信号のうちの所定の動作が開始された後の最初のパルス信号のパルス幅を誤り検出回路から出力されるパルス幅より長くする。端子は、メモリの試験時にタイミング調整回路の出力を外部に出力する。

(もっと読む)

コンピュータ装置、メモリ診断方法、及びメモリ診断制御プログラム

【課題】複雑なメモリ診断プログラムであってもOS起動前にこれを正常に実行することができること。

【解決手段】メインメモリを有するコンピュータ装置であって、第1のメモリ診断プログラムを実行することにより、メインメモリの不良領域の特定を行う第1のメモリ診断手段と、再配置可能な第2のメモリ診断プログラムが記憶された記憶手段と、メインメモリのうち、第1のメモリ診断手段により特定された不良領域を除く領域に、記憶手段に記憶されている第2のメモリ診断プログラムを展開し、実行する第2のメモリ診断手段と、を有する。

(もっと読む)

メモリモジュールのコントローラ及びメモリモジュールのコントローラの制御方法

【課題】受信したクロック信号及びストローブ信号のタイミングを判断して判断結果を出力する機能を有するメモリモジュールのコントローラにおいて、通常動作時と同様の構成でのループバックテストを可能とすること。

【解決手段】ライトデータ制御回路21、ストローブ制御回路11、リードデータ制御回路24、リードストローブ制御回路12、ライトデータ遅延回路22及び遅延制御部23を有し、ライトデータ遅延回路22及び遅延制御回路23は、リードストローブ制御回路12からリードデータ制御回路24に入力されるストローブ信号が、リードデータ制御回路がライトデータ制御回路21から入力されたデータ信号を保持するタイミングとなるように、信号のタイミングを遅延させる。

(もっと読む)

基準セルを使用する、メモリ・デバイスの軟データ生成の方法および装置

基準セルを使用する、メモリ・デバイスの軟データ生成の方法および装置を提供する。少なくとも1つの軟データ値が、1つまたは複数の基準セルに既知のデータを書き込むことと、基準セルのうちの1つまたは複数を読み取ることと、読み取られた1つまたは複数の基準セルに基づいて読取統計を入手することと、入手された読取統計に基づいて少なくとも1つの軟データ値を入手することとによって、メモリ・デバイス内で生成される。読取統計を、オプションで、メモリ・アレイの1つまたは複数の所望の位置について、あるいは1つまたは複数のアグレッサ・セル内の所与のパターンPATTについて、入手することができる。読取統計は、オプションで、複数の可能な値について入手された非対称統計を含むことができる。  (もっと読む)

(もっと読む)

メモリ検査回路

【課題】メモリへのライトアクセスとリードアクセスとが混在して実行された場合に生じる不具合を検出することができるメモリ検査回路を提供する。

【解決手段】書込アドレス用乱数発生回路21、書込データ用乱数発生回路22、書込制御部23、書込アドレス用乱数発生回路21と同じ読出アドレス用乱数発生回路31、書込データ用乱数発生回路22と同じ比較データ用乱数発生回路32、読出処理部33、判定部34、及びアクセス順序制御部5を備え、アクセス順序制御部5は、書込制御部23による書込処理を少なくとも1回実行させた後、書込制御部23による書込処理と読出処理部33による読出処理とをランダムな順序で実行させるようにした。

(もっと読む)

メモリ検査回路

【課題】アドレスとデータとの特定の組み合わせからなる特定のシーケンスが実行されたときにしか生じないようなメモリの故障モードを検出し、当該故障モードを生じさせるシーケンスを特定することが容易なメモリ検査回路を提供する。

【解決手段】書込アドレス用乱数発生回路21、書込データ用乱数発生回路22、書込制御部23、書込アドレス用乱数発生回路21と同じ読出アドレス用乱数発生回路、書込データ用乱数発生回路22と同じ比較データ用乱数発生回路、読出処理部、判定部、及び乱数生成制御部を備え、乱数生成制御部は、RAMへのアクセスを再現するときは、書込アドレス用乱数発生回路21、書込データ用乱数発生回路22、読出アドレス用乱数発生回路、及び比較データ用乱数発生回路を構成する乱数発生回路のLFSRを、それぞれ順方向とは逆の逆方向にシフトさせるようにした。

(もっと読む)

メモリアドレス検証方法

【課題】 半導体メモリの試験パターンに含まれるアドレスの規則性の乱れを検出する。

【解決手段】 メモリアクセス試験のために生成されたアドレスADがメモリ試験装置TST、WSに入力される。メモリ試験装置TST、WSは、異なるアドレスADの間の変化を検出する。メモリ試験装置TST、WSは、これら変化が異なるときに、異なることを示す情報を出力する。これにより、アドレスADの規則性の乱れを検出でき、メモリアクセス試験に使用されるアドレスADに誤りの可能性があることを検証できる。この結果、メモリアクセス試験を実行するためのプログラムTPRGのデバッグ効率を向上できる。

(もっと読む)

81 - 100 / 262

[ Back to top ]