Fターム[5B018MA24]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | ICカード、メモリカード (351)

Fターム[5B018MA24]に分類される特許

101 - 120 / 351

記憶媒体

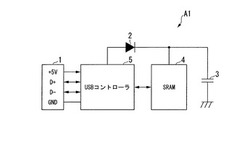

【課題】データの漏えいを防止できる安価な記憶媒体を提供する。

【解決手段】記憶媒体が、コンデンサと、コンデンサに蓄えられた電力を基にデータを記憶する揮発性メモリとを具備する。コンピュータのUSBポートにUSBメモリが装着されると、USBコントローラ5は、USBコネクタ1を介してコンピュータから電力を受け取り、当該電力をコンデンサ3及びSRAM4に供給する。そして、コンピュータのUSBポートからUSBメモリが取り外されると、コンデンサ3は、SRAM4への電力の供給を開始する。SRAM4は、コンデンサ3から電力が供給されている間データを継続して記憶するが、コンデンサ3の電力がなくなると電力の供給が停止するので、記憶しているデータが消える。

(もっと読む)

インサイチュでのメモリのアニール

メモリデバイスを有するシステムにおいて、あるイベントがシステム操作中に検出される。メモリデバイスは、そのイベントの検出に応じて、メモリデバイスの使用に起因する劣化を反転させるために加熱される。別のシステムにおいて、メモリデバイスは、そのシステムの別のメモリデバイス内でのデータアクセス操作と同時に使用に起因する劣化を回復させるために加熱される。第1および第2のメモリデバイスと連結されたメモリコントローラを有する別のシステムにおいては、データは、メンテナンス操作が第1のメモリデバイス内において必要であると決定することに応じて、第1のメモリデバイスから第2のメモリデバイスに退避される。 (もっと読む)

電子機器及びプログラム

【課題】落下や水没等の様な特殊な状態になったことを検出して内部のデータをバックアップする機能を備えているとともに、バックアップされたデータが漏洩されることを防止し得るようにする。

【解決手段】特殊状態検出部13は、携帯電話装置1の落下や水没等の特殊状態を検出して検出信号を中央制御部2に送出する。中央制御部2は検出信号を受けてアプリ情報記憶部11に記憶されている情報をバックアップメモリ12にバックアップさせたり、無線通信部4を介してネットワーク上のサーバなどにバックアップさせたりする。その後、携帯電話装置1に異常があるかを判断し、異常が無い場合にはバックアップメモリ12やサーバなどにバックアップされたバックアップデータを削除して、バックアップデータが漏洩するのを防止する。

(もっと読む)

情報処理方法、情報処理装置、およびプログラム

【課題】メモリコラプションに対処しつつ、データの書込み処理に要する時間を短縮する。

【解決手段】ステップS34では、データ領域の全ての更新ブロックの物理ブロック番号が参照されてデータ領域の更新ブロックとして認識される。そして、ステップS35で、データ領域の更新ブロックとして認識された全ての物理ブロックが一括して消去される。これにより、物理ブロックにデータを書込み毎に消去する場合に比較して、処理時間を短縮することができる。本発明は、EEPROMのように、データを書き込む場合、記録領域に既に記録されているデータに上書きすることができず、既に記録されているデータを消去してから新たなデータを記録しなければならない記録媒体に対して、データを書き込む場合に適用することができる。

(もっと読む)

記憶装置およびメモリコントローラ

【課題】フラッシュメモリのページ間のコピーに制限を生じさせることなく、データに対するスクランブルを実行可能なメモリコントローラを提供する。

【解決手段】メモリコントローラは、スクランブルパターン生成部と、スクランブル処理部と、論理物理アドレス変換テーブルと、メモリインターフェースと、制御回路とを備え、物理ページをセクターデータ部と管理部に分けて管理する。制御回路は、データ部に対しては、データ部に固有の論理アドレスに関連する情報を基にしてスクランブルパターン生成部でスクランブルパターンを生成し、スクランブル処理部でこの論理アドレスに対応するデータ部のデータをスクランブルし、管理部に対しては、物理アドレスに関連する情報を基にしてスクランブルパターン生成部でスクランブルパターンを生成し、スクランブル処理部で管理データをスクランブルし、半導体メモリに対して書き込み読み出しを行う。

(もっと読む)

メモリ記憶装置

【課題】ホスト装置が不揮発性メモリから記憶情報を読出さずに不揮発性メモリのデータ保持に対する信頼性を向上させる。

【解決手段】本発明に係るメモリ記憶装置は不揮発性メモリ(2)とメモリコントローラを有する。メモリコントローラは、ホストインタフェース回路(10)、メモリインタフェース回路(12)及び制御回路(11,13,14)を有する。制御回路は第1〜3処理を制御可能である。第1処理は書込みデータにエラー訂正コードを付加したデータをメモリインタフェース回路から書込み制御情報と共に出力する。第2処理は読出し制御情報に従いエラー検出・訂正したデータをホストインタフェース回路から出力する。第3処理は読出し制御情報に従いエラー検出・訂正したデータを書込み制御情報と共に出力する。メモリコントローラは、第3処理において、エラー発生回数が所定回数を超えたときエラー訂正された読出しデータの記憶領域を変更する。

(もっと読む)

メモリ・デバイス上の故障注入による攻撃を検知する方法、及び対応するメモリ・デバイス

【課題】メモリ・デバイス上の故障注入による攻撃を検知する。

【解決手段】メモリ・デバイスがデータ・ビット及びmパリティ・ビットを備えたブロック(BL)を貯蔵するメモリ・プレーン(PM)のグループ、及び、ブロックの各ビットを読出す手段(ML)及びブロックの読出時に各データ・ビットの読出値及び各パリティ・ビットの読出値に基づきパリティ・チェックをする検証手段を備えた故障注入攻撃検知手段を備え、メモリ・プレーン(PM)はmメモリ・セルの別々のパケット(PQ)を形成するよう前記グループのメモリ・セル間に配置された参照メモリ・セルを備え、各参照メモリ・セルは故障注入攻撃の間に参照値で変更される参照ビットを貯蔵し、mメモリ・セルの各パケットは、異なるパリティに関連するブロックのmビットを貯蔵する。

(もっと読む)

不揮発性記憶装置、アクセス装置、及び不揮発性記憶システム

【課題】アクセス装置から高温になった不揮発性記憶装置を取り出したときの支障を回避することと、不揮発性記憶装置への高速なデータの転送とを両立する。

【解決手段】不揮発性記憶装置100Aは、データを記憶する不揮発性メモリ120と、不揮発性メモリ120にデータを読み書きするメモリコントローラ110Aとを備える。メモリコントローラ110Aは、アクセス装置200A又は200Bが不揮発性記憶装置100Aの排出を抑制する排出制御機構203を有するかどうかの情報である排出制御情報を取得する情報取得部101と、排出制御情報に応じて、データの読み出し又は書き込みのアクセスレートを制御するアクセスレート制御部106Aと、を有する。

(もっと読む)

表示装置、データ変換方法およびデータ変換プログラム

【課題】内部電池の電力残量に応じて、電子ファイルを適切に特定のデータ形式に変換することができる表示装置、データ変換方法およびデータ変換プログラムを提供する。

【解決手段】携帯端末では、メモリカードに記憶されている他のデータ形式の電子ファイルが取得されると、バッテリにデータ変換に必要な電力残量があるか否かが判断される(S11)。バッテリにデータ変換に必要な電力残量がある場合(S11:YES)、電子ファイルが特定のデータ形式に変換されて、その変換済ファイルがメモリカードに記憶される(S15)。一方、バッテリにデータ変換に必要な電力残量がない場合は(S11:NO)、電子ファイルは特定のデータ形式に変換されない。

(もっと読む)

管理型不揮発性メモリのための低レイテンシ読み取り動作

メモリシステムにおいて、ホストコントローラは、不揮発性メモリ(NVM)パッケージ(例えば、NAND装置)に結合される。ホストコントローラは、低レイテンシの読み取り動作を要求する読み取りコマンドをNVMパッケージへ送信する。読み取りコマンドに応答して、NVMパッケージのコントローラは、データを検索し、そしてデータを修正のためにECCエンジンへ送信する。読み取りコマンドに続いて、ホストコントローラは、読み取り状態要求コマンドをNVMパッケージのコントローラへ送信する。その読み取り状態要求に応答して、コントローラは、幾つかの又は全てのデータをホストコントローラへの転送に利用できることを指示する状態レポートをホストコントローラへ送信する。このレポートに応答して、ホストコントローラは、データを転送する。未修正のデータがホストコントローラへ転送されたことを指示するためにアンダーラン状態を決定することができる。 (もっと読む)

記憶装置、基板、液体容器、データ記憶部に書き込むべきデータをホスト回路から受け付ける方法、ホスト回路に対し電気的に接続可能な記憶装置を含むシステム

【課題】記憶装置において、ホスト回路との通信の信頼性を向上する。

【解決手段】ホスト回路と電気的に接続される記憶装置は、不揮発性のデータ記憶部と、データ受信部と、判定部と、データ送信部とを備える。データ受信部は、ホスト回路からメモリアレイに書き込むべき第1のデータと、第1のデータに基づいて生成された第2のデータを受信する。判定部は、第1のデータと第2のデータとの整合性を判定する。データ送信部は、判定の結果をホスト回路に送信する。

(もっと読む)

メモリコントローラおよび半導体記憶装置

【課題】それぞれが、いずれかのブロック33に分類可能な複数のメモリセル31から構成されたメモリ部30に記憶するデータの誤り訂正処理の効率が良いメモリコントローラ10および半導体記憶装置2を提供する。

【解決手段】誤り訂正数と対応した誤り訂正レベルを記憶する誤り訂正数対応テーブル25と、各ブロック単位の誤り訂正レベルを記憶する誤り訂正レベル記憶部23と、各ブロック単位ごとの誤り訂正不能回数を計測する訂正不能回数計測部26と、誤り訂正不能回数が所定の回数を超えるごとに、各ブロックの誤り訂正レベルを変更する誤り訂正レベル変更部24と、誤り訂正レベルおよび誤り訂正数対応テーブル25にもとづいた誤り訂正数で符号化処理を行う符号化器21と、復号器22と、を有する。

(もっと読む)

データ生存性を得るためのシステムおよび方法

データを記憶するためのシステムおよび方法を提供する。この保護メモリシステムは、それぞれが互いに対して離れて位置する複数のメモリモジュールを含むメモリアレイと、記憶すべきデータをデータ取得ユニットから受け取り、その受け取ったデータを、複数のメモリモジュールのそれぞれの中の対応する記憶場所に記憶し、記憶されるデータには誤り検査情報が含まれ、第1の記憶場所においてデータ誤りが検出されるまで複数のメモリモジュールのうちの第1のメモリモジュールからデータを読み取り、複数のメモリモジュールのうちの第2のメモリモジュールの第2の記憶場所から、第1の記憶場所から読み取られるデータに対応するデータを読み取り、第1の記憶場所から読み取ったデータを、第2の記憶場所から読み取ったデータで置換するように構成されるメモリコントローラとを含む。 (もっと読む)

ストレージ装置およびそのデータ制御方法

【課題】 新規に追加交換されるFMPK130を含む複数のFMPK130の間で効率的な平準化を行うこと。

【解決手段】

ストレージコントローラ110は、実FMPK130内に空きブロックが不足した場合、実FMPK130の中のいずれかのFMPK130および追加された代替用FMPK130を平準化対象のデバイスとするときに、平準化対象のデバイスに属する実FMPK130のブロックの属性が、Hotであるときには、当該ブロックに属するデータのうち閾値より大きいデータを代替用FMPK130のブロックに移動させ、平準化対象のデバイスに属する実FMPK130のブロックの属性が、Coldであるときには、当該ブロックに属するデータのうち閾値より小さいデータを代替用FMPK130のブロックに移動させる。

(もっと読む)

半導体装置ソケット

【課題】 半導体モジュールの不具合によるシステム不起動が生じた場合でも、不具合の原因を検出できるようにする。

【解決手段】 半導体装置ソケットは、半導体記憶装置を備えた半導体モジュールの挿入部を受けるソケット部と、システムへの挿入部と、半導体記憶装置の代わりに使用可能な代替半導体記憶装置と、半導体モジュールの半導体記憶装置と代替半導体装置との間でシステムとの接続を切り替える切替スイッチと、を備える。

(もっと読む)

非接触型携帯可能電子装置および非接触型ICカード

【課題】メモリへのデータ書込みの途中にエラーが発生しても、データ書込みを最初からやり直す必要がなく、書込みデータ長によっては大幅な処理時間の短縮効果が期待できる非接触型携帯可能電子装置および非接触型ICカードを提供する。

【解決手段】非接触型カードリーダ・ライタから送信される電磁波を受信し、この受信した電磁波により動作電圧を生成して動作するもので、非接触型カードリーダ・ライタから送信される書込みコマンドに基づき不揮発性メモリにデータを書込む処理を行ない、その処理結果を非接触型カードリーダ・ライタへ送信する非接触型ICカードにおいて、不揮発性メモリに対するデータの書込み途中にエラーが発生し、書込みが途中まで正常に終了していた場合、その旨のレスポンスに、正常に書込みが終了したデータの長さ、書込みが終了していないデータの長さ、メモリの書込みに失敗したアドレスのうち少なくともいずれか1つを示すデータを付加して非接触型カードリーダ・ライタへ送信する。

(もっと読む)

メモリ装置

【課題】数十年以上の単位で記録データを長期的に安定に保存でき、しかも保存データを確実に読み出し可能なメモリ装置を提供する。

【解決手段】第1回路200は、データ記録回路210と、第2回路300からの読み出しまたは書き込み指示を受けて、アドレス信号に応じてデータ記録回路に対するデータの書き込みおよび読み出し制御を行う書き込み読み出し制御回路230と、を含み、第2回路300は、第1回路とのデータ転送制御を行うデータ転送制御回路310と、データ転送制御回路の作業用メモリ320と、を含み、データ転送制御回路310は、第1回路200のデータ記録回路210への書き込みデータを、いったん作業用メモリ320に蓄積し、蓄積したデータを順次に第1回路側の書き込み読み出し制御回路230に転送する。

(もっと読む)

メモリコントローラおよび半導体記憶装置

【課題】読み出すデータの信頼性の高いメモリコントローラ10および半導体記憶装置2を提供する。

【解決手段】論理アドレス/物理アドレス変換テーブル16と、各メモリセル31からデータを読み出すアクセス回数を論理アドレスと対応して記憶するアクセス回数記憶部15と、所定のアクセス回数ごとに各メモリセル31に記憶されているデータの記憶状態を確認する記憶状態確認部13と、データの記憶状態が所定の劣化状態の場合に各メモリセル31に記憶されたデータを記憶しなおすリフレッシュ処理を行うリフレッシュ処理部12と、を有する。

(もっと読む)

メモリ装置

【課題】数十年以上の単位で記録データを長期的に安定に保存でき、しかも保存データを確実に読み出し可能なメモリ装置を提供する。

【解決手段】第1回路200は、データ記録回路210に対するデータの書き込みおよび読み出し制御を行い、所定のイベントの発生によりデータ記録回路への読み出し・書き込み信号を第1レベルに設定してデータの書き込み禁止となるように制御する書き込み読み出し制御回路230と、書き込みが禁止されたデータ記録回路からの読み出しデータを第2回路に転送する長期信頼性読み出し制御回路240と、非書き込み禁止時には書き込み読み出し制御回路を通してデータ記録回路に対するデータの書き込みおよび読み出しを行う第1経路を選択し、書き込み禁止時には、長期信頼性読み出し制御回路を通してデータ記録回路からのデータの読み出しを行う第2経路を選択するセレクタ250と、を含む。

(もっと読む)

携帯可能電子装置および携帯可能電子装置におけるデータ管理方法

【課題】データメモリの記憶領域を効率的に使用しつつ、最新のレコードデータと更新前の複数世代のレコードデータとを容易に保存したり、簡単な手順で読み出したりすることができるICカードを提供する。

【解決手段】ICカード1は、複数のレコードデータを格納するレコードファイルを記憶するデータメモリ14を有し、外部装置2からレコードファイルにおける特定のレコードデータの書換えを要求するコマンドが与えられた場合、書換えが要求されたレコードデータの書換え前のレコードデータを当該レコードファイル内にバックアップデータとして保存し、書換え前のレコードデータをバックアップデータとして保存した場合、前記コマンドに従って当該レコードデータを書き換える。

(もっと読む)

101 - 120 / 351

[ Back to top ]