Fターム[5C006BC06]の内容

液晶表示装置の制御 (150,375) | 表示器駆動回路 (12,655) | アクティブにおける画素単位回路 (2,022) | 3端子型(TFT、FET) (1,869)

Fターム[5C006BC06]に分類される特許

201 - 220 / 1,869

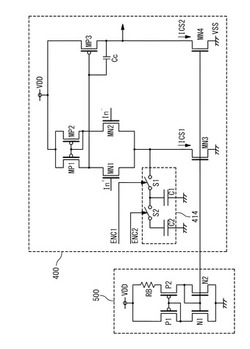

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

電気光学装置および電子機器

【課題】表示領域aとダミー表示領域bとの差を、より小さくする。

【解決手段】表示領域aにおいて画素電極118は、所定のピッチでマトリクス状に配列する。表示領域aを囲むダミー表示領域bにおいて設けられるダミー画素電極131は、画素電極118と同一層からなり、かつ画素電極118に等しいサイズおよびピッチで島状に配列する。ダミー画素電極131は、画素電極118よりも下層の配線を介して互いに相互接続されている。

(もっと読む)

映像表示方法およびそれを用いた液晶表示装置

【課題】2種類の映像を交互に表示する際、各映像への黒挿入による残像の発生を均一化する。

【解決手段】

2種類の映像フレームを交互に出力する左右映像交互出力部15と、液晶パネルの画素領域に対応して4以上の偶数個であるm個の画素をマトリックス状に配列した画素領域である基本領域内に、mより小さい2以上の偶数個のマスク画素が異なる配列で配置されるm通りのマスクパターンを有するマスクパターン記憶部18と、マスクパターンを順次選択するマスクパターン選択カウンタ17と、選択されたマスクパターンを交互出力部から出力される映像フレームに合成するマスク合成部16とを備え、マスクパターンはm通りのマスクパターンを通じて前記基本領域内における画素単位でのマスク画素の配置される回数が等しい。

(もっと読む)

表示装置及び表示装置の駆動方法

【課題】表示画像の画質の低下を抑制する。

【解決手段】M行(Mは2以上の自然数)N列(Nは自然数)に配列された複数の表示回路と、ライトユニットと、を具備し、ライトユニットは、X行(Xは2以上の自然数)に配列され、行毎に少なくとも異なる1行以上の表示回路に重畳し、赤色に呈する発光ダイオード、緑色に呈する発光ダイオード、及び青色に呈する発光ダイオードを含む複数の発光ダイオード群と、複数の表示回路及び複数の発光ダイオード群の間に設けられた導光板と、を有し、導光板は、複数の発光ダイオード群のうち、互いに異なる行の発光ダイオード群の光を透過するX個の導光部材を含む。

(もっと読む)

液晶表示パネル、液晶駆動装置、液晶表示装置

【課題】ドット反転駆動時の電力ロスを低減することが可能な液晶表示装置を提供する。

【解決手段】液晶表示パネル30は、複数行のゲート線Gと、複数列のソース線Sと、複数個の液晶画素と、を有しており、液晶表示パネル30全体として前記複数個の液晶画素に各々印加される電圧の極性がドット毎に反転されるように、かつ、前記複数列のソース線Sに各々印加される電圧の極性が少なくとも行走査期間にわたって反転されないように、前記複数列のソース線S及び前記複数個の液晶画素がレイアウトされている。

(もっと読む)

液晶表示装置、および液晶表示装置の駆動方法

【課題】ヒステリシス特性を有する液晶層を含む液晶表示装置において、前階調の影響を受けずに同一電圧の印加時に一定の輝度で表現ことが可能な、液晶表示装置および液晶表示装置の駆動方法を提供する。

【解決手段】複数の液晶印加電圧に対する透過率特性曲線がヒステリシス特性を有する液晶層を含む液晶表示装置の駆動方法であって、一フレームの階調データに対応する複数の階調電圧を印加する前に液晶層にリセット電圧を印加するステップと、ヒステリシス特性による複数の電圧曲線のうち、印加されたリセット電圧によって選択された1つの電圧曲線に対応する複数の階調電圧を生成するステップと、複数の階調電圧を液晶層のうち対応する領域に印加するステップとを有する、液晶表示装置の駆動方法が提供される。

(もっと読む)

電気光学装置および電子機器

【課題】多画面表示装置または立体画像表示装置において、フリッカー、横スジ(または

斜めスジ)、縦クロストーク、または横クロストークの発生を抑制する。

【解決手段】TFT(Thin Film Transistor)116と画素電極118との組が、m×n

個設けられている。画素電極118は、矩形形状を有し、透明性を有する材料で形成され

ている。TFT116のゲート電極は走査線112に接続され、ソース電極はデータ線1

14に接続され、ドレイン電極は画素電極118に接続されている。画素電極118は、

m行n列のマトリックス状に配置されている。一の列において、画素電極118は、隣り

合う2つのデータ線114に交互に(TFT116を介して)接続されている。

(もっと読む)

飽和電圧と閾値電圧間の変調を達成するための多重ピクセルを備えたディスプレイ

【課題】ピクセルに記憶されたデータを迅速に反転可能なマルチビットデータワードを表示する液晶ディスプレイを提供する。

【解決手段】ピクセル電極612、記憶素子702、第1の電圧供給端子622、第2の電圧供給端子624、共通電極、およびマルチプレクサ704を含み、マルチプレクサが、記憶素子702のうちの関連付けられた1つに記憶されたデータビットの値に応答して、ピクセル電極612のうちの関連付けられた1つを第1の電圧供給端子622および第2の電圧供給端子624のうちの1方と選択的に接続し、記憶されるビットの重要性に依存する時間の間、マルチビットデータワードの各ビットを記憶素子702に連続的に書き込み、ならびに各ビットを記憶素子702に記憶しつつ、第1の所定の電圧を第1の電圧供給端子622に、第2の所定の電圧を第2の電圧供給端子624に、そして第3の所定の電圧を共通電極にアサートする。

(もっと読む)

画素回路、電気光学装置及び電子機器

【課題】出力回路のトランジスターの劣化等を抑制しながら画素を駆動できる画素回路等の提供。

【解決手段】画素回路はデータ信号をラッチするラッチ部と、バッファー回路を有し、ラッチ部からのラッチデータ信号に基づく駆動データ信号をバッファリングして画素に出力する出力回路30を含む。出力回路30は、バッファー回路の出力ノードNCQと画素回路出力ノードNQとの間に設けられる抵抗RPと、高電位側電源VDDのノードと画素回路出力ノードNQとの間に設けられ、画素回路出力ノードNCQから高電位側電源VDDのノードに向かう方向を順方向とする第1のダイオードDI1と、画素回路出力ノードNQと低電位側電源VSSのノードとの間に設けられ、低電位側電源VSSのノードから画素回路出力ノードNQに向かう方向を順方向とする第2のダイオードDI2を含む。

(もっと読む)

表示装置

【課題】順方向走査駆動する場合と、逆方向走査駆動をする場合とに生じる、画素回路の保持電圧の差異の影響を抑制し、表示品質が向上される表示装置の提供。

【解決手段】データ信号線と、複数の画素回路と、複数のゲート信号線と、順方向又は逆方向走査駆動のいずれかを駆動するとともにゲートオーバーラップ駆動をする、ゲート信号線駆動回路と、画素回路の表示データに応じた表示制御電圧をデータ信号線に供給する、データ信号線駆動回路と、各画素回路に応じる基準電圧を該画素回路それぞれに供給する、基準電圧線駆動回路と、を備える表示装置であって、前記各画素回路は、画素電極と、基準電極と、スイッチング素子と、を備え、前記基準電圧線駆動回路は、順方向又は逆方向走査駆動の際、各画素回路の前記基準電極に、それぞれ、順方向基準電圧又は逆方向基準電圧を選択して、供給する、ことを特徴とする。

(もっと読む)

画素回路、電気光学装置及び電子機器

【課題】ラッチ回路の誤動作発生等を抑止しながら画素を駆動できる画素回路等の提供。

【解決手段】画素回路は第1、第2のラッチ回路11、12を含む。第1のラッチ回路11は、並列接続されたP型トランジスターTP1及びN型トランジスターTN1により構成される第1のトランスファーゲートTG1と、直列接続されたP型トランジスターTP2、TP3、N型トランジスターTN3、TN2により構成される帰還用第1のクロックドインバーター回路CIV1と、第1のインバーター回路IV1を含む。第2のラッチ回路12は、並列接続されたP型トランジスターTP5及びN型トランジスターTN5により構成される第2のトランスファーゲートTG2と、直列接続されたP型トランジスターTP6、TP7、N型トランジスターTN7、TN6により構成される帰還用第2のクロックドインバーター回路CIV2と、第2のインバーター回路IV2を含む。

(もっと読む)

液晶表示装置及びその駆動方法

【課題】ブラック階調の映像データの残像問題を改善する液晶表示装置及びその駆動方法を具現すること。

【解決手段】液晶パネルと;T−Vカーブの特性によって各階調に対応するガンマ電圧が設定されたガンマ電圧供給部と;前記ガンマ電圧を用いて、入力されたデジタル映像データをアナログ映像データに変換し、前記液晶パネルに出力するデータ駆動部を備え、前記各階調のうち、ブラック階調に対応する前記ガンマ電圧値が0V〜0.005Vになるように設定された液晶表示装置及びその駆動方法を提供する。

(もっと読む)

画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置

【課題】超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な画素回路を提供する。

【解決手段】電気光学素子と、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、第2スイッチ素子の制御端子に一方の電極端子が接続され、第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、を備え、電気光学素子に保持された画像データに対応する電圧レベルが、第1スイッチ素子を介して第1容量素子にサンプリングされ、第2スイッチ素子を介して第2容量素子にサンプリングされることを特徴とする、画素回路が提供される。

(もっと読む)

液晶ディスプレイ装置及びこれを有する電子機器

【課題】高い透過率及び/又は反射率を確保しながら安定に多色表示可能な液晶ディスプレイ装置等を提供する。

【解決手段】液晶ディスプレイ装置は、マトリクス状に配置された複数の画素を有する。夫々の画素は、その画素による表示色を示すデジタル値を記憶するメモリ回路(24)と、メモリ回路(24)に記憶されているデジタル値を表示色に対応する電圧に変換するデジタル−アナログ変換回路(25)と、電圧に応じて異なる波長の光を透過又は反射する液晶セル(22)とを有する。

(もっと読む)

ディスプレイ装置及びこれを有する電子機器

【課題】回路構成及び制御を複雑化することなく光リーク電流を抑制することができるディスプレイ装置等を提供する。

【解決手段】ディスプレイ装置は、行及び列のマトリクス状に配置される複数の画素と、画素の行又は列ごとに設けられる複数の信号線とを有する。夫々の画素Pjiは、画素電極20と、画素Pjiが属する画素の行又は列に対して設けられている信号線15−iと画素電極20との間に直列に配置され、同時にオン及びオフする2つのスイッチング素子21、22と、2つのスイッチング素子21、22の間に所定の一定電圧を接続する抵抗素子30とを有する。抵抗素子30は、2つのスイッチング素子21、22のオン抵抗よりも大きく、2つのスイッチング素子21、22のオフ抵抗よりも小さい抵抗を有する。所定の一定電圧は、信号線15−iに印加される信号電圧のセンター電圧に等しい。

(もっと読む)

半導体装置及びその駆動方法

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

液晶表示パネル、液晶表示装置、及び液晶表示装置の駆動方法

【課題】液晶表示パネル、液晶表示装置、及び液晶表示装置の駆動方法を提供すること。

【解決手段】マトリックス形態で配列される複数のピクセルと、ピクセルのうち第1行−ピクセルと接続される第1サブゲートラインと、ピクセルのうち第2行−ピクセルと接続される第2サブゲートラインと、第1サブゲートラインと第2サブゲートラインとの間に位置し、各々上側に隣接する第2行−ピクセルと下側に隣接する第1行−ピクセルと接続する複数のゲートラインと、ピクセルのうち隣接する第1列−ピクセルと接続される複数の偶数データラインと、ピクセルのうち隣接する第2列−ピクセルと接続される複数の奇数データラインと、を含むことを特徴とする、液晶表示パネルが提供される。液晶表示パネルは、水平クロストーク及び垂直クロストークを防止しながらも消費電力を効率的に減少させることができる。

(もっと読む)

画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置

【課題】超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な画素回路を提供する。

【解決手段】電気光学素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、第2スイッチ素子の制御端子に一方の電極端子が接続され、第2スイッチ素子の他方の電極端子に他方の電極端子が接続され、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する容量素子と、を備え、電気光学素子に保持された画像データに対応する電圧レベルが、第1スイッチ素子をオンすることにより、第2スイッチ素子を介して容量素子にサンプリングされることを特徴とする、画素回路が提供される。

(もっと読む)

ディスプレイ装置及びこれを備える電子機器

【課題】フリッカを発生させることなくメモリ回路を各画素に組み込むディスプレイ装置等を提供する。

【解決手段】ディスプレイ装置は、マトリクス状に配置された複数の画素を有する。各画素Pjiは、第1の電極20と第2の電極24との間の電位差に応じて透過可能な光量が変化する光透過素子22と、第1の電極20にある電位を記憶しておくメモリ回路25とを有する。ディスプレイ装置は、更に、周期的にメモリ回路25をリフレッシュするコントローラを有する。コントローラは、リフレッシュタイミングで第1の電極20が第2の電極24に対して正の電位を有する場合に、メモリ回路25に第1の電極20での電位を記憶させ、第2の電極24に第1の所定電圧を印加して第1の電極20での電位を第1の所定電圧の分だけ増大させ、第1の電極20にある電荷を放電させて第1の電極20が第2の電極24に対して負の電位を有するようにする。

(もっと読む)

表示装置

【課題】 表示パネルの外部回路の構成をシンプル化すると共に、低消費電力化を図る。

【解決手段】 ゲート信号線51から入力される信号に応じてドレイン信号線61からのデジタル映像信号を保持する保持回路110を設ける。保持回路110からの信号に応じて2つの信号(信号Aと信号B)のいずれかを選択して画素電極80に供給する信号選択回路120を設ける。そして、信号A、信号Bを作成する基準電圧発生回路500を表示パネル100内に設ける。デジタル表示モード時には、基準電圧発生回路500により、表示画素80に印加する信号を作成しているので、これらの信号A及び信号Bを外部から供給する必要がない。

(もっと読む)

201 - 220 / 1,869

[ Back to top ]