Fターム[5C006BC06]の内容

液晶表示装置の制御 (150,375) | 表示器駆動回路 (12,655) | アクティブにおける画素単位回路 (2,022) | 3端子型(TFT、FET) (1,869)

Fターム[5C006BC06]に分類される特許

141 - 160 / 1,869

表示装置

【課題】画素回路に含まれるトランジスタに生じるゲート・ソース間の寄生容量が異なる。

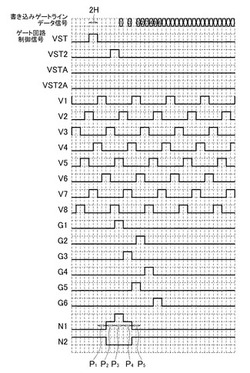

【解決手段】表示装置であって、それぞれ、トランジスタと、前記トランジスタに接続された画素電極と、該画素電極に対向して配置された基準電極と、を含み、マトリクス状に配置された複数の画素回路と、対応する前記複数の画素回路にそれぞれ接続される複数のデータ線と、対応する前記複数の画素回路にそれぞれ接続される複数のゲート線と、それぞれ、第1の順序または第2の順序で、順に2水平期間以上の水平期間にハイ電圧となるゲート信号を出力する、該ゲート信号が出力される水平期間に応じた数の複数のゲート回路と、前記各ゲート回路を制御し、前記複数のゲート線を走査するゲート信号制御回路と、を含み、前記ゲート信号制御回路は、隣接するゲート線においてゲート信号が出力される期間が重複しないように、前記各ゲート回路にゲート信号の出力を開始させる。

(もっと読む)

液晶表示装置

【課題】複数種類の映像信号を画素内に保持できるようにすることで、面順次動作を可能とする。

【解決手段】画素106は、奇数フィールド表示期間では、保持容量Cs1に保持されている奇数フィールドの映像信号のサンプリング電圧を正転・反転アンプ120により正転増幅した信号と反転増幅した信号とを垂直走査周期よりも短い所定の周期でトランジスタTr3、Tr6により交互に切り替えて画素電極PEに印加することで奇数フィールドの映像表示を行う。これと並行してデータ線Diを介して供給される偶数フィールドの映像信号をトランジスタTr4によりサンプリングして保持容量Cs2へ書き込む。偶数フィールド表示期間では奇数フィールド表示期間と逆に保持容量Cs2の読み出しと保持容量Cs1への書き込みとが同時に行われる。

(もっと読む)

表示装置

【課題】映像線駆動回路内に表示制御回路を内蔵することにより、部品点数を削減した表示装置を提供する。

【解決手段】各映像線駆動回路はバス接続され、前記複数の映像線駆動回路の中の1つの映像線駆動回路は、マスタの映像線駆動回路として動作し、前記複数の映像線駆動回路の中の前記マスタの映像線駆動回路以外の映像線駆動回路はスレーブの映像線駆動回路として動作し、前記各映像線駆動回路の前記表示制御回路は、前記表示制御回路の設定値を保持するレジスタを有し、前記表示装置の起動時に、前記レジスタに対して、外部メモリから前記表示制御回路の設定値を書き込むことが可能であり、前記表示装置の起動時に、前記レジスタに対して、前記外部メモリから前記表示制御回路の設定値を書き込む際に、前記マスタの映像線駆動回路から最終の前記スレーブの映像線駆動回路まで順番に前記外部メモリにアクセスし、前記レジスタに前記設定値を書き込む。

(もっと読む)

液晶表示素子

【課題】絵柄によって動作中の配線容量が変化することに起因する疑似信号の発生を抑圧し、表示品質を向上させる。

【解決手段】液晶表示素子10は、バッファアンプ11が制御信号用配線S+とスイッチングトランジスタTr5のゲートとの間に接続され、バッファアンプ12が制御信号用配線S-とスイッチングトランジスタTr6のゲートとの間に接続されている。このため、画面全体で一様な中間階調(グレー)の画像を表示する場合と、中間階調の画面内に四角の白いボックスで表示される画像を表示する場合とで、トランジスタTr5、Tr6のドレインに印加される保持容量Cs1、Cs2の保持電圧が異なったとしても、それが配線S+、S-に反映されることがない。

(もっと読む)

半導体装置及び表示装置

【課題】 一導電型のTFTによって構成され、かつ出力信号の振幅を正常に得られる表示装置の駆動回路を提供する。

【解決手段】 TFT101、104にパルスが入力されてONし、ノードαの電位が上昇した後、VDD−VthNとなったところで浮遊状態となる。よってTFT105がONし、クロック信号がHiとなるのに伴って出力ノードの電位が上昇する。一方、TFT105のゲート電極の電位は、出力ノードの電位上昇に伴い、容量107の働きによってさらに上昇し、VDD+VthNより高くなる。よって出力ノードの電位は、TFT105のしきい値によって電圧降下することなくVDDまで上昇する。その後、次段出力がTFT102、103に入力されてONし、ノードαの電位は下降してTFT105がOFFする。同時にTFT106がONし、出力ノードの電位はLoとなる。

(もっと読む)

携帯情報装置

【課題】携帯情報装置の消費電力を抑える。

【解決手段】表示装置とCPUと外部入力端子とを有し、表示装置はソース信号線駆動回路と、複数の画素とを有し、複数の画素はそれぞれ、画素に入力される映像信号を記憶する機能を有する回路と、画素電極とを含み、外部入力端子から映像表示をかえるための信号の入力が一定期間行われない場合、CPUによって表示装置が静止画を表示していると判断され、表示装置が静止画を表示するとき、CPUからソース信号線駆動回路へのスタートパルス、クロック信号、及び映像データ信号の供給が停止される。

(もっと読む)

電気光学装置および電子機器

【課題】複数の信号線駆動回路が配線ブロック内の各信号線への階調電圧の印加順序の更新制御を行う電子機器において、各信号線駆動回路間で階調電圧の印加順序が不一致になることを防止する。

【解決手段】電気光学装置100R、100Gおよび100Bの各制御回路30は、互いに非同期に階調電圧の印加順序の更新制御を行う。ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対し、階調電圧の印加順序の更新周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングで、初期化用同期信号ISYNCを供給し、電気光学装置100R、100Gおよび100Bの各制御回路30において、階調電圧の印加順序の更新制御の動作を一斉に初期化させる。

(もっと読む)

液晶ディスプレイのゲート制御信号の生成方法及び装置

【課題】フレキシブルプリント回路基板の枚数を削減したCOGLCDと,そのLCDについての伝送方法および,フレキシブルプリント回路基板の枚数を削減するためのゲート制御信号の生成方法を提供する。

【解決手段】画素のアレイを有するパネルと、イメージデータ及びソース制御信号を出力するタイミングコントローラと、一連のソースドライバと、ゲートドライバとを備える液晶ディスプレイが開示される。複数のソースドライバのうちの1つのソースドライバは、少なくとも1つのソース制御信号を参照することによってゲート制御信号を生成してゲートドライバへと送信するように選択される。これにより、ゲートドライバは、ソースドライバとともに、パネルの画素を駆動することができる。

(もっと読む)

イメージディスプレイシステムおよび方法

【課題】イメージディスプレイシステムと方法を提供する。

【解決手段】

イメージディスプレイシステムと方法を提供する。システムの画素構造は、ラッチ回路とディスプレイ回路を有する。スキャンライン信号に従って、ラッチ回路は、データライン信号を受信し、一時的に保存する。ディスプレイ回路は、リセット信号とセット信号に従って作動する。リセット信号に従って、ディスプレイ回路は、画素の液晶分子の制御端の電圧レベルをリセットする。セット信号に従って、ディスプレイ回路は、ラッチ回路に保存されたデータライン信号を受信し、液晶分子の制御端を調整して、これにより、液晶分子が回転し、画素の期待されるイメージが表示される。リセット信号の有効区間は、最後のスキャンライン信号が無効になった後、且つ、セット信号が有効になる前に配置される。

(もっと読む)

液晶表示素子及びその駆動方法

【課題】ランプ信号を歪ませてしまうことで生じるいわゆる「黒浮き」の画像ノイズを低減し、高品位な画像表示を可能とする。

【解決手段】正極性用データ線Di+には図示しない正極性用ビデオスイッチからの正極性用ランプ信号RAMP+が供給され、負極性用データ線Di-には図示しない負極性用ビデオスイッチからの負極性用ランプ信号RAMP-が供給される。スイッチSWiは、正極性用データ線Di+と負極性用データ線Di-との間に設けられ、i列目の2つのビデオスイッチが同時にオンになる直前のタイミングで一度だけオンとなり、これにより正極性用データ線Di+及び負極性用データ線Di-に充電された電圧を正負で中和する機能を持つ。ランプ信号期間の終了後から、次の水平走査期間の開始時刻までの間の僅かの期間内で、スイッチSWiがオンとされ、正極性用データ線Di+と負極性用データ線Di-とを短絡する。

(もっと読む)

光センサおよび表示装置

【課題】精度の高いセンサ出力を得ることのできる、センサ回路または表示装置を提供する。

【解決手段】光検出素子と、蓄積ノードを介して接続され光検出素子に流れた電流に応じて電荷を蓄積する蓄積部と、リセット信号を蓄積ノードへ供給するリセット信号配線と、読み出し信号を蓄積ノードへ供給する読み出し信号配線と、出力配線に接続され蓄積ノードと出力配線を導通させて蓄積ノードの電位に応じた出力信号を出力するセンサスイッチング素子と、蓄積ノードと所定の電圧が供給される所定電圧電極との間の接続および非接続を切り替えるスイッチ素子であってタッチ操作による押圧を受けると接続状態になるスイッチ素子と、スイッチ素子と蓄積ノードとの間に接続されスイッチ素子と蓄積ノードとの間の導通または非導通状態を切り替える制御信号が入力される制御電極を備える制御スイッチング素子とを備える。

(もっと読む)

液晶表示装置の調整方法、その調整方法を適用して調整することにより製造した液晶表示装置、およびその調整方法を含む液晶表示装置の製造方法

【課題】本発明は、焼付き量が最小となるような直流電圧成分を容易に求めて液晶に印加する電圧を調整することが可能な液晶表示装置の調整方法、その調整方法を適用して調整することにより製造した液晶表示装置、およびその調整方法を含む液晶表示装置の製造方法を提供することを目的としている。

【解決手段】本発明による液晶表示装置の調整方法は、液晶に印加される印加電圧を調整する液晶表示装置の調整方法であって、(a)フレームレートコントロール法を用いた、直流電圧成分を含む表示画像を生成する工程と、(b)工程(a)にて生成された表示画像を表示する工程と、(c)工程(b)にて表示された表示画像の表示品位と、直流電圧成分との関係を評価する工程と、(d)工程(c)による評価の結果に基づいて、印加電圧を調整する工程とを備えることを特徴とする。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

表示パネル及びそれを含む表示装置

【課題】隣接する二つの画素が一つのデータラインを共有する構造を有する表示パネルにおいて、ベーゼル幅を低減できる表示パネルを提供する。

【解決手段】表示パネルは複数の画素、データライン、一対のゲートライン、第1ゲート駆動回路及び第2ゲート駆動回路を含む。複数の画素は表示領域に配置され、複数の画素行と複数の画素列からなる。データラインは列方向に伸長し、二つの画素列ごとに配置される。一対のゲートラインは行方向に伸長し、一つの画素行ごとに各々、画素行の第1側部及び第2側部に配置される。第1ゲート駆動回路は表示領域の第1周辺領域に形成され、画素行の第1側部に配置された第1ゲートラインにゲート信号を提供する第1ステージを含む。第2ゲート駆動回路は第1周辺領域と向き合う表示領域の第2周辺領域に形成されて、画素行の第2側部に配置された第2ゲートラインにゲート信号を提供する第2ステージを含む。

(もっと読む)

電気光学装置及び電子機器

【課題】ダミー走査線を選択する期間を短くする。

【解決手段】走査線駆動回路200は、第1行〜第4行の走査線に走査信号G1〜G4を出力する。これらの信号波形は同一である。また、走査線駆動回路200は、第605行〜第608行の走査線に信号波形が同一となる走査信号G605〜G608を出力する。従って、第1行〜第4行の走査線は同じ水平走査期間で選択され、第605行〜第608行の走査線は同じ水平走査期間で選択される。これによって、ダミー走査線を選択する期間を短くすることができる。

(もっと読む)

ソースドライバ、それを備えるディスプレイ装置、及びその駆動方法

【課題】 ガンマ電圧間の非単調性を除去可能なソースドライバ、それを備えるディスプレイ装置、及びその駆動方法を提供する。

【解決手段】 ディスプレイ装置が備えるソースドライバ100は、それぞれm個の階調電圧を含むk個のグローバルガンマ電圧信号を出力するグローバルブロック170と、映像データに基づいてk個のグローバルガンマ電圧信号のうち何れか1つを選択し、選択されたグローバルガンマ電圧信号に含まれた特定階調電圧をソースラインS1からSsまでに出力するチャンネルドライバ500と、を備える。グローバルブロック170は、第1階調電圧から第m階調電圧までのそれぞれ階調電圧を出力する前に、出力される階調電圧より高いプリエンファシス電圧を所定時間出力する。これにより、ディスプレイ装置は、ガンマアンプを使用することなく各チャンネルドライバを十分に駆動することができる。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、基板上の積層構造の単純化を図る。

【解決手段】電気光学装置は、第1方向(X方向)及び該第1方向に交わる第2方向(Y方向)に沿って配列された複数の画素と、画素毎に夫々対応して設けられた複数のトランジスター(Tr)と、第1方向に沿って配列された画素からなる画素群毎に設けられ、トランジスターのゲート電極に電気的に夫々接続された複数の走査線(11)とを備え、複数のトランジスターのうち第2方向において隣り合う画素に設けられたトランジスターは電気的に互いに直列接続されており、互いに直列接続されたトランジスターのうち第2方向における一端に位置するトランジスターに画像信号を供給する画像信号供給部を備える。

(もっと読む)

半導体装置

【課題】簡素でかつ占有面積の小さな駆動回路を提供すること。

【解決手段】本発明のシフトレジスタ回路は、複数のレジスタ回路を有している。各レジスタ回路は、クロックドインバータ回路およびインバータ回路を有している。クロックドインバータ回路の出力信号がインバータ回路の入力信号となるよう両者が直列に接続されている。さらに、レジスタ回路は、インバータ回路の出力信号が伝達される信号線を有している。該信号線には接続されている素子が多く寄生容量が大きいため高負荷である。本発明のシフトレジスタ回路は、信号線の寄生容量が大きいために高負荷であることを用いている。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、コントラスト及び明るさを選択的に高める。

【解決手段】電気光学装置は、走査線(11)と重なるように設けられ、且つデータ線が延びる方向で互いに隣り合う画素電極間に位置する間隙領域を含む領域に重なるように形成された導電電極(400)と、基準電位に対して極性が所定期間毎に反転する画像信号をデータ線に供給する画像信号供給部(101、95、7)と、導電電極に導電電極電位を供給する導電電極電位供給部(300)とを備える。導電電極電位供給部は、画素電極に供給される画像信号と同一極性の電位を有するように、導電電極電位を制御する第1動作モードと、導電電極が基準電位と同一の電位を有するように導電電極電位を制御する第2動作モードとを有する。

(もっと読む)

液晶表示装置

【課題】ソースフォロワ出力の線形領域を従来より拡大する。

【解決手段】画素10内のソースフォロワ用PMOSトランジスタTr13及びTr14は、ゲートが保持容量Cs1、Cs2に接続されて常にオン状態で使用されるため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのみが+0.5Vに設定され、ノーマリーオン状態とされる。ソースフォロワ用PMOSトランジスタTr13及びTr14の電流値は定電流負荷トランジスタTr7で制御し、オンオフは定電流負荷トランジスタTr7とスイッチング用NMOSトランジスタTr5、Tr6で制御する。また、トランジスタTr5、Tr6が介在し出力可能の電圧範囲が存在するため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのシフトによって線形性を保つ領域が最大になるように最適化する。

(もっと読む)

141 - 160 / 1,869

[ Back to top ]