Fターム[5C006BC12]の内容

液晶表示装置の制御 (150,375) | 表示器駆動回路 (12,655) | 信号(セグメント)側駆動回路 (2,784) | デジタル駆動回路 (1,138)

Fターム[5C006BC12]に分類される特許

61 - 80 / 1,138

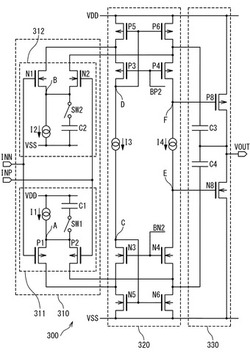

演算増幅回路、液晶パネル駆動装置

【課題】演算増幅回路を安定に動作させつつスルーレートを向上させる。

【解決手段】第1差動増幅部(311)は、P型差動対(P1/P2)のソースと正側電源電圧(VDD)との間に、並列に接続される第1電流源(I1)と第1容量(C1)とを備え、P型差動対(P1/P2)のソースと第1容量(C1)との間に挿入される第1スイッチ(SW1)をさらに備える。第2差動増幅部(312)は、N型差動対(N1/N2)のソースと負側電源電圧(VSS)との間に、並列に接続される第2電流源(I2)と第2容量(C2)とを備え、N型差動対(N1/N2)のソースと第2容量(C2)との間に挿入される第2スイッチ(SW2)をさらに備える。第1スイッチ(SW1)と第2スイッチ(SW2)とは、第1差動増幅部(311)および第2差動増幅部(312)に入力される入力差動信号に同期して交互に回路を開閉する。

(もっと読む)

ソースドライバおよび液晶表示装置

【課題】ソースラインに接続されずに余る電位出力端が生じる場合でも、タイミングコントローラによるスタートパルス入力後に、ダミーデータなしで、実際の画像データを読み込むことができるソースドライバを提供する。

【解決手段】シフトレジスタ1は、ラッチ部5に対してデータ読み込み指示信号を出力するデータ読み込み指示信号出力部2を複数個備える。第1スイッチ3は、タイミングコントローラからのスタートパルスを一番左のデータ読み込み指示信号出力部2に入力するか、左から4番目のデータ読み込み指示信号出力部2に入力するかを切り替え可能である。第2スイッチ4は、スタートパルスを左から802番目のデータ読み込み指示信号出力部2に入力するか、左から799番目のデータ読み込み指示信号出力部2に入力するかを切り替え可能である。

(もっと読む)

カラー表示装置,液晶表示装置、および半透過液晶表示装置

【課題】

カラー表示装置において赤色(R),緑色(G),青色(B)副画素に加えて、白色(W)副画素を配線数を増加させずに追加すると単位面積あたりの色毎の画素数が減るために解像度が劣化する。

【解決手段】

視感度に応じて副画素の面積および数を調整する。具体的には、視感度の相対的に低い赤色(R)及び青色(B)副画素の面積を視感度の相対的に高い緑色(G)及び白色(W)副画素の面積の略2倍とし、緑色(G)及び白色(W)副画素の数を赤色(R)及び青色(B)副画素の2倍とする。大きい方の副画素は複数の単位副画素から構成される。小さい方の副画素は一つの単位副画素から構成される。

(もっと読む)

表示装置、中間階調処理回路及び中間階調処理方法

【課題】 簡単な構成で表示画面上でフリッカが生じないように中間階調処理を行うことができる表示装置、中間階調処理回路及び中間階調処理方法を提供する。

【解決手段】 入力画像データが表す所望の輝度レベルが所定レベル以下である場合に、連続して表示される同一輝度レベルの画像データの数を既定値以下に調整する中間階調制御手段を備える。また、入力画像データが表す輝度レベルが所定レベル以下でかつ複数の表示輝度レベル以外であるとき選択した表示輝度レベルが所定の周期より大なる期間以上に亘って同一の表示輝度レベルにならないように低輝度側に直近の表示輝度レベル及び高輝度側に直近の表示輝度レベル各々の選択の頻度を互いに近付ける中間階調制御手段を備える。

(もっと読む)

回路面積を節減可能なディスプレーパネルの駆動回路

【課題】回路面積を節減可能なディスプレーパネルの駆動回路の提供。

【解決手段】回路面積を節減可能なディスプレーパネルの駆動回路は、複数のデジタルアナログ転換回路200により入力画素データをそれぞれ転換し、画素信号を発生し、複数の駆動ユニット202は各デジタルアナログ転換回路200にそれぞれ接続し、画素信号に基づき駆動信号を発生し、駆動信号をディスプレーパネル2に伝送し画面を表示させ、複数の昇圧ユニット204は各駆動ユニット202に接続し、制御信号に基づき供給電圧を発生し、しかも供給電圧を各駆動ユニット202に提供し、昇圧ユニット204により供給電圧をそれぞれディスプレーパネル2の複数の駆動ユニット202に提供し、これにより外付けの保存キャパシタの面積を縮小でき、さらには保存キャパシタの外付けを不要とでき、回路面積節減の目的を達成することができる。

(もっと読む)

立体表示装置および立体表示方法

【課題】表示映像の画質を高めることができる立体表示装置を得る。

【解決手段】複数の開閉部12A,12Bからなる開閉部グループを複数含み、グループ間で互いに異なるタイミングで個別に開閉動作する光バリア部と、複数の異なる視点の視点画像に基づいて、各開閉部グループの開動作タイミングに応じて、複数の開閉部グループにそれぞれ対応する複数の系列の複合画像(複合フレーム画像FA,FB)を生成する複合画像生成部と、各開閉部グループの開閉動作に同期して、対応する系列の複合画像を表示する表示部とを備える。上記複合画像生成部は、少なくとも1つの系列の複合画像を補間によって生成するものである。

(もっと読む)

マルチチャネル半導体装置及びそれを具備したディスプレイ装置

【課題】別途のプローブ接続用パッドなしに、出力チャネルの個数より少ない個数のプローブを接続して多数の出力チャネルの出力信号をモニタリングすることができるマルチチャネル半導体装置及びそれを具備するディスプレイ装置を提供する。

【解決手段】少なくとも1つの出力バッファを具備する複数のバッファ・グループ;少なくとも1つの出力パッドを具備する複数のパッド・グループ、及び複数のバッファ・グループ;複数のパッド・グループとの連結を制御するチャネル・スイッチング部;を含むマルチチャネル半導体装置であり、該複数のパッド・グループのうち1つのパッド・グループは、第1動作モードで、対応するバッファ・グループの出力信号を出力し、第2動作モードで、複数のバッファ・グループの出力信号を順次に出力する。

(もっと読む)

駆動回路、電気光学装置及び電子機器

【課題】 電荷の再利用を行う場合に、より一層の低消費電力化を実現できる駆動回路、電気光学装置及び電子機器を提供する。

【解決手段】 駆動回路は、ゲート線と第1のソース線により特定される第1の画素電極と、ゲート線と第2のソース線により特定される第2の画素電極と、第1、第2の画素電極と電気光学物質を介して対向して設けられる対向電極とを含む電気光学装置を駆動するための駆動回路であって、共用ラインと、第1、第2のソース線を共用ラインに短絡させるソース線短絡回路と、共用ラインと対向電極出力ノードとの間に設けられたノード短絡スイッチと、第1の容量素子接続ノードと対向電極電圧出力ノードとの間に設けられる対向電極電荷蓄積用スイッチと、第2の容量素子の一端と接続可能な第2の容量素子接続ノードと共通ラインとの間に設けられるソース電荷蓄積用スイッチとを含む。

(もっと読む)

立体画像表示方法及び立体画像表示方法により立体画像を表示する表示装置

【課題】立体画像のクロストークを改善するための立体画像表示方法及び立体画像表示方法により立体画像を表示する表示装置を提供すること。

【解決手段】立体画像表示方法は第N(Nは、自然数)フレームの間、k(kは、2以上の自然数)個の表示ブロックに分割した表示パネルに左眼画像を出力し、各表示ブロックに該当する左眼画像の出力が完了した時点から第1設定時間が経過した時点に各表示ブロックに光を照射し、第N+1フレームの間、表示パネルに右眼画像を出力し、各表示ブロックに該当する右眼画像の出力が完了した時点から第2設定時間が経過した時点に各表示ブロックに光を照射する。

(もっと読む)

立体映像表示装置

【課題】高い階調表示性能、左右画像のチャンネル分離性能を確保できる立体映像表示装置を提供する。

【解決手段】信号処理部101は入力される3D映像信号から左目用信号、右目用信号が時間的に交互に並べ替えられた信号に変換する。液晶表示素子の駆動装置は、左目用信号、右目用信号のそれぞれのデータに別々のフレームレートコントロールテーブルにおけるフレーム番号を割り当てることによりフレームレートコントロールを行うフレームレートコントロール部24を備える。液晶表示素子6は駆動装置で駆動され、照明光学系は液晶表示素子に照明光を入射させ、投射レンズは液晶表示素子から射出された変調光を投射する。

(もっと読む)

飽和電圧と閾値電圧間の変調を達成するための多重ピクセルを備えたディスプレイ

【課題】ピクセルに記憶されたデータを迅速に反転可能なマルチビットデータワードを表示する液晶ディスプレイを提供する。

【解決手段】ピクセル電極612、記憶素子702、第1の電圧供給端子622、第2の電圧供給端子624、共通電極、およびマルチプレクサ704を含み、マルチプレクサが、記憶素子702のうちの関連付けられた1つに記憶されたデータビットの値に応答して、ピクセル電極612のうちの関連付けられた1つを第1の電圧供給端子622および第2の電圧供給端子624のうちの1方と選択的に接続し、記憶されるビットの重要性に依存する時間の間、マルチビットデータワードの各ビットを記憶素子702に連続的に書き込み、ならびに各ビットを記憶素子702に記憶しつつ、第1の所定の電圧を第1の電圧供給端子622に、第2の所定の電圧を第2の電圧供給端子624に、そして第3の所定の電圧を共通電極にアサートする。

(もっと読む)

表示装置

【課題】 保持回路110へのデータの誤書き込みを防止すると共に、低消費電力化及び表示画素の高集積化を図る。

【解決手段】 表示画素にデジタル映像データを保持するための保持回路を備えた表示装置において、データ書き込み時には、保持回路110に供給される電源電圧をデータ保持に必要な最小電圧に設定し、書き込み終了後に、昇圧回路95により保持回路110に供給される電源電圧を昇圧する。保持回路110はゲート信号線51から入力される信号に応じて、ドレイン信号線61からのデジタル映像信号が書き込まれると共に該デジタル映像信号を保持する。そして、保持回路110に保持された信号に応じて表示が行われる。

(もっと読む)

表示装置

【課題】 表示パネルの外部回路の構成をシンプル化すると共に、低消費電力化を図る。

【解決手段】 ゲート信号線51から入力される信号に応じてドレイン信号線61からのデジタル映像信号を保持する保持回路110を設ける。保持回路110からの信号に応じて2つの信号(信号Aと信号B)のいずれかを選択して画素電極80に供給する信号選択回路120を設ける。そして、信号A、信号Bを作成する基準電圧発生回路500を表示パネル100内に設ける。デジタル表示モード時には、基準電圧発生回路500により、表示画素80に印加する信号を作成しているので、これらの信号A及び信号Bを外部から供給する必要がない。

(もっと読む)

データ処理装置

【課題】容易にEMIノイズを大きく低減することのできるデータ処理装置を実現する。

【解決手段】データ処理装置(201)は、サンプリング回路(50、50a〜50l)によってデータバス(30)を構成する各データライン(30a〜30c)のデータ(D0、D1、D2)をサンプリングした後、次のデータ(D0、D1、D2)が各データライン(30a〜30c)に供給される前に、各データライン(30a〜30c)の2本以上どうしを互いに短絡させるスイッチ(6)を備えている。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

半導体装置

【課題】画素部や信号線駆動回路が形成された基板と、ドライバICとの接続配線数を低減させる。

【解決手段】信号線駆動回路は第1乃至第3のトランジスタを有し、第1乃至第3のトランジスタは第1乃至第3の信号線と電気的に接続している。第1乃至第3の信号線は画素部へ延びている。第1乃至第3のトランジスタは共通して、ドライバICの第1端子と電気的に接続している。このような構成により、接続配線数を1/3に低減することができる。

(もっと読む)

表示パネル駆動装置

【目的】消費電力の増加及びコスト増を招くことなく、表示パネルの駆動を担う複数のドライバチップ各々を経由させて、デューティ比の安定したクロック信号を各ドライバチップに供給することが可能な表示パネル駆動装置を提供することを目的とする。

【構成】本発明においては、表示パネルの信号線各々に入力映像信号に基づく画素駆動電圧をクロック信号に応じたタイミングで印加する信号線ドライバを、夫々クロックラインによってカスケード接続された複数のドライバチップに分割して構築するにあたり、各ドライバチップに、以下の如きクロック送出部を設ける。クロック送出部は、クロックラインを介して供給されたクロック信号の周期を1/2に分周した分周クロック信号と、この分周クロック信号を所定の遅延時間だけ遅延させた遅延分周クロック信号との論理レベルが互いに同一である期間中は第1レベル、互いに異なる場合には第2レベルを有する整形クロック信号を次段のドライバチップに送出する。

(もっと読む)

液晶駆動用のソースドライバのオフセットキャンセル出力回路

【課題】液晶駆動用のソースドライバのオフセットキャンセル出力回路を提供する。

【解決手段】基準電圧が非反転入力端に印加されたオペアンプと、反転入力端に各々の一端が接続された入力コンデンサ及び出力コンデンサと、反転入力端とオペアンプの出力端との間に接続された第1の電界効果トランジスタを有し、リセット動作時に入力コンデンサ及び出力コンデンサ各々にオフセット電圧を蓄電させ、通常出力動作時に入力コンデンサの他端に階調電圧を印加しかつ出力コンデンサの他端をオペアンプの出力端に接続するスイッチ素子回路と、を備え、リセット動作時及び通常出力動作時に第1の電界効果トランジスタの基盤に基準電圧に等しい第1の電位を印加し、通常出力動作中の階調電圧の切り替え時に第1の電界効果トランジスタのソース/ドレインから基盤に流れるリーク電流を防止するように基盤に第1の電位とは異なる第2の電位を第1の電位に代えて印加する。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】駆動回路76は、入力電位VIよりも所定電圧高い電位をノードN22に出力するレベルシフト回路61と、ノードN22の電位よりも所定電圧低い電位をノードN30に出力するプルアップ回路30と、入力電位VIよりも所定電圧低い電位をノードN27に出力するレベルシフト回路63と、ノードN27の電位よりも所定電圧高い電位をノードN30に出力するプルダウン回路33と、一方電極がそれぞれ信号φB,/φBを受け、他方電極がそれぞれノードN22,N27に接続されたキャパシタ76,77とを備える。入力電位VIの変化時、信号φB,/φBは、それぞれパルス的に「H」レベルおよび「L」レベルになる。したがって、低消費電流化と応答速度の高速化が図られる。

(もっと読む)

表示装置

【課題】1つの表示装置で、アナログ表示(動画像表示)とデジタル表示(静止画像表示)という2種類の表示モードに対応することを可能にすると共に、表示システムの大幅な低消費電力を図る。

【解決手段】 アナログ表示を行う第1の表示回路と、デジタル表示を行う第2の表示回路を備え、アナログ表示を停止するように切り換えるときには、外部から入力されるモード設定信号DHに基づき、ドレイン信号線61と第1の表示回路との接続を切ると共に、モード設定信号DHを遅延することにより生成される停止制御信号LAに応じて、不要な回路(DAコンバータ310、演算増幅器311、タイミングコントローラ305)への電源供給を停止する。

(もっと読む)

61 - 80 / 1,138

[ Back to top ]