Fターム[5E001AJ02]の内容

セラミックコンデンサ (14,384) | 製法−部位 (2,228) | 誘電体 (927)

Fターム[5E001AJ02]に分類される特許

1 - 20 / 927

セラミック電子部品及びその製造方法

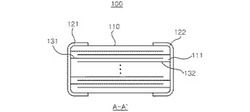

積層セラミック電子部品及びその製造方法

【課題】一定水準のESRを具現しながら、同一容量の積層セラミック電子部品におけるQ値の選択幅を広げる。

【解決手段】複数の誘電体層111が積層されたセラミック素体110と、セラミック素体110の内部に形成された第1及び第2内部電極131、132とを含み、第1及び第2内部電極131、132は、銅が80から99.9wt%、及び、ニッケルが0.1から20wt%を含み、周波数が1000MHz以下である積層セラミック電子部品を形成する。

(もっと読む)

高誘電率セラミックスの製造方法

【課題】ニッケル内部電極を使用した積層セラミックコンデンサに適用可能であり、かつ100nm未満の粒径のチタン酸アルカリ土類金属化合物を主原料としても誘電率が向上しうる高誘電率セラミックスの製造方法を提供する。

【解決手段】平均粒子径が50nm以上100nm未満であるチタン酸アルカリ土類金属化合物とランタン化合物とを混合する工程と、前記混合する工程で得られた混合物を、不活性ガス雰囲気下、1000℃以上1200℃未満の温度で焼成する工程と、を有し、前記ランタン化合物の混合量が、前記チタン酸アルカリ土類金属化合物に対するランタンの原子数換算で0.5〜1.5at%である、高誘電率セラミックスの製造方法。

(もっと読む)

積層セラミックキャパシタの製造方法

【課題】本発明は、積層セラミックキャパシタの製造方法に関する。

【解決手段】本発明は、内部電極が印刷されたセラミックグリーンシートを積層してセラミック積層体を形成する段階と、上記セラミック積層体に熱圧搾を加える段階と、上記セラミック積層体を切断する段階と、上記セラミック積層体にスラリーを浸透させる段階と、上記セラミック積層体に浸透されたスラリーを乾燥する段階と、を含むことができる。本発明によると、積層セラミックキャパシタの製造工程時に発生するクラック(crack)が除去されて信頼性に優れた積層セラミックキャパシタを製作することができる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、複数の誘電体層が積層されたセラミック素体と、上記複数の誘電体層に形成される複数の内部電極と、上記内部電極が形成されない誘電体層のマージン部に形成され、気孔率が10%以下であるマージン部誘電体層と、上記セラミック素体の外表面に形成される外部電極とを含んでよい。

(もっと読む)

積層電子部品の製造方法およびその方法に用いる積層ユニットの製造方法

【課題】いわゆる多層塗布工法を用いて積層電子部品を製造する際に、シートアタック現象が発生せず、結果として得られる電子部品のショート不良率が少ない積層電子部品の製造方法と、その製造方法に用いられる積層ユニットと、その製造方法を提供することである。

【解決手段】第1グリーンシート10aと、第1グリーンシート10aの上に形成された第1電極パターン12aと、第1電極パターン12aが形成された第1グリーンシート10aの表面に形成された第2グリーンシート10bと、第2グリーンシート10bの上に形成された第2電極パターン12bと、を有する積層ユニットである。第1グリーンシート10aに含まれるバインダ樹脂が、第1ブチラール系樹脂であり、第2グリーンシート10bに含まれるバインダ樹脂が、前記第1ブチラール系樹脂とは異なる第2ブチラール系樹脂である。

(もっと読む)

静電容量素子の製造方法

【課題】グリーンシートのパターンの生成を極力少なくし、一つのパターンのグリーンシートから複数の異なるグリーンシートを作製する静電容量素子の製造方法を提供する。

【解決手段】誘電体シート及び該誘電体シートに導電体塗布用の所定のパターン形状を有するマスクを用意して、誘電体シート上に基本パターングリーンシートを作製する。その後、基本パターングリーンシートを例えば180°回転したパターンと、この基本パターングリーンシートを裏返した裏返しグリーンシートを作製し、これらを任意に積層して加圧、高温焼成することにより静電容量素子を製造する。これにより、製造工程の品質管理を容易にすると共に、設備投資面のコスト削減などの生産性の向上を図ることができる。

(もっと読む)

セラミック電子部品の製造方法

【課題】信頼性の高いセラミック電子部品を製造可能な方法を提供する。

【解決手段】第1のペースト層25を第1の側面24cの上に形成し、第1のペースト層25に膨潤体26を接触させて第1のペースト層25に含まれる分散媒を膨潤体26に吸収させながら第1のペースト層25を乾燥させる第1のペースト層形成工程を行う。第2のペースト層を第2の側面24dの上に形成し、第2のペースト層に膨潤体26を接触させて第2のペースト層に含まれる分散媒を膨潤体に吸収させながら第2のペースト層を乾燥させる第2のペースト層形成工程を行う。

(もっと読む)

グラビア印刷装置

【課題】被印刷シート上への印刷ペーストの転写量を部分的に調整することができるグラビア印刷装置を得る。

【解決手段】グラビア印刷装置20は、表面に凹部24を有する版胴22と、版胴22と対向して配置される圧胴30とを含む。貯留槽26に蓄えられた導電性ペースト28を凹部24に充填し、版胴22と圧胴30との対向部において、セラミックグリーンシート32上に導電性ペースト28を転写する。版胴22の一部または圧胴30の一部を磁化することにより、磁化された部分における導電性ペースト28の転写量を調整する。

(もっと読む)

積層セラミック電子部品の製造方法

【課題】生のセラミック素体に導電性ペーストを塗布した際に生じる膨潤、歪みを抑制し得る、積層セラミック電子部品の製造方法を提供する。

【解決手段】第2のセラミックグリーンシート20bに含まれる有機バインダーの重合度をAとし、第2のセラミックグリーンシート20bに含まれる可塑剤の体積含有率をBとしたときに、180.56≦A/Bとなる。

(もっと読む)

誘電体磁器組成物および電子部品

【課題】比較的に高い比誘電率及び耐電圧を有し、しかも高温領域を含む広い温度範囲(−55〜400℃)において容量温度特性が良好である誘電体磁器組成物を提供する。

【解決手段】一般式KNbO3で表される第一の相と、一般式BaTiO3で表される第二の相との混晶体から成る主成分を有し、副成分としてMn、Siの元素を含有する。KNbO3とBaTiO3との混晶体から成る主成分とすることで、100℃以下では、BaTiO3が有する高い比誘電率を利用し、150℃以上では、KNbO3が有する高い比誘電率を利用することができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、誘電体層と内部電極との接着力に優れた積層セラミック電子部品に関する。

【解決手段】本発明は、誘電体層を含むセラミック本体と、当該セラミック本体内で当該誘電体層を介して対向配置される内部電極と、を含み、上記誘電体層の平均厚さをtd、上記内部電極の平均厚さをteとすると、0.1μm≦te≦0.5μmであり、(td+te)/te≦2.5を満足し、上記内部電極の中心線平均粗さをRa、十点平均粗さをRzとすると、5nm≦Ra≦30nm、150nm≦Rz≦td/2及び8≦Rz/Ra≦20を満足する積層セラミック電子部品を提供する。本発明によると、誘電体層と内部電極との接着力及び耐電圧特性が向上して信頼性に優れた大容量積層セラミック電子部品の具現が可能となる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、上記セラミック素体の内部に形成され、上記セラミック素体の第1面及び上記第1面と連結された第3面または第4面に露出し、上記第1面に露出した領域のうち一部が互いに重なる引出し部を有する第1及び第2内部電極と、上記セラミック素体の第1面及び上記第1面から延長されて上記第1面と連結された第3面または第4面に形成され、上記引出し部と夫々連結される第1及び第2外部電極と、上記セラミック素体の第1面、上記第1面と連結された第3面及び第4面に形成される絶縁層と、を含む。

(もっと読む)

セラミックペーストおよびセラミックグリーンシート

【課題】ポリビニルアセタールを含み、塗膜強度の向上と粘度安定性とが両立した積層セラミックコンデンサ用セラミックペーストを提供する。

【解決手段】以下の式(I)に示す部分構造を分子内に3以上有する有機ホウ素化合物を含むペーストとする。式(I)において、mは0または1、nは1〜3の整数、R1およびR2は互いに独立して、水素原子または置換されていてもよいアルキル基である。R1およびR2は、互いに結合していてもよい。 (もっと読む)

(もっと読む)

積層コンデンサ及びコンデンサ内蔵配線基板

【課題】特性が異なる複数の領域からなる積層コンデンサを一体的に作製し、周波数特性の広帯域化を容易に実現可能な積層コンデンサを提供する。

【解決手段】本発明の積層コンデンサは、誘電体層20〜22と内部電極層30〜33とを交互に積層してなり、第1領域R1及び第2領域R2を含むコンデンサ本体部と、アレイ状に配置された全貫通型のビア導体40、41、50、51と、その両端部に接続される外部電極60、61、70、71を備えている。第1ビア導体群であるビア導体40、41は、第1領域R1及び第2領域R2の内部電極層30〜33と電気的に接続され、第2ビア導体群であるビア導体50、51は、第1領域R1の内部電極層30、31と電気的に接続され、かつ第2領域R2の内部電極層32、33と電気的に接続されない。ビア導体50、51は、第2領域R2におけるビア径が第1領域R1におけるビア径よりも小さくなるように形成される。

(もっと読む)

積層型コンデンサ

【課題】材料的な制約を受けることなく且つ汎用的な構造を含む場合にも適用可能であって、電歪振動を抑制することが可能な積層型コンデンサを提供すること。

【解決手段】誘電体セラミックスによって形成された素体及びその素体内部においてセラミックス層を挟んで重なりあうように配置された複数の内部電極4a,4bを有する積層体2と、を備え、複数の内部電極4a,4bを含むコンデンサ領域CAと、複数の内部電極4a,4bによって生じる電歪現象を低減させ音鳴きを抑制するための第一抑制領域EA及び第二抑制領域DAとが形成されており、第一抑制領域EAはコンデンサ領域CAに隣接し、第二抑制領域DAの厚みは複数の内部電極4a,4bの配置態様に応じて定められるものである。

(もっと読む)

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

積層型電子部品の製造方法

【課題】特性のばらつきが少なく、小型で高容量の電子部品を、低コストで製造することが可能な積層型電子部品の製造方法を提供すること。

【解決手段】グリーンシートに所定パターンで電極ペースト膜を形成する工程と、グリーンシートを積層して積層体4aを準備する工程と、積層体を、支持基板36の粘着層34に付着する工程と、積層方向と直交する第1方向に沿って、支持基板は切断せずに積層体を切断して端子電極接続面15a,15bを形成し、積層方向および第1方向と直交する第2方向に沿って、積層体および支持基板を切断してギャップ面16を形成し、支持基板と一体化された棒状体38を得る工程と、ギャップ面が同一平面に配置されるように複数の棒状体38を並べ、ギャップ面16に、セラミックペースト42を塗布する工程と、粘着層の粘着力を弱め、積層体2aと支持基板36とを分離する工程とを有することを特徴とする。

(もっと読む)

積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】高さ方向に沿って2枚以上の外層ダミー導体7を所定間隔で連続的に配置することにより、複数の外層ダミー群31を形成する。外層ダミー群31内における外層ダミー導体7同士の間隔をd、外層ダミー群31同士の間隔をg、としたとき、gがdより大きくなるようにする。これによって、めっき析出ポイントを確保しつつ、外層ダミー群31同士の間隔を遠ざけることにより、外層ダミー導体7による内部電極3,4の押圧を緩和することができ、局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

積層セラミックコンデンサ

【課題】耐湿性の良好な積層セラミックコンデンサを提供する。

【解決手段】内部電極21が形成された複数の第1のセラミック層22を積層してなる有効層20と、前記有効層20を挟むように内部電極が形成されていない複数の第2のセラミック層31を積層してなる一対の保護層30とを有する積層体10と、該積層体10の外面に形成され前記内部電極21と電気的に接続した外部電極40とを備えた積層セラミックコンデンサにおいて、前記第1のセラミック層21及び第2のセラミック層31はそれぞれSiO2が添加されたセラミック材料からなり、且つ、前記保護層は相対的に互いにSiO2濃度が異なる複数の第2のセラミック層31H,31Lを積層してなる。

(もっと読む)

1 - 20 / 927

[ Back to top ]