Fターム[5E070AA11]の内容

通信用コイル・変成器 (13,001) | 類型、用途 (2,750) | 変成器、トランス (331)

Fターム[5E070AA11]の下位に属するFターム

フライバックトランス (9)

パルストランス (27)

分配器 (6)

インピーダンス変換器(バラン、平衝不平衝) (62)

Fターム[5E070AA11]に分類される特許

181 - 200 / 227

交互配置三次元オンチップ差動誘導器及び変成器

交互配置三次元(3D)オンチップ差動誘導器及び変成器が開示されている。交互配置3Dオンチップ差動誘導器及び変成器は、CMOS、BiCMOS、及び、SiGe技術のような主流標準的プロセスにおいて複数の金属層を最良に使用する。

(もっと読む)

(もっと読む)

基板搭載電子部品及びこれの実装認識方法

【目的】 その大きさに関係なく従来の画像認識方式の実装検査装置によって基板上での固定状態を検査可能であって、故に基板上での確実な固定を実現できる基板搭載電子部品及びその実装認識方法を提供する。

【構成】 基板の部品載置面に対向して載置される底面を有する本体部と、本体部からその底面に平行な方向に突出する少なくとも1つの突出部と、を有する。突出部はその端部において本体部の底面に平行な検出平面を有することを特徴とする。

(もっと読む)

磁気結合素子ならびに送受信装置

【課題】電気信号を送信する1次側コイル2と電気信号を受信する2次側コイル3とを電気的に絶縁分離した状態で対向配置してなる磁気結合素子1において、十分な性能を確保したうえで、比較的簡単かつ安価に製造できる構造とする。

【解決手段】多数枚の絶縁性の基板5〜9を積層した構成とされ、各コイル2,3が、各基板5〜9のうちの適宜の基板に形成される導電性の配線で形成されている。要するに、一般的な配線基板を積層した単純な構成として、従来例のような半導体プロセスを使用しないようにしている。

(もっと読む)

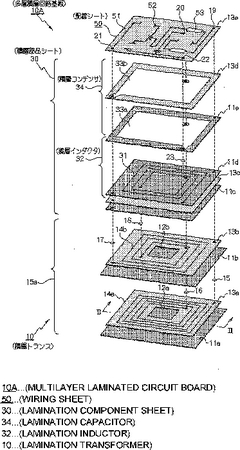

多層積層回路基板

本発明の多層積層回路基板10Aは、積層トランス10と、積層部品が形成された積層部品シート30と、回路パターンが形成された配線シート50とが積層されたものである。多層積層回路基板10Aでは、積層トランス10を内蔵することにより、積層トランス10のパッケージが省略されるとともに、積層トランス10と他の部品との配線も最小限になっている。  (もっと読む)

(もっと読む)

積層型磁性部品及びその製造方法

本発明の積層トランス10は、中央及び周縁にそれぞれ形成された中央磁性パターン11a及び周縁磁性パターン12aと中央及び周縁以外の部分に形成された非磁性体の誘電パターン13aとからなる混成シート14aと、同じく中央磁性パターン11b及び周縁磁性パターン12bと誘電パターン13bとからなる混成シート14bと、誘電パターン13aの一方の面上に位置する一次巻線15aと、誘電パターン13bの一方の面上に位置する二次巻線15bと、混成シート14a,14b、一次巻線15a及び二次巻線15bを挟持するとともに中央磁性パターン11a,11b及び周縁磁性パターン12a,12bを介して互いに接する磁性シート16a,16bとを備えたものである。  (もっと読む)

(もっと読む)

インダクタンス部品

【課題】 インダクタンス部品の高温アニールにより、大電流に対応した直流重畳特性の優れた、且つ、高い電力効率を有するインダクタンス部品を提供すること。

【解決手段】 軟磁性粉末とバインダーを含む混和物により構成される粉末磁性体内に、巻線コイル3が封じ込められて加圧成形されて一体化されるインダクタンス部品1であり、巻線コイル3の端子部5が300℃以上の液相線を有する金属を含む被覆により端子処理されていることを特徴とすることで、インダクタンス部品1の高温アニールを可能とした。

(もっと読む)

高周波用磁心及びそれを用いたインダクタンス部品

高周波用磁心は、一般式、(Fe1−a−bNiaCob)100−x−y−z(M1−pM’p)xTyBz[但し、0≦a≦0.30、0≦b≦0.50、0≦a+b≦0.50、0≦p≦0.5、1原子%≦x≦5原子%、1原子%≦y≦12原子%、12原子%≦z≦25原子%とし、且つ22≦(x+y+z)≦32、MはZr,Nb,Ta,Hf,Mo,Ti,V,Cr,Wから選ばれた少なくとも1種、M’はZn,Sn,R(RはYを含む希土類金属)から選ばれた少なくとも1種、及びTはAl,Si,C,Pから選ばれた少なくとも1種]で表わされる組成を備えた軟磁性金属ガラス粉末に対し、質量比で10%以下のバインダを混合した混合物の成形体からなる。インダクタンス部品は、高周波用磁心に対して巻線を少なくとも巻回数で1ターン以上巻回して成る。  (もっと読む)

(もっと読む)

積層型巻線構造を有するトランスフォーマー

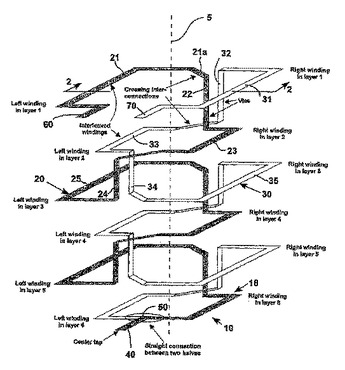

本発明は、積層型巻線構造を有するトランスフォーマーに関するものである。

本発明は、交流電力を供給されて電子誘導作用により他の回路に電力を供給するトランスフォーマーであって、中空部を有するコア部と、前記コア部に相互電気的に絶縁された1次巻線及び2次巻線が巻かれ、かつ前記1次巻線及び前記2次巻線は、各々金属板が間隙をなしながら積層され、一側端が結合された積層金属板であり、前記1次巻線及び前記2次巻線の他側端が互いに挿入されて結合し、かつ前記1次巻線の金属板が前記2次巻線の前記間隙の間に交互に挿入される形態で結合されることを特徴とする積層型巻線構造を有するトランスフォーマーを提供する。

本発明によると、高周波大容量のトランスフォーマーから発生する導通損失を格段に減らして変圧効率を向上させることができ、巻線から発生する熱の発熱量を格段に減らし、熱の放出までも効果的に遂行できることになる。

(もっと読む)

表面実装部品

【課題】実装基板上に溶融半田を印刷後、実装部品の実装端子を位置決めし、実装端子を加圧して実装しても、実装端子の真下の溶融半田を十分確保でき、振動や衝撃等が加わっても実装部品が回路基板から脱落する虞のない信頼性の高い表面実装部品を提供することにある。

【解決手段】コイルが巻装されたコアを内蔵したトランス本体11と、このトランス本体11から外部に導出されコイルと電気的に接続される実装端子12とからなり、この実装端子12を回路基板13のランド14にリフロー半田付けして実装される表面実装される表面実装部品において、実装端子12の回路基板13のランド14に対面する接続端子片15を山折りし、接続端子片15の下面に半田を滞留させる半田滞留部16を設けたことを特徴とする。

(もっと読む)

トランス

【課題】コイルとなる線材が太い場合でも基板に対するコイル端末の接続が容易になると共に、基板に対するトランスの傾斜のおそれがなく、比較的安価に製造できるトランスを提供する。

【解決手段】プラスチック成形体5Aに、ピン端子4を貫挿する貫通孔10と、コイル端末を貫挿する貫通孔11とを設ける。プラスチック成形体5Aにピン端子4を貫挿してプラスチック成形体5Aをボビン2に装着する。コイル端末2aを貫通孔7に貫挿して位置出しする。そして基板9に設けた端子孔10にボビン1に設けたピン端子4を挿入すると共に、コイル端末2aを挿通孔11に挿通する。

(もっと読む)

電子部品

【課題】 内部応力を緩和して、クラックの発生や磁気特性の劣化を防ぐことが可能な電子部品を提供すること。

【解決手段】 積層型インダクタ1は、素体10と、素体10の内部に設けられたコイルLとを備えている。素体10は、焼結した第1の部分16と、焼結していない粉体からなる第2の部分18とを有している。コイルLは、第2の部分18の内部に位置するように形成されており、第2の部分18によって覆われている。

(もっと読む)

3dBカプラ

【課題】トランスの1次側と2次側との良好な容量結合および誘導結合を、小さいサイズで実現できる3dBカプラを提供する。

【解決手段】トランスの一次側である第1の導体およびトランスの二次側である第2の導体が、相互に隔離され、容量的および誘導的に相互に結合されており、それぞれn>1の巻数を有する3dBカプラとし、所定の特性インピーダンスおよび所定の基本周波数に対して、結合容量のキャパシタンスと誘導結合を形成するインダクタンスを共に所定値に調整する。

(もっと読む)

プリンテッド・スパイラル・インダクタ

【課題】

インダクタはスペースをとり、磁性体をコアとすることが多く、非線形性が強く出ることが多い。変圧器は重く大きい。インダクタの設計には経験や、高価なシミュレーターが必要であり、小さいインダクタンスの測定には非常に高価な測定器を必要とする。FM信号の受信や、アナログ演算処理には、一般的にIC化を含む複雑な回路を必要とし、別電源も必要である。

【課題を解決するための手段】

基板上に円形のスパイラルインダクタを生成することにより、省スペースで線形動作をさせやすいインダクタを生成する。本発明によるプログラムを用い、巻数を増やす上で発生する諸問題を考慮し、インダクタンスの計算を安価で容易に高速に行う。製造したインダクタの値を、自励発振させて安価に精度良く計測を行う。該インダクタを多重に重ね、薄く軽量な変圧器、電源や複雑な回路を必要としないFM受信器、アナログ信号の加算、減算器を生成する。

(もっと読む)

位相補償回路付き環状鉄心変流器

【課題】環状鉄心を貫通する1次導体と、環状鉄心周りに巻かれる2次巻線とを含む環状鉄心変流器において補償回路の位相誤差を低減する。

【解決手段】測定分流器(RSh)または負荷(Zh)が、2次端部に設置される。1次電流(IP)と2次電流(IS)との間の位相誤差(f)を補償するために、能力(C)が実質的に方程式(I)または(II)に従って測定される補償回路(K)が2次端部に設置される。方程式(I)または(II)においては、Cは補償回路の能力を表し、ωは角振動数を表し、ψは1次電流と2次電流との間の位相誤差を表し、RShは任意の測定分流器の抵抗を表し、Zbは任意の負荷のインピーダンスを表す。

(もっと読む)

エネルギー貯蔵コイル

【課題】EMIの発生を抑制するエネルギー貯蔵コイルの提供。

【解決手段】エネルギー貯蔵コイル(30)は、周囲に複数ターン(32)の導体が巻かれたコア(31)を具備し、コア(31)に沿って延びる少なくとも2つの区域を形成するこれらのターンは、それぞれ、複数ターン(32)が互いに重なる第1端及び第2端を有する主区域(37)、及び主区域(37)の第1端に隣接する少なくとも1つの補助区域であり、補助区域ターンがターンからターンまで主区域(37)よりも低い寄生キャパシタを有する補助区域(38,39)を提供する。

(もっと読む)

複合積層型電子部品

【課題】 バリスタ素子部とインダクタ素子部とを、クラックの発生等が生じることなく確実に接合・一体化させることができ、部品のコンパクト化が図れる複合積層型電子部品を提供する。

【解決手段】 バリスタ層と内部電極を有するバリスタ素子部(10)と、フェライト層と内部導体を有するインダクタ素子部(20)と、これらの双方の素子部を接合するために介在される接合中間層(50)とを有し、フェライト層は、Ni−Zn系の磁性フェライトであり、バリスタ層は、その主成分がZnOからなり、接合中間層は、組成の異なる第1番目から第N番目までのN層(Nは2以上の整数)の接合膜を積層することにより構成されており、その接合中間層の中でインダクタ素子部のフェライト層に接する第1番目の接合膜はZn系フェライトから構成される。

(もっと読む)

複合積層型電子部品

【課題】 バリスタ素子部と、インダクタ素子部とをクラックの発生等が生じることなく確実に接合・一体化させることができ、しかも、接合のための接合中間層の厚さを極力薄く設定することができ、部品のコンパクト化が図れる複合積層型電子部品を提供する。

【解決手段】 バリスタ素子部(10)と、インダクタ素子部(20)と、これらの双方の素子部を接合するために介在される接合中間層(50)とを有し、その接合中間層(50)は、組成の異なる第1番目から第N番目までのN層(Nは2以上の整数)の接合膜を積層することにより構成されるとともに、それらの総和厚さが240μm以下であり、インダクタ素子部と、これに接する第1番目の接合膜との相互の線膨張率の差が1(ppm/K)以内であり、それ以外のN−1箇所の接合界面を構成する隣接する接合膜同士の相互の線膨張率の差が2(ppm/K)以内であり、バリスタ素子部と、これに接する第N番目の接合膜との相互の線膨張率の差が2(ppm/K)以内に構成される。

(もっと読む)

インダクタ

【課題】 インダクタンス値を限りなく低くした、また、ノーマルモード特性にて、ノイズを与えない磁気結合の優れた高効率なインダクタンス構造とした、薄いフレキシブルなフリップチップタイプの薄膜磁性体を用いたインダクタを得る。

【解決手段】 薄い薄膜磁性体からなる第1の磁性層上層10,12と、相対する1対の導体コイルと、絶縁層からなるコイル構造であって、磁性体は、数μmから数10μmの樹脂基板の両面上に、第1の磁性層上層10,12を成膜して構成した複合磁性体を、相対して接着した導体コイルの両側に配置し、前記導体コイルは、樹脂基板の片側に渦巻き状に形成され、内端が前記樹脂基板の厚み方向に貫通するスルーホール媒体を介して前記樹脂基板の他面側に導かれており、極薄でフレキシブルなフリップチップタイプのコモンモードチョーク構成である薄膜磁性体を用いたインダクタとする。

(もっと読む)

インダクタンス素子

【課題】 巻線長を短くして銅損を減少させると共に、引出し部分から発生する磁界を低減するインダクタンス素子を得る。

【解決手段】 磁芯14の下部に配置された巻枠12に、磁芯14の長手方向に沿って5つの端子16がそれぞれ植設される。磁芯14に4つのコイル20がそれぞれ巻かれ、4つのコイル20が並列に配置される。各コイル20は1本の巻線材18で繋がった形で形成され、各コイル20の巻線材18が端子16に一旦絡げられて半田付けされてから隣のコイル20に延びる構造になっている。隣り合ったコイル20同士は相互に逆巻きで巻かれ、それぞれのコイル20は3ターン巻かれた構造になっている。

(もっと読む)

表面実装部品およびその製造方法

【課題】 リード端子の突き出し方向について、はんだ接合部の強度を向上できてクラックの発生を防止でき、はんだ付けの確実化が手間なく容易に行える表面実装部品およびその製造方法を提供すること

【解決手段】 成形体1は線材とコア材を組み付けるボビンであり、樹脂材料から薄い帯板形状に形成し、短辺両端からリード端子2…が突き出す状態に一体に封止する。各リード端子はクランク形状に折り曲げ加工し、先端の接合面を基板のランドパターンに接面させてはんだ付けする構成である。リード端子には先端に当該突き出し方向と交差して張り出す凸部3を設け、凸部は先端の側部一方あるいは両方に設ける。製造には、リード端子は複数が所定に配列する形態でリードフレームに形成し、そのリードフレームの定位置に成形体を形成して、アウターリードを切断,フォーミングして各単体に分離する。

(もっと読む)

181 - 200 / 227

[ Back to top ]