Fターム[5E082FG42]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 気体・固体誘電体 (7,068) | 気体・固体誘電体の製造・形成手段 (1,162) | 蒸着、スパッタリング (233)

Fターム[5E082FG42]に分類される特許

161 - 180 / 233

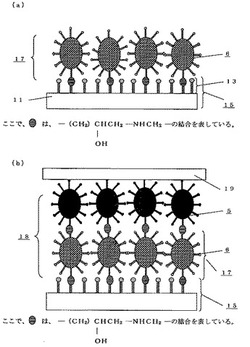

絶縁体微粒子膜とその製造方法及びそれを用いたコンデンサー

【課題】

スパッタ法やCVD法では、特殊な真空チャンバーが必要であり、製造コストが高くなるという欠点があり、ゾルゲル法では、反応に高温を必要とするため、基材が耐熱性のものに限定されていた。さらに、大面積の被膜を作成する場合、膜厚にばらつきがあった。

【解決手段】

導電性基材表面に絶縁層として1層形成された絶縁体微粒子膜が導電性基材表面に形成された第1の有機膜と絶縁体微粒子表面に形成された第2の有機膜を介して共有結合している単層絶縁体微粒子膜を製造提供することを要旨とする。さらに同様の方法を用いて、単層誘電体微粒子層が第1及び第2の電極に挟まれた構造のコンデンサーであり、第1の電極と誘電体微粒子が第1の電極表面に形成された第1の有機膜と誘電体微粒子表面に形成された第2の有機膜を介して共有結合しているコンデンサーを提供する。

(もっと読む)

薄膜キャパシタが内蔵された印刷回路基板及びその製造方法

【課題】低温で所望の誘電特性を有する非晶質常誘電体薄膜を形成すると共に製品の信頼性を高めることの出来る薄膜キャパシタが内蔵された印刷回路基板及びその製造方法を提供する。

【解決手段】絶縁基材31a上に順次下部電極33と、上記下部電極上に形成された非晶質常誘電体膜35と、上記常誘電体膜上に形成された金属シード層37と、上記金属シード層上に形成されたその表面粗度Raが300nm以上である上部電極39と、を形成して薄膜キャパシタが内蔵された印刷回路基板30とする。この場合、上記下部電極33は無電解メッキで形成された部分33aと電解メッキで形成された部分33bとを含む。

(もっと読む)

薄膜キャパシタを内蔵した印刷回路基板の製造方法及びそれにより製造された印刷回路基板

【課題】薄膜キャパシタを内蔵した印刷回路基板の製造方法及びそれにより製造された印刷回路基板を提供する。

【解決手段】絶縁基材21a上に、無電解メッキで形成された部分23aと電解メッキで形成された部分23bを含む下部電極23を形成する工程と、上記下部電極上に低温成膜工程によって非晶質常誘電体膜25を形成する工程と、上記常誘電体膜上に無電解メッキ工程によって金属シード層27を形成する工程と、上記金属シード層上に電解メッキ工程を利用して上部電極29を形成する工程とを含み(上部電極29上に絶縁基板21bを設けてもよい)、薄膜キャパシタを内蔵した印刷回路基板の製造方法及びこの製造方法で製造された薄膜キャパシタを内蔵した印刷回路基板20である。

(もっと読む)

コンデンサの製造方法

【課題】本発明は、誘電体層と金属薄膜層とを蒸着によって積層形成したコンデンサの大容量化と長寿命化を目的とする。

【解決手段】コンデンサ素子母体3を蒸着によって形成する第1の工程と、前記コンデンサ素子母体3をプレスした後条の形態に切断し、更にメタリコン電極8を形成しコンデンサ素子条とする第2の工程と、引き出し電極端子9を取り付けてコンデンサ素子10を形成する第3の工程と、開口部を有する樹脂ケース12に前記コンデンサ素子10を収容した後、充填樹脂13によって隙間を充填する第4の工程とからなるコンデンサの製造方法。

(もっと読む)

薄膜デバイスおよびその製造方法

【課題】キャパシタを備えた薄膜デバイスにおいて、キャパシタの耐電圧の低下や製品間におけるキャパシタの耐電圧のばらつきの増大を抑制する。

【解決手段】薄膜デバイス1は、基板2と、この基板2の上に設けられたキャパシタ3とを備えている。キャパシタ3は、基板2の上に配置された下部導体層10と、この下部導体層10の上に配置された誘電体膜20と、この誘電体膜20の上に配置された上部導体層30とを有している。誘電体膜20の厚みは、0.02〜1μmの範囲内であり、且つ下部導体層10の厚みよりも小さい。下部導体層10の上面の最大高さ粗さは、誘電体膜20の厚み以下である。

(もっと読む)

薄膜キャパシタが内蔵された印刷回路基板及びその製造方法

【課題】電極の厚さを厚くすることができ、上部電極の表面粗度を増加させることができる薄膜キャパシタが内蔵された印刷回路基板及びその製造方法を提供する。

【解決手段】絶縁基材31a上に第1下部電極33a及び第2下部電極33bからなる下部電極33を形成し、上記下部電極33上に低温成膜工程により非晶質常誘電体膜35を形成し、上記非晶質常誘電体膜35上に緩衝層36を形成し、上記緩衝層36上に金属シード層37を形成し、上記金属シード層37上に上部電極39を形成して薄膜キャパシタが内蔵された印刷回路基板30を製造する。

(もっと読む)

電気デバイス

【課題】水を消費する機能かつ蓄電機能を有する、防水性に優れた保護層を備えた電気デバイスを提供する。

【解決手段】電気デバイスにおける電気化学素子の少なくとも一部を覆う保護層は、第1の絶縁層と、第1の絶縁層上に形成された、弁金属を含む陽極層と、陽極層上に形成された酸化皮膜層と、酸化皮膜層上に形成された固体電解質層と、固体電解質層上に形成された陰極層と、陰極層上に形成された第2の絶縁層と、陽極層と電気的に接続された第1の電圧印加端子と、陰極層と電気的に接続された第2の電圧印加端子と、を備える。

(もっと読む)

薄膜キャパシタの製造方法、それにより製造される薄膜キャパシタおよびこれを有する薄膜キャパシタ内蔵型印刷回路基板

【課題】下部電極の酸化を防止し、さらに下部電極と誘電体層の界面で欠陥を防止してBDV特性を確保できる薄膜キャパシタの製造方法と該薄膜キャパシタが内蔵された印刷回路基板を提供すること。

【解決手段】薄膜キャパシタの製造方法は、金属ホイールを再結晶熱処理する段階と、上記再結晶熱処理した金属ホイールの上部に誘電体層を形成する段階と、上記金属ホイールと誘電体層を熱処理する段階と、上記熱処理した誘電体層の上部に上部電極を形成する段階と、を含んで成る。本発明において金属ホイールの再結晶は、低温から短時間で行われるため金属ホイールの酸化が防止されながら再結晶される。従って、誘電体層の高温熱処理が可能となり、これによって薄膜キャパシタの電気的特性及び製品の信頼性を改善できる。

(もっと読む)

誘電体磁器組成物及びそれを用いて作製される電子部品並びに積層セラミックコンデンサの製造方法

【課題】マイクロ波領域で使用するのに好適な電気的特性を有するとともに、低温焼成可能で、環境に悪影響を及ぼすことのない高周波用誘電体磁器組成物を提供する。

【解決手段】BaTi4O9、ZnO、SiO2、SiO2、B2O3を含有する誘電体磁器組成物であって、ZnO、SiO2及びBaOの、ZnOと、SiO2と、SiO2との合計質量に対する質量割合が,ZnO、SiO2及びBaOの三元図において、それぞれ50%:30%:20%(点A)、30%:50%:20%(点B)、20%:30%:50%(点C)、45%:20%:35%(点D)の点A−B−C−D−Aの順に結ぶ直線によって囲まれる四辺形領域内にあり、BaTi4O9100質量部に対し、ZnO、SiO2及びBaOの合計で15〜25質量部、B2O3を1〜5質量部含有する誘電体磁器組成物。

(もっと読む)

強誘電体薄膜

【課題】 Si単結晶基板上に強誘電体薄膜を形成するに際し、膜内の応力を制御して自発分極値の低下を防ぐことを目的とする。

【解決手段】 Si単結晶基板上に形成された強誘電体材料からなるエピタキシャル強誘電体薄膜であり、この強誘電体薄膜の結晶面のうち、前記Si単結晶基板表面の結晶面に平行な結晶面をZF面とし、ZF面間の距離をzFとし、強誘電体薄膜構成材料のバルク状態でのZF面間の距離をzF0としたとき、0.980≦zF/zF0≦1.010であり、前記強誘電体材料が、ペロブスカイト型結晶構造を有する、化学式ABO3(AはCa、Ba、Sr、K、Na、Li、LaおよびCdから選ばれた1種以上であり、BはTi、Zr、TaおよびNbから選ばれた1種以上である)で表される化合物又は希土類元素含有チタン酸鉛であり、厚さが2〜100nmである強誘電体薄膜。

(もっと読む)

強誘電性薄膜素子用の不動態化構造

【課題】 強誘電性薄膜素子の電極間の強誘電層の界面に沿って形成される漏洩通路を減少させ、制御する。

【解決手段】 開示されている強誘電性薄膜素子は、2つの電極の間における、該強誘電性薄膜素子と不動態層との間の界面に沿う漏洩通路を減少させまたは制御する不動態化構造を含む。また、このような素子を作製するための方法が開示されている。前記不動態化構造は開口を有する第1の不動態層を含み、該開口は、前記強誘電性薄膜層の一部分を露出させ、第2の不動態層が該開口を介して前記含み、該通路が前記強誘電性薄膜層に接することを可能にする。一実施の形態において、前記開口は、コンデンサの活性領域を包囲している矩形リングである。他の実施の形態において、第2の不動態層が第2の電極にも接し、該第2の電極の一部分も前記開口を介して露出する。他の実施の形態において、集積抵抗における前記薄膜層と不動態層との間の界面に沿って電流が流れる。

(もっと読む)

樹脂仕切板および樹脂仕切板を用いたフィルムコンデンサの製造方法

【課題】本発明は、複数のコンデンサ素子の両端面にメタリコン電極を形成する際に、コンデンサ素子の両端面にバリのない良好な形状のメタリコン電極を形成できる樹脂仕切板とその樹脂仕切板を用いたフィルムコンデンサの製造方法の提供を目的とする。

【解決手段】誘電体フィルムの片面または両面に金属蒸着電極を形成した金属化フィルムを一対の前記金属蒸着電極が前記誘電体フィルムを介して対向するように積層または巻回したコンデンサ素子1の両端面1aに溶融金属を溶射してメタリコン電極を形成する際に複数のコンデンサ素子1のそれぞれを仕切る平板状の樹脂板であって、対向する2辺に逆テーパ状の凸部2aを有する樹脂仕切板2を用いる。

(もっと読む)

薄膜コンデンサとその製造方法、配線基板

【課題】保護層の内部に残留応力を適正範囲内にするとともに直下の層との密着性を確保させた長期信頼性を確保する薄膜コンデンサとその製造方法を提供するとともに、この薄膜コンデンサを用いた高信頼性の配線基板を提供する。

【解決手段】支持基板1上に、下部電極層2、誘電体層3、上部電極層4が順次形成されて、静電容量領域が形成されて薄膜コンデンサをなしている。そして、下部電極層2と電気的接続された外部端子5a、上部電極層4と電気的接続された外部端子5bが形成され、これらの外部端子5a、5bがそれぞれ内部に露出するように、開口部6a、6bを設けた保護層7が静電容量領域を被覆するように形成されている。この保護層7は、シリカを主成分とするとともに、圧縮残留応力を100MPa以上210MPa以下の範囲となるようにした。

(もっと読む)

誘電体膜キャパシタおよびその製造方法

【課題】誘電体膜キャパシタにおいて、下部電極とその下層との密着性が良く、酸化されにくく熱的に安定な電極構造を提供する。

【解決手段】誘電体膜キャパシタ20は、開口部22aを有し、白金を含む材料からなる下部電極22と、下部電極22の上方に設けられた、ABOx型ペロブスカイト構造を有する酸化物を含む誘電体膜24と、誘電体膜24の上方に設けられた上部電極26と、を含む。誘電体膜24の形成領域の面積に対する、下部電極22の平面面積の割合が50%以上である。

(もっと読む)

半導体バリア結晶粒界コンデンサーの構造と製造方法

【課題】 汚染問題を解決できる半導体バリア結晶粒界コンデンサーの構造と製造方法を提供する。

【解決手段】 半導体材料層401A、合成水晶半導体402A、第1良導体406A、第2良導体405A及び絶縁層404Aを含む。半導体材料層401Aの局部は外部に第1種雑質が混合されて、第1種の半導体材料区域403Aを形成する。第1良導体406Aと第1種雑質の半導体材料区域403Aとを接続させ、合成半導体402Aは第1種雑質を混入した半導体材料区域403Aにスパッター加工する。合成半導体402Aの内部にも第1種雑質及び第2種雑質が混入され、合成水晶半導体402A上の局部に第2良導体405Aをスパッター加工する。第1良導体406Aと第2良導体405Aの間は、合成水晶半導体402で仕切っておく。

(もっと読む)

薄膜電子部品の製造方法

【課題】 薄膜電子部品の性能の低下を防ぐことの可能な薄膜電子部品の製造方法を提供する。

【解決手段】 本発明に係る薄膜電子部品の製造方法は、基材10上に誘電体層16を設ける工程と、誘電体層の少なくとも一部を覆い、第1の開口50を有する第1の導電層31を設ける工程と、基材を貫通して第1の開口に連通する第1の貫通孔52を形成する工程とを備えている。基材上に第2の導電層32を設け、この第2の導電層の少なくとも一部を覆うように誘電体層16を設けてもよい。第2の導電層は、第2の開口51を有していてもよい。基材を貫通して第2の開口に連通する第2の貫通孔53を形成してもよい。

(もっと読む)

抵抗体薄膜積層フィルム

【課題】抵抗体素子やコンデンサ部品、部品内蔵プリント配線板に有用な、安定した高品質の抵抗体薄膜が形成された薄膜抵抗体素子用の抵抗体薄膜積層フィルムの提供。

【解決手段】基板の一面上に抵抗体薄膜層が形成され、該抵抗体薄膜層上に電極層が形成されてなる抵抗体薄膜積層フィルムにおいて、該基板がベンゾオキサゾール骨格を有するジアミン類と芳香族テトラカルボン酸類を出発材料とする線膨張係数が1〜12(ppm/℃)のポリイミドベンゾオキサゾールフィルムである抵抗体薄膜積層フィルム。

(もっと読む)

内蔵型薄膜キャパシター、積層構造物及びそれらの製造方法

【課題】低温の成膜工程で充分な誘電率を有する誘電体膜を得て、これを備える薄膜キャパシター等を提供する。

【解決手段】第1及び第2金属電極膜とその間にBiZnNb系非晶質金属酸化物を用いて、誘電率が15以上の誘電体膜を含む薄膜キャパシターを形成する。ポリマー基盤複合体基材上に、順次、第1金属電極膜と、BiZnNb系非晶質金属酸化物を用いて成る、誘電率が15以上の誘電体膜と、第2金属電極膜を形成して積層構造物とする。誘電体膜として採用されるBiZnNb系非晶質金属酸化物は結晶化のための高温の熱処理工程がなくても、高い誘電率を示すため、印刷回路基板のようなポリマー基盤の積層構造物の薄膜キャパシターに有益に使用できる。

(もっと読む)

半導体基板上に形成される高精度高周波数キャパシタ

【課題】高周波数用高精度キャパシタを提供すること。

【解決手段】高精度高周波数キャパシタは半導体基板102の表側に形成された誘電層104を有し、第一の電極106が誘電層上に形成される。半導体基板は高度にドープされ、それゆえ抵抗率が低い。第二の電極108は第一の電極106より絶縁され、また表側表面上に形成される。一つの実施例では、第二の電極108は金属を満たしたビア116によって裏面の導電層120と電気的に接続される。他の実施例ではビアは省略され、第二の電極は基板と電気的に接続されているか、誘電層上に形成されるかのどちらかであり、一対の連続して接続されたキャパシタを作り出す。

(もっと読む)

多層薄膜キャパシタとその製造方法及び装置

本発明は、複数個のスリットを有するシャドーマスクを備えた一つのマスクセットを用い、シャドーマスクと蒸着ソースとの間の蒸着角の設定により真空蒸着を行う。一旦作り出された真空状態にて、下部端子層、誘電層、内部電極層、及び上部端子層からなる多層薄膜キャパシタを一気に形成する。または、複数個のスリットを有するシャドーマスクをそれぞれ備え、互いに向き合うように設けられた上部及び下部マスクセットの相対的な移動により、スリットパターンを調節し、一旦作り出された真空状態にて、下部端子層、誘電層、内部電極層、及び上部端子層からなる多層薄膜キャパシタを一気に形成する。  (もっと読む)

(もっと読む)

161 - 180 / 233

[ Back to top ]