Fターム[5E082FG46]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 気体・固体誘電体 (7,068) | 気体・固体誘電体の製造・形成手段 (1,162) | 塗布、印刷 (820)

Fターム[5E082FG46]に分類される特許

21 - 40 / 820

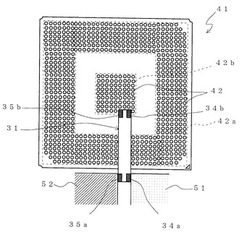

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

積層セラミック電子部品

【課題】耐電圧特性に優れた高圧用積層セラミック電子部品を提供する。

【解決手段】本発明によると、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向配置される内部電極層とを含み、上記誘電体層の平均厚さをtdと規定すると、td≧15μmで、上記誘電体層内の10μm当たりの誘電体粒数が15個以上である積層セラミック電子部品を提供する。

本発明によると、微粉の誘電体パウダーで均一な厚膜の誘電体層が得られ、耐電圧特性に優れた高圧用積層セラミック電子部品を具現することができる。

(もっと読む)

積層型電子部品の製造方法

【課題】特性のばらつきが少なく、小型で高容量の電子部品を、低コストで製造することが可能な積層型電子部品の製造方法を提供すること。

【解決手段】グリーンシートに所定パターンで電極ペースト膜を形成する工程と、グリーンシートを積層して積層体4aを準備する工程と、積層体を、支持基板36の粘着層34に付着する工程と、積層方向と直交する第1方向に沿って、支持基板は切断せずに積層体を切断して端子電極接続面15a,15bを形成し、積層方向および第1方向と直交する第2方向に沿って、積層体および支持基板を切断してギャップ面16を形成し、支持基板と一体化された棒状体38を得る工程と、ギャップ面が同一平面に配置されるように複数の棒状体38を並べ、ギャップ面16に、セラミックペースト42を塗布する工程と、粘着層の粘着力を弱め、積層体2aと支持基板36とを分離する工程とを有することを特徴とする。

(もっと読む)

コンデンサおよびその製造方法

【課題】 メッキ液の浸入を防ぎ、信頼性の高いコンデンサを提供すること。

【解決手段】 複数の積層された誘電体層5、および該誘電体層5間の界面に沿って形成された複数の内部電極3を含み、該内部電極3の各端部が所定の端面に露出している積層体2と、所定の前記端面2e、2fに露出した前記内部電極3を互いに接続するように、所定の前記端面2e、2fに設けられた外部電極4とを備え、前記内部電極3と前記誘電体層5との間に、所定の前記端面2e、2fに開口する隙間6が設けられており、該隙間6にガラス7が設けられているコンデンサ1である。

(もっと読む)

積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】高さ方向に沿って2枚以上の外層ダミー導体7を所定間隔で連続的に配置することにより、複数の外層ダミー群31を形成する。外層ダミー群31内における外層ダミー導体7同士の間隔をd、外層ダミー群31同士の間隔をg、としたとき、gがdより大きくなるようにする。これによって、めっき析出ポイントを確保しつつ、外層ダミー群31同士の間隔を遠ざけることにより、外層ダミー導体7による内部電極3,4の押圧を緩和することができ、局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

コンデンサモジュール

【課題】セラミックコンデンサを利用することで、ACラインのノイズ吸収フィルタ等を構成する複数のコンデンサと抵抗との異なる種類の電子部品を一体化することができ、耐熱性が良好で、サイズの小型化、コストの低廉化、実装スペースの省スペース化を実現することができるコンデンサモジュールを提供する。

【解決手段】セラミック基板12内に形成され、一端が第1入出力端子14aに接続された2つの第1Xコンデンサ電極16aと、セラミック基板12内に形成され、一端が第2入出力端子14bに接続され、且つ、それぞれ第1Xコンデンサ電極16aに対向する2つの第2Xコンデンサ電極16bと、セラミック基板12の上面12uに形成され、第1入出力端子14aと第2入出力端子14b間に接続された1つの抵抗体18とを有する。

(もっと読む)

内部電極用導電性ペースト組成物及びそれを含む積層セラミック電子部品

【課題】内部電極層用導電性ペースト組成物及びそれを含む積層セラミックコンデンサを提供する。

【解決手段】本発明による内部電極層用導電性ペースト組成物は金属粉末100モルと、セラミック粉末0.5〜4.0モルと、シリカ(SiO2)粉末0.03〜0.1モルと、を含むことができる。本発明の一実施形態による内部電極用導電性ペースト組成物は、内部電極の焼成収縮温度を高め、内部電極の連結性を向上させることができる。また、誘電体層の緻密度を向上させ、耐電圧特性、信頼性及び誘電特性を向上させることができる。

(もっと読む)

積層セラミックコンデンサ

【課題】耐湿性の良好な積層セラミックコンデンサを提供する。

【解決手段】内部電極21が形成された複数の第1のセラミック層22を積層してなる有効層20と、前記有効層20を挟むように内部電極が形成されていない複数の第2のセラミック層31を積層してなる一対の保護層30とを有する積層体10と、該積層体10の外面に形成され前記内部電極21と電気的に接続した外部電極40とを備えた積層セラミックコンデンサにおいて、前記第1のセラミック層21及び第2のセラミック層31はそれぞれSiO2が添加されたセラミック材料からなり、且つ、前記保護層は相対的に互いにSiO2濃度が異なる複数の第2のセラミック層31H,31Lを積層してなる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、電極連結性を制御して容量を確保することができる積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、セラミック本体10と、この前記セラミック本体10の内部に形成され、中央部70及び前記この中央部70から縁に向かって薄くなるテーパ部50を有する内部電極30、31と、を含む。前記内部電極30、31の面積に対する前記テーパ部50の面積の比率は、35%以下であることを特徴とする。本発明によると、小型及び高容量の積層型セラミックキャパシタにおいても、電極連結性を制御することにより所望の容量を確保することができる。

(もっと読む)

積層セラミックコンデンサ

【課題】 外部電極における下地電極の厚みが薄い場合でも、湿中負荷試験における不良を少なくできる積層セラミックコンデンサを提供する。

【解決手段】 誘電体層5と内部電極層7とが交互に積層されたコンデンサ本体1と、該コンデンサ本体1の前記内部電極層7が露出した端面1aおよび該端面1aに隣接する側面1bに設けられた下地電極3および該下地電極3上に設けられた被覆電極とを含む外部電極とを具備する積層セラミックコンデンサにおいて、前記下地電極3は、銅を主成分とし、かつ亜鉛を含み、緻密度が96%以上であり、前記下地電極3の前記コンデンサ本体1の前記端面1a側における厚みが20μm以下である。

(もっと読む)

チップ型積層キャパシタ

【課題】本発明は、小型化及び高容量化を具現するとともに、音響ノイズを低減するチップ型積層キャパシタに関する。

【解決手段】本発明の一実施例によるチップ型積層キャパシタは、グレインの平均サイズの10倍以上であり、3μm以下の厚さに形成される誘電体層が積層されて形成されるセラミック本体と、上記セラミック本体の長さ方向の両端部に形成され、相違する極性を有する第1及び第2外部電極と、一端は上記第2外部電極が形成される上記セラミック本体の一端部面と第1マージンを形成し、他端は第1外部電極に引き出される第1内部電極と、一端は上記第1外部電極が形成される上記セラミック本体の他端部面と第2マージンを形成し、他端は第2外部電極に引き出される第2内部電極と、を含み、上記第1マージンと第2マージンとは、200μm以下の条件で相違する幅を有することができる。

(もっと読む)

高誘電絶縁放熱シートおよびその製造方法

【課題】高い放熱性と誘電率とを有する高誘電絶縁シートを提供する。

【解決手段】溶媒可溶性ポリマーと、前記溶媒可溶性ポリマー中に分散する、高誘電率微粒子および熱伝導性微粒子とを含む高誘電絶縁放熱シートであって前記熱伝導性微粒子が、非球状であり、前記熱伝導性微粒子の長径方向と、前記高誘電絶縁放熱シートの厚さ方向との間の角度が、平均して、60°以下である高誘電絶縁放熱シートとする。

(もっと読む)

電子部品の製造方法

【課題】表層電極において接続信頼性の高い突起状導体を形成することができる電子部品の製造方法を提供すること。

【解決手段】セラミックコンデンサのカバー層部108は、各ビア導体131の周囲となる位置のセラミック絶縁層150間に複数の段差補正用絶縁層151を介在させた状態で形成される。フォトレジストフィルム180の露光時には、突起状導体を形成するための形成予定領域R1の外側領域R2を感光させるべく入射したレーザ202が、表層電極111に当たって向きを変え形成予定領域R1の反対側である外側領域R2に反射するように露光を行う。フォトレジストフィルム180を現像して、開口部を有するめっきレジストを形成し、開口部を介して露出する表層電極111に対してめっきを施すことにより突起状導体を形成する。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、信頼性に優れた積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明による積層セラミック電子部品は、内部電極及び誘電体層を含み、上記内部電極の一部が露出する接続面を一つ以上有する本体部と、上記接続面に結合して上記内部電極と電気的に連結される外部電極と、上記接続面において露出する内部電極の少なくとも一部を遮蔽するように上記接続面に用意される保護層と、を含み、上記内部電極全体の幅に対して上記保護層によって遮蔽される内部電極の露出した幅の比率は、0.8から0.9倍を有する。本発明によると、内部電極が外部に露出する本体部の表面における外部電極との距離が相対的に近い領域に内部電極を遮蔽することができる保護層を用意することで、異物浸透による絶縁抵抗の劣化、信頼性の低下及び接触性の不良を防止することができる。

(もっと読む)

積層コンデンサ及び積層コンデンサの製造方法

【課題】焼付層の応力によるクラックの発生と、めっき液の浸入による絶縁不良の発生とを防止できる積層コンデンサ及び積層コンデンサの製造方法を提供する。

【解決手段】積層コンデンサ1では、内部電極6A,6Bから積層体2の端面に引き出される引出導体12A,12Bの全部を覆うように焼付層17A,17Bが形成されている。これにより、めっき層18A,18Bの形成の際にめっき液が内部電極6A,6B側に浸入することが防止され、絶縁不良の発生を防止できる。また、焼付層17A,17Bがダミー電極13C,13F,13G,13Hの一部を覆っているので、焼付層17A,17Bの面積を抑えることができる。したがって、焼付層17A,17Bに過剰な応力が生じることを抑制でき、焼付層17A,17Bの応力によるクラックの発生を防止できる。

(もっと読む)

積層セラミック電子部品およびその製造方法

【課題】積層セラミック電子部品の製造方法において、プリント配線板の導体接続部との接合の信頼性を確保し、多積層化できるようにする。

【解決手段】積層セラミック電子部品の製造方法は、セラミックグリーンシートを形成する工程と、その上に内部電極層2a,2bとなる金属ペーストを印刷する工程と、これらを複数枚重ねて、積層圧着し積層体を形成する工程と、前記積層体の主面に延在部用の導電性ペーストを印刷し、乾燥させて延在部9a,9bを形成する工程と、積層体を切断し、個片に分離して積層セラミック素体3を形成する工程と、その端面6a,6bに廻り込み部用の導電性ペーストを塗布することにより廻り込み部10a,10bを形成する工程とを含む。前記積層体を形成する工程において、前記積層体の引出部5a,5bの主面7が機能部4の主面7より低くなるように積層体を圧着する。

(もっと読む)

電子部品及び電子部品の製造方法

【課題】電子部品の高密度実装を可能とする電子部品及び電子部品の製造方法を低コストで提供すること。

【解決手段】電子部品1は、素体2、外部電極3,4、及び絶縁層20,21を備えている。素体2は、互いに対向する一対の端面2a,2bと、一対の端面2a,2bを連結するように伸び且つ互いに対向する一対の主面2c,2dと、一対の主面2c,2dを連結するように伸び且つ互いに対向する一対の側面2e,2fと、を有している。外部電極3,4は、素体2の端面2a,2b側に形成され、端面2a,2bに隣接する主面2c,2d及び側面2e,2fの一部を覆う。少なくとも外部電極3,4における側面2e,2f側に位置する電極部分3e,3f,4e,4fの表面が、絶縁層20,21で覆われている。

(もっと読む)

積層コンデンサ

【課題】外部電極と端子導体との間のショート不良を防止できる積層コンデンサを提供する。

【解決手段】積層コンデンサ1では、ESR制御部の内部電極に接続される外部電極3A,3Bがめっき層のみで構成されている。したがって、全ての外部電極3A,3B及び端子導体4A,4Bを焼付層で構成する場合と比べて外部電極3A,3Bと端子導体4A,4Bとの間のショート不良を防止できる。また、この積層コンデンサ1では、静電容量部の内部電極に接続される端子導体4A,4Bが焼付層を含んで構成されている。したがって、静電容量部の内部電極へのめっき液の浸入を抑制でき、絶縁抵抗不良の発生を低減できる。

(もっと読む)

強誘電体薄膜の製造方法

【課題】(100)面に優先的に結晶配向が制御された強誘電体薄膜をシード層やバッファ層を設けることなく、簡便に得ることが可能な、強誘電体薄膜の製造方法を提供する。

【解決手段】結晶面が(111)軸方向に配向した下部電極を有する基板の下部電極上に、強誘電体薄膜形成用組成物を塗布し、加熱して結晶化させることにより下部電極上に強誘電体薄膜を製造する方法の改良であり、強誘電体薄膜が(100)面に優先的に結晶配向が制御された配向制御層により構成され、配向制御層を結晶化後の層厚を35nm〜150nmの範囲内にすることにより形成することを特徴とする。

(もっと読む)

積層電子部品

【課題】静電容量の低下を抑制し、誘電体層と電極層との密着性を向上させてクラック等を防止できる積層電子部品を提供すること。

【解決手段】誘電体層(2)とNiが主成分である電極層(3)とが積層された素子本体を有する積層電子部品であって、素子本体は、Ni酸化物を主成分とする第1相(21)と、Ni以外の金属酸化物を主成分とする第2相(22)と、を有し、素子本体を誘電体層および電極層に対して垂直な切断面において、積層方向と垂直な方向では、第1相は電極層と接し、第2相は、電極層および/または第1相と接し、第1相の少なくとも一部は、電極層と第2相とに挟まれ、積層方向と垂直な方向において、第1相が電極層と接しかつ第2相と接している長さをLnioとし、積層方向と垂直な方向における電極層の長さをLniとすると、(ΣLnio)/2Lniが0.05〜12%である。

(もっと読む)

21 - 40 / 820

[ Back to top ]