Fターム[5E346AA12]の内容

多層プリント配線板の製造 (97,916) | 多層の形状、構造 (21,562) | 層の形状、構造が特定されたもの (8,277) | 絶縁層 (3,880)

Fターム[5E346AA12]に分類される特許

81 - 100 / 3,880

配線基板及びその製造方法

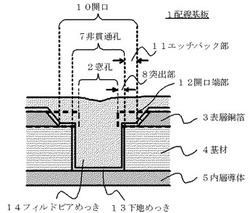

【課題】材料コストや工数を増加させずに、コンフォーマル工法で形成した非貫通孔内へのフィルドビアめっきの充填性を改善し、接続信頼性を向上させた配線基板及びその製造方法を提供する。

【解決手段】表層銅箔3の開口10から基材4を貫通して内層導体5に到る非貫通孔7と、前記非貫通孔7の周囲の基材上に前記表層銅箔の窓孔2を前記非貫通孔7より拡大して形成したエッチバック部11と、前記非貫通孔7を充填し、前記内層導体5と表層銅箔3とを電気的に接続するフィルドビア14と、を有する配線基板及びその製造方法。

(もっと読む)

配線基板及びその製造方法

【課題】貫通孔のフィルドビアめっき内へのボイドを抑制し、また表裏面の貫通孔上のフィルドビアめっき表面が平坦なことにより、工数低減と信頼性の確保を図ることが可能な配線基板及びその製造方法を提供する。

【解決手段】スルーホールめっき層を備えるIVHと内層導体とを有する内層板と、この内層板の表裏両側に積層した絶縁樹脂及び表層導体とを有する積層基板と、前記積層基板を貫通する貫通孔とを有し、前記貫通孔の断面形状が、前記積層基板の表裏両側から内部に向かって孔径が縮小したテーパ形状の部分と、前記貫通孔の内層板に対応する部分に設けられた対向する内壁が平行となる部分と、を有する配線基板及びその製造方法。

(もっと読む)

貫通コンデンサ内蔵多層基板及び貫通コンデンサ内蔵多層基板の実装構造

【課題】貫通コンデンサの接続不良の発生を低減できる貫通コンデンサ内蔵多層基板及び貫通コンデンサ内蔵多層基板の実装構造を提供する。

【解決手段】貫通コンデンサ内蔵多層基板1では、基板11の内部に貫通コンデンサ21を配置することにより、ノイズ成分を貫通コンデンサ21の接地用端子電極24から接地導体層13に流して除去することができる。また、貫通コンデンサ内蔵多層基板1では、貫通コンデンサ21の接地用端子電極24に接続される接地プレーン14cが、貫通コンデンサ21の信号用端子電極23に接続される電源プレーン14a及び電源用配線14bと同一段の導体層として配置されている。これにより、貫通コンデンサ21と電源導体層14及び接地導体層13との接続が同一段で実現されるので、貫通コンデンサ21の寸法に多少のばらつきが生じたとしても接続不良の発生を低減できる。

(もっと読む)

部品内蔵配線基板の製造方法

【課題】樹脂充填材とコア基板との密着性を改善することにより、信頼性に優れた部品内蔵配線基板を製造することが可能な部品内蔵配線基板の製造方法を提供すること。

【解決手段】コア基板準備工程ではコア基板11を準備し、収容穴部形成工程では収容穴部90をコア基板11に形成し、貫通穴部形成工程では貫通穴部14を形成する。めっき層形成工程では、収容穴部90の内壁面91に対してめっき層92を形成するとともに、貫通穴部14の内壁面に対して、空洞部を有するスルーホール導体となるめっき層71を形成する。収容工程では、部品101を収容穴部90に収容する。樹脂埋め工程では、収容穴部90の内壁面91と部品側面106との隙間、及び、空洞部に対して、樹脂充填材93を充填して埋める。

(もっと読む)

プリント回路基板及びその製造方法

【課題】積層される半導体チップの個数を増加させて高機能化を果たすとともに、薄板化の要求を満すことができるだけでなく、キャビティの内部下面を平坦化してキャビティに挿入される半導体チップを容易に整列できるようにする効果を有し、多数の半導体チップを同時に収容することができ、容易に高機能化を果たすことができるプリント回路基板及びその製造方法を提供する。

【解決手段】本発明の一実施例によるプリント回路基板100は、第1絶縁材110a及び第1絶縁材110a上に形成された第2絶縁材110bを含む絶縁層110と、絶縁層110の内層及び外層に形成された回路パターン120と、第1絶縁材110a又は第2絶縁材110bに複数個形成された半導体チップ挿入用キャビティ140と、を含む。

(もっと読む)

連結基板の製造方法

【課題】分割溝を形成する際の素子基板の変形や位置ずれを抑制できる連結基板の製造方法の提供を目的とする。

【解決手段】複数の素子基板3となる未焼成の連結基板1の第1の主面1bに0.09N/20mm以上の粘着力を有する粘着シート7aを貼り合わせた後、前記第1の主面1bとは反対側の第2の主面1aに前記複数の素子基板3を分割するための分割溝5を形成する工程と、前記第1の主面1bから前記粘着シート7aを剥離した後、前記未焼成の連結基板1を焼成する工程とを有する連結基板の製造方法。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】反りを低減可能な半導体パッケージ、及びその製造方法を提供する。

【解決手段】本半導体パッケージは、第1の半導体チップの回路形成面及び側面を封止する第1の封止絶縁層と、前記第1の封止絶縁層の前記回路形成面側の面である第1面に積層された配線層及び絶縁層と、前記絶縁層上に搭載された第2の半導体チップと、前記第2の半導体チップを封止するように前記絶縁層上に形成された第2の封止絶縁層と、を有する。

(もっと読む)

多層プリント配線板の製造方法

【課題】回路基板(例えば内層材)の位置ずれを抑制し、外側に外層材を重ねて積層成形する場合には外層材の溶着部におけるシワの発生を抑制することができる多層プリント配線板の製造方法を提供する。

【解決手段】2枚の回路基板1を絶縁層用プリプレグ2を介して溶着により仮止めした後に積層成形することによって多層プリント配線板を製造する方法に関する。前記回路基板1が、前記絶縁層用プリプレグ2に対向する面に厚み105μm以上の回路パターン4及び枠部5を設けて形成されている。前記枠部5に溶着用プリプレグ6が配置されている。

(もっと読む)

多層プリント配線板

【課題】 インダクタを有しつつも反りを抑制することを可能とする多層プリント配線板を提供する。

【解決手段】 コア基材30の内部には、第1導体パターンと第1ビア導体とによりインダクタL1、L2が形成されている。そして、コア基板30を構成する第1絶縁層30M,30A,30B,30C,30D,30E,30Fは無機繊維補強材を含んでいる。すなわち、インダクタL1、L2が形成される層には、剛性を高めるための無機繊維補強材が設けられているため、無機繊維補強材によって絶縁層の熱収縮が抑制されやすくなる。

(もっと読む)

金属ベース片面銅張板の製造方法

【課題】

金属ベース片面銅張板の多段プレスにおける作業性・生産性を大幅に改善すると共に、成形後の製品反りを抑制する製造方法を提供する。

【解決手段】

銅箔の片面に樹脂層を備えた樹脂付銅箔と金属板とを重ね合わせ熱盤間で加熱加圧成形する金属ベース片面銅張板の製造方法において、前記樹脂付銅箔の樹脂層を有する面を金属板に対向させてなる積層物を、前記樹脂付銅箔と前記金属板とが交互となるように複数組配置して加熱加圧成形する。

(もっと読む)

配線基板

【課題】

隣接する半田バンプ同士が接触して短絡してしまうことを防いで、半導体素子を正常に作動させることが可能な配線基板を提供すること。

【解決手段】

内層配線導体4aが被着された第1の絶縁層3aの表面に内層配線導体4aを挟んで第2の絶縁層3bが積層されているとともに第2の絶縁層3bの表面に半導体素子Sの電極Tが半田バンプ12を介して接続される複数の半導体素子接続パッド9が配設されて成る配線基板10であって、半導体素子接続パッド9は、半導体素子接続パッド9の直下に接続されたビア導体5aを介して内層配線導体4aに接続されている第1のパッド9aと、半導体素子接続パッド9から離間した位置で内層配線導体4aに接続されているか、あるいは内層配線導体4aから電気的に独立している第2のパッド9bとを含み、第2のパッド9bの直下に内層配線導体4aと直接的に非接続のダミービア導体5bが接続される。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】反りを低減可能な半導体パッケージ、及びその製造方法を提供する。

【解決手段】本半導体パッケージ10は、第1の半導体チップ20の回路形成面及び側面を封止する第1の封止絶縁層32と、第1の封止絶縁層32の前記回路形成面側の面である第1面に積層された配線層33、35、37及び絶縁層34、36と、第1の封止絶縁層32の前記第1面の反対面である第2面に搭載された第2の半導体チップ40と、第2の半導体チップ40を封止するように前記第2面に形成された第2の封止絶縁層49と、を有する。

(もっと読む)

支持体及びプリント配線板の製造方法

【課題】製造中のプリント配線板は剥離しにくく、製造後のプリント配線板は容易に剥離することができると共に、金属張積層板として再利用することができる支持体を提供する。

【解決手段】プリプレグ層1に第1金属箔2及び第2金属箔3を積層して形成されている。前記プリプレグ層1よりも前記第1金属箔2が小さい。前記第1金属箔2よりも前記第2金属箔3が大きい。前記第1金属箔2の周囲において前記プリプレグ層1と前記第2金属箔3とが接着されている。

(もっと読む)

配線基板

【課題】信号配線に30GHz以上の超高周波の信号を効率よく伝送させることが可能な配線基板を提供すること。

【解決手段】絶縁層1を貫通する貫通導体3Sと、絶縁層1の表面に貫通導体3Sを覆うランド部Lを有して配設された帯状の信号配線2Sと、絶縁層1の表面に信号配線2Sの周囲を所定の間隔をあけて取り囲むように配設された接地導体2Gまたは電源導体2Pと、を具備して成る配線基板であって、信号配線2Sは、ランド部Lの直径よりも広い幅で接地導体2Gまたは電源導体2Pとの間隔が一定である幅広部Wと、幅広部Wとランド部Lとの間を接続し、ランド部Lの直径よりも狭い幅で且つ信号配線2Sを伝播する信号の波長の4分の1未満の長さの幅狭部Nとを有する配線基板である。

(もっと読む)

多層セラミック基板およびその製造方法

【課題】構造欠陥の少ない多層セラミック基板およびその製造方法を得る。

【解決手段】多層基板10は、第1のセラミック層12a〜12dと第2のセラミック層14a〜14cとを交互に積層した構成を有する。第1のセラミック層12b,12c,12d上には、第1の内部電極16、第2の内部電極20、第3の内部電極22が形成される。第1の内部電極16の主面上に、第3のセラミック層18が形成される。第2の内部電極20および第3の内部電極22の主面および端部を覆うように、第3のセラミック層18が形成される。第3の内部電極22が形成された層において、第3のセラミック層18は、第1のセラミック層12dの全面を覆うように形成される。

(もっと読む)

熱硬化性樹脂組成物、並びにこれを用いたプリプレグ、積層板及び多層プリント配線板

【課題】良好な樹脂硬化性、すなわちプリプレグ積層時に、高温かつ長時間の処理を必要とせず、且つワニスやプリプレグの硬化性や保存安定性が良好であり、耐薬品性、耐熱性、接着性に優れる樹脂組成物、及びこれを用いたプリプレグ、積層板、多層プリント配線板を提供する。

【解決手段】1分子中に少なくとも2個のN−置換マレイミド基を有するマレイミド化合物(a)と、1分子中に少なくとも2個の1級アミノ基を有するアミン化合物(b)を有機溶媒中で反応させて製造される不飽和マレイミド基を有する樹脂組成物(A)、熱硬化性樹脂(B)及び、イソシアネートマスクイミダゾールやエポキシマスクイミダゾールなどの変性イミダゾール化合物(C)を含有する熱硬化性樹脂組成物を使用する。

(もっと読む)

配線基板

【課題】絶縁基板とサーマルビアとの界面におけるクラックの抑制および発光素子で発生した熱の放熱性の向上。

【解決手段】配線基板20は、外部接続用電極層120、セラミックス層130および配線層140を備える。セラミックス層130は、アルミナとホウ珪酸ガラスを材料として形成されており、熱伝導率が6W/m・K以下である。セラミックス層130は、複数の第1のサーマルビア132、および、第1のサーマルビア132より小さい直径を有する第2のサーマルビア134を配置することにより、熱伝導率の低いセラミックス層130を用いた配線基板20において、発光素子150で生じる熱の放熱性能を向上している。第1のサーマルビア132は、発光素子搭載領域150a内に格子状に配置され、第2のサーマルビア134は、隣接する全ての第1のサーマルビア132から等距離離れた位置に配置されている。

(もっと読む)

多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法

【課題】上部配線層と下部配線層とを、微細なコンタクトホールを介して接続する多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法を提供する。

【解決手段】基板10上に形成された第1の導電層20と、層間絶縁層30と、第2の導電層70とを有し、前記層間絶縁層に形成されたコンタクトホール40を介して前記第1の導電層と前記第2の導電層とが電気的に接続された構造を有する多層配線基板において、

前記層間絶縁層は、前記コンタクトホールを含まない第1の領域50と、前記コンタクトホールを含み、該第1の領域よりも表面エネルギーが高く形成された第2の領域60とを有し、

前記第1の導電層の前記コンタクトホール内の領域は、前記第2の領域よりも表面エネルギーが高く、

前記第2の導電層は、前記層間絶縁層の前記第2の領域に接触して堆積形成され、前記コンタクトホールを介して前記第1の導電層と接続されている。

(もっと読む)

配線基板及びその製造方法と半導体装置

【課題】接続バンプが狭小化された半導体チップであっても信頼性よく実装できる配線基板を提供する。

【解決手段】ガラス又はシリコンからなり、下面に開口した第1ホールH1と上面に開口した第2ホールH2とが連通してなるスルーホールTHを備えた基板層10と、第1ホールH1に形成された配線層20と、第2ホールH2に形成されて配線層20に接続された接続パッドPと、基板層10の下面に形成された絶縁層30及び他の配線層22とを含む。

(もっと読む)

電子部品モジュールの製造方法

【課題】チップ側面にスルーホールを設ける場合において、樹脂等の絶縁体が充填されたとしてもマザーシートをチップ毎に分割することができる電子部品モジュールを提供する。

【解決手段】絶縁体31を塗布するより前に、スルーホール内に固体材料52を充填しておき、絶縁体31がスルーホール内に流れ込まないようにする。固体材料52は、ワックスや蝋材等の低融点材料(絶縁体31の硬化温度よりも低い100℃未満の融点を有するもの)である。そして、絶縁体31を熱硬化させると、固体材料52が溶出または揮発し、スルーホールは空洞となる。したがって、上記V字型のブレイク用溝55を外側に、矩形状のブレイク用溝51およびV字型のブレイク用溝57を内側にして曲げることでマザー積層体を各チップにブレイクすると、スルーホールの側壁に端面電極が露出し、分割後のいずれか一方のチップの側壁に絶縁体が付着している、ということはなくなる。

(もっと読む)

81 - 100 / 3,880

[ Back to top ]