Fターム[5E346BB20]の内容

多層プリント配線板の製造 (97,916) | 配線パターンの形状、構造 (5,951) | その他 (629)

Fターム[5E346BB20]に分類される特許

1 - 20 / 629

プリント基板組立体の配線設計方法及び製造方法

配線基板の製造方法

インダクタ内蔵配線基板、及びインダクタ内蔵配線基板のインダクタンス値制御方法

配線基板

【課題】半導体集積回路素子に対して十分な電源供給を行なって半導体集積回路素子を良好に作動させることが可能な配線基板を提供すること。

【解決手段】上面側のビルドアップ配線層3における電源プレーン3Pの中に形成された接地用のビアランド3Lおよびこれに接続されたビア6は、接地用の半導体素子接続パッド7Gの各列における一部のパッドにのみ対応するにように間引かれて形成されているとともに、電源用の半導体素子接続パッド7Pの各列から電源用のスルーホール5Pへの導電路が電源プレーン3Pにおける前記間引かれた部分を通るようにして形成されているとともに、下面側のビルドアップ配線層3におけるビアランド3Lは、複数一組のビア6に対応する分が一つに繋がっている。

(もっと読む)

基板内蔵用電子部品および部品内蔵型基板

【課題】 厚みを薄くできるとともに部品集積度の向上も図ることができる基板内蔵用電子部品および部品内蔵型基板を提供する。

【解決手段】 基板内蔵用電子部品(100)は、一対の磁性体層(101、102)と、前記一対の磁性体層(101、102)の間に挟み込まれた複数の層からなる絶縁体層(103〜105)と、前記絶縁体層の少なくとも一の層内に形成された平面型コイル(110、111)と、前記平面型コイル(110、111)の周囲を一巡して同層内に形成されたシールドパターン(121、122)とを有する。

(もっと読む)

電子部品埋込み型印刷回路基板及びその製造方法

【課題】印刷回路基板内に電子部品を直接内蔵し、固定せずに脱着自在に形成することによって、基板の歩留まりに伴う部品損失を減らすことができる、電子部品埋込み型印刷回路基板及びその製造方法を提供する。

【解決手段】本発明の電子部品埋込み型印刷回路基板100は、中空構造の電子部品ケース120が設けられたベース基板110と、電子部品ケース120に挿入される電子部品150と、ベース基板110の上下面に設けられた回路パターン層131、132と、これらの回路パターン層131、132を覆う絶縁層160とを含む。

(もっと読む)

電子モジュールとその製造方法

【課題】外部振動や機械的衝撃に対して高い信頼性を確保した電子モジュールとその製造方法を提供する。

【解決手段】コア層1の上下面にビルドアップ層2b,2aを積層した多層基板20を用い、基板20の一部にコア層1を貫通した開口3に収納されたSAWフィルタ5を内蔵させ、上面のビルドアップ層2b上に形成した配線/回路パターン10aにSAWフィルタ5の端子5cおよび電子部品12a,12bを接続する。また、基板20の上面側のコア層1上に設けた配線/回路パターン6bにICチップ11a,11bを接続して搭載し、配線基板20の下面のビルドアップ層2aの表面に設置された放熱パターン9を有する。そして、基板20の上面から下面に貫通し、ICチップ11a,11bと放熱パターン9に達する熱伝達用のビアホール4を複数備え、ICチップ11a,11bを含む複数の電子部品が搭載された上面の全面を覆って補強板16を固定した。

(もっと読む)

配線基板及びその製造方法

【課題】半導体チップとの接続信頼性の優れた配線基板を提供すること。

【解決手段】オーガニック配線基板10の基板主面11側には、樹脂絶縁層21〜23と導体層24とを積層した第1ビルドアップ層31が形成されている。第1ビルドアップ層31における最表層の導体層24は、半導体チップをフリップチップ実装するための複数の接続端子部41を含む。複数の接続端子部41は、ソルダーレジスト25の開口部43を介して露出している。各接続端子部41は、半導体チップの接続領域51と、接続領域51から平面方向に延設されかつ接続領域51よりも幅が狭く形成された配線領域52とを有する。配線領域52の表面のはんだ濡れ性は接続領域51の表面のはんだ濡れ性よりも低くなっている。

(もっと読む)

積層型半導体パッケージ

【課題】高密度に相互接続した積層型半導体パッケージを提供する。

【解決手段】第1の配線基板20に第1の半導体チップ30が実装され、一方の側に第1の電極パッド23が形成された第1の半導体パッケージ10と、第2の配線基板60の他方の側に第2の電極パッド64が形成された第2の半導体パッケージ50は、半導体チップ収容孔41xと、絶縁性基材41を厚さ方向に貫通する複数の線状導体42に接合された第3の電極パッド42と、第4の電極パッド44と、を備えた接続用部材40で接合される。

(もっと読む)

回路モジュール

【課題】集積回路素子を有するICパッケージに、集積回路素子に接続されていない補助配線を設けることで、高密度配線が可能な回路モジュールを提供する。

【解決手段】集積回路素子5を有するICパッケージ2と、ICパッケージ2が実装される配線基板3とを備え、集積回路素子5がICパッケージ2の表面に形成された複数のパッドのうちの一部を介して配線基板3の複数のランド電極に接続されている回路モジュールにおいて、複数のパッドのうち集積回路素子5に接続されていない少なくとも2つのパッドが、ICパッケージ2に設けられ、かつ、集積回路素子5に接続されていない補助配線8により接続されるとともに、配線基板3に設けられた複数の配線パターン10が、集積回路素子5に接続されていない少なくとも2つのパッドと補助配線8を介して接続される。

(もっと読む)

配線基板ならびにその配線基板を備えた電子装置および電子モジュール装置

【課題】 実装信頼性が高い配線基板および電子装置ならびに電子モジュール装置を提供する。

【解決手段】 本発明の配線基板は、電子部品Eが収納される凹部1aが形成された絶縁基板3と、凹部の底面1cに形成された複数の電極2と、凹部の側壁1bの一部が傾斜しており、凹部の側壁1bの一部と凹部の底面1cとのなす角が鋭角である。

(もっと読む)

回路モジュール

【課題】共通化された電源供給ラインによって電源供給を受ける素子間において、広い周波数帯域で高いアイソレーションを確保する。

【解決手段】第1、第2電源供給ライン201,202は、接続点211で接続されている。接続点211は、バイパスコンデンサ300を介してグランドへ接続されている。第1、第2電源供給ライン201,202は互いに電磁界結合するように形成されており、この相互誘導により、相互インダクタンス−Mからなるインダクタ503が接地ライン110に接続されるのと等価な回路が実現される。接地ライン110の寄生インダクタ401のインダクタンスLpおよびバイパスコンデンサ300の寄生インダクタ301のインダクタンスLCBの合成インダクタと相互インダクタ−Mとを一致させるように、第1、第2電源供給ライン201,202を形成する。

(もっと読む)

電子素子内蔵型印刷回路基板及びその製造方法

【課題】電子素子内蔵型印刷回路基板及びその製造方法を提供する。

【解決手段】本発明に係る印刷回路基板は、キャビティが形成された第1基板と、キャビティにフェースダウン方式で内蔵された第1電子素子と、第1電子素子の上側に積層され、キャビティにフェースアップ方式で内蔵された第2電子素子と、第1基板の上下面にそれぞれ積層された第2基板と、を含むことを特徴とする。

(もっと読む)

部品内蔵基板実装体及びその製造方法並びに部品内蔵基板

【課題】小型化が可能であると共に内蔵される電子部品のレイアウトの自由度を高めつつ、内蔵された電子部品の放熱特性の向上を図る。

【解決手段】部品内蔵基板実装体100は、部品内蔵基板1と、これが実装された実装基板2とからなる。部品内蔵基板1は、第1〜第4プリント配線基材10〜40を熱圧着により一括積層した構造を備える。第2プリント配線基材20の第2樹脂基材21に形成された開口部29内には電子部品90が内蔵されている。第4プリント配線基材40の実装面2a側にはバンプ49が形成されている。電子部品90の裏面91aに接続されたサーマルビア14及びサーマル配線13を介して、各層のサーマルビア及びサーマル配線を通り、バンプ49から実装基板2に電子部品90の熱が伝わって、実装基板2にて放熱される。

(もっと読む)

プリント配線基板、基板積層体、平面コイルおよび平面トランス

【課題】同一仕様の小型のプリント配線基板を1枚または複数枚用いて基板積層体とすることによって、高いインダクタンス値を有する小型の平面コイルおよび平面トランスを提供する。

【解決手段】同一仕様の複数枚のプリント配線基板1を交互に裏返し、その第1外層面1aどうしを、或いは第2外層面1cどうしを当接させて順次重ね合わせて基板積層体Sを構築し、第1および第2選択接続部41,42間、第3および第4選択接続部43、44間に適宜接続部品である0Ωのチップ抵抗27を装着すると共に、これらのプリント配線基板Pにおける第1導体部11間を、また第6導体部16間を順に接続していくことで、簡易に所望とするターン数の平面コイルを実現することができる。

(もっと読む)

表面実装型受動素子部品、部品キャリアテープ、部品内蔵配線板

【課題】板厚み内部に位置させたとき部品端子からの導電路の配置密度を向上させること。

【解決手段】直方体状の素子部材と、素子部材の長手方向の一方向側の端部面である第1の端部面上に、および該第1の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に第1の端部面上と連なるように設けられた第1の端子電極と、素子部材の長手方向の他方向側の端部面である第2の端部面上に、および該第2の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に前記第2の端部面上と連なるように設けられた第2の端子電極と、を具備し、第1の端子電極および第2の端子電極が、いずれも、素子部材の上面上に設けられている面積の方が、素子部材の下面上に設けられている面積よりも広い。

(もっと読む)

多層基板

【課題】電子部品2を搭載する多層基板10における電子部品2と導電パターン121との間における接続信頼性の低下を抑制する。

【解決手段】熱可塑性樹脂をフィルム基材とする第2樹脂フィルム13、および熱硬化性樹脂をフィルム基材とし、片面に導電パターン121が形成された第1樹脂フィルム12を交互に積層した積層体10aと、電子部品2を搭載するベースフィルム11とを加熱プレスすることで形成される多層基板において、ベースフィルム11には、導電パターン121と電子部品2の電極端子2aとを接続するための端子接続用貫通穴111が形成され、積層体10aの積層方向から見たときに電子部品2と重合する部品搭載部位101は、端子接続用貫通穴111と重合しない非重合部位101bよりも、端子接続用貫通穴111と重合する重合部位101aに、積層方向における導電パターン121の数が多くなるように構成されている。

(もっと読む)

印刷回路基板用積層板及び印刷回路基板の製造方法

【課題】本発明は、印刷回路基板用積層板及び印刷回路基板の製造方法を提供する。

【解決手段】本発明による印刷回路基板の製造方法は、半硬化状態の絶縁体の一面に電子素子を仮接するステップと、電子素子を加圧して絶縁体に電子素子が挿入された印刷回路基板用積層板を準備するステップと、印刷回路基板用積層板の表面に電子素子と電気的に接続される回路パターンを形成するステップと、を含むことを特徴とする。

(もっと読む)

コンデンサ内蔵基板の製造方法

【課題】コンデンサ内蔵基板の製造方法において、絶縁基材上にコンデンサ素子を搭載する工程を簡略化する。

【解決手段】本発明に係るコンデンサ内蔵基板の製造方法は、貼着工程と、剥離工程と、積層工程とを有する。ここで、貼着工程では、外的な作用を与えることによりコンデンサ素子1の貼着と剥離とが可能なシート80を用いて、該シート80の表面の内、1又は複数の所定領域にコンデンサ素子1を貼着して添付することにより素子添付シート8を作製する。剥離工程では、絶縁基材20上の所定位置に、素子添付シート8を、該素子添付シート8に添付されているコンデンサ素子1を絶縁基材20に向けた姿勢で重ね合わせ、その状態で素子添付シート8に外的な作用を与えることにより、コンデンサ素子1をシート80から剥離して絶縁基材20上に搭載する。積層工程では、該絶縁基材20上に別の絶縁基材20を積層することにより絶縁基板を形成する。

(もっと読む)

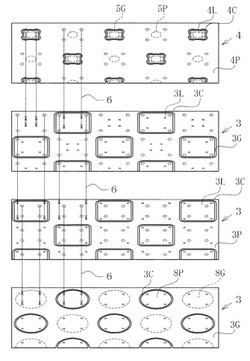

チップインダクタ内蔵配線基板

【課題】チップインダクタ内蔵配線基板において、チップインダクタの漏れ磁束に起因したノイズとしての高周波電流の配線層への影響を低減し、配線基板に実装された他の回路部品や電子部品に対する電位変動や電源供給の変動を抑制して、これら回路部品及び電子部品の動作を良好に保持する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層と、前記第1の配線層及び前記第2の配線層間に配設されてなる絶縁層と、前記絶縁層内に配設されるとともに、前記第1の配線層に実装されてなるチップインダクタとを具え、前記第2の配線層は安定電位を供給する配線層であり、前記第2の配線層の前記チップインダクタと相対向する領域において非連続の複数の開口部が形成され、前記領域が前記非連続の複数の開口部によって画定されるようにして、チップインダクタ内蔵配線基板を構成する。

(もっと読む)

1 - 20 / 629

[ Back to top ]