Fターム[5E346BB20]の内容

多層プリント配線板の製造 (97,916) | 配線パターンの形状、構造 (5,951) | その他 (629)

Fターム[5E346BB20]に分類される特許

61 - 80 / 629

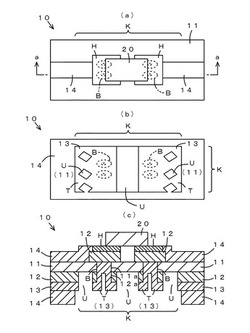

フレキシブルプリント配線板、電子機器、フレキシブルプリント配線板の製造方法

【課題】製造工程及び製造コストを増大させることなく製造することができる、放熱特性に優れたフレキシブルプリント配線板、該フレキシブルプリント配線板を備える電子機器及び前記フレキシブルプリント配線板の製造方法の提供を課題とする。

【解決手段】発熱性の電子部品20を実装するためのフレキシブルプリント配線板10であって、基材11の表裏両面に導電層12を設けてあるものにおいて、裏面側の導電層12のうち、前記電子部品20の直下を含む電子部品近傍領域Kに、凹凸パターンからなる放熱構造を設けてあると共に、前記基材11の表裏の導電層12を、前記電子部品近傍領域Kに設けたブラインドビアホールBを介して電気接続してある。

(もっと読む)

複合基板の製造方法、及び複合基板

【課題】2枚の基板をインサート物質を介して接合する複合基板の製造方法において、該インサート物質の移動を制御する複合基板の製造方法、及び該複合基板の製造方法によって得られる複合基板の提供。

【解決手段】平面をなす主面2aに機能素子8が配された第一基板2と、該第一基板2と接合させる主面3aを有する第二基板3とを用い、主面2a,3aのうち少なくとも一方の主面にインサート物質4を形成する工程Aと、主面2a,3aどうしを向かい合わせて圧接することにより、インサート物質4を介して、第一基板2と第二基板3とを接合させる工程Bと、を含む複合基板の製造方法であって、工程Aにおいてインサート物質4の表面に段差を設けること、及び工程Bにおいて前記段差の高い側から低い側に向けて、インサート物質4が移動するように圧接することを特徴とする複合基板の製造方法。

(もっと読む)

配線基板の製造方法及び半導体パッケージの製造方法

【課題】半導体チップと電気的に接続される電極パッドのピッチの、所望のピッチからのずれを小さくすることができる配線基板の製造方法を提供する。

【解決手段】半導体チップを構成する半導体基板と同等の熱膨張率を有する材料からなる支持基板11の上面に凹部を形成する工程、前記支持基板の上面に剥離層を形成する工程と、前記剥離層上に金属層を形成する工程と、前記金属層上に第1絶縁層16を形成する工程と、前記凹部に対応する位置の前記金属層が露出するように、前記第1絶縁層16を貫通する貫通穴を形成する工程と、前記金属層をシード層として、前記貫通穴内に露出した前記金属層上に第1配線層17を形成する第1配線層形成工程と、前記第1配線層17及び前記第1絶縁層16上に更に配線層及び絶縁層を積層する積層工程と、前記剥離層に所定の処理を施すことにより、前記支持基板11を除去する工程とを有する。

(もっと読む)

キャパシタおよびその製造方法、回路基板、半導体装置

【課題】ビルドアップ基板中に内蔵できるキャパシタを、エアロゾルデポジション法を使って形成する。

【解決手段】金属よりなる第1の基体上に第1のセラミック膜を形成する工程と、金属よりなる第2の基体上に第2のセラミック膜を形成する工程と、前記第1および第2のセラミック膜の一方の表面に銅よりなる第1の電極パタ―ンと第1のビアプラグパタ―ンとを、相互に離間して形成する工程と、前記第1および第2の基体を互いに押圧することにより、前記第1のセラミック膜と前記第2のセラミック膜とを、前記第1の基体と前記第2の基体とが押圧された状態で、前記第1の基体と前記第2の基体との間にパルス電圧を印加することにより、前記第1および第2のセラミック膜を、前記第1の電極パターンおよび前記第1のビアプラグパタ―ンを介して相互に接合する工程と、前記第2の基体を除去する工程と、を含む。

(もっと読む)

プリプレグ、基板および半導体装置

【課題】プリプレグの両面に異なる用途、機能、性能または特性等を付与することができ、かつ、優れた機械的強度や耐久性を有するプリプレグ、このプリプレグを備える基板、およびかかる基板を用いて製造される半導体装置を提供すること。

【解決手段】プリプレグ1は、平板状の繊維基材2と、この繊維基材2の一方の面側に位置し、第1の樹脂組成物で構成された第1の樹脂層3と、繊維基材2の他方の面側に位置し、第1の樹脂組成物と異なる組成の第2の樹脂組成物で構成された第2の樹脂層4とを備えている。第1の樹脂層3は、繊維基材2の厚さ方向の一部に第1の樹脂組成物が含浸した第1の含浸部31を有している。第2の樹脂層4は、繊維基材2の第1の樹脂組成物が含浸されていない残りの部分に第2の樹脂組成物が含浸した第2の含浸部41を有している。そして、繊維基材2内において、第1の含浸部31と第2の含浸部41が接触している。

(もっと読む)

車載用電子機器に用いる基板構造

【課題】安価かつ信頼性の高いセラミック基板において、多層構造とする際に誘電体材料から鉛を排除した材料として環境対応を図る。

【解決手段】焼結したセラミック基体2と、セラミック基体の表面に形成された導電性金属の導体ペーストからなる第一の回路配線パターン3と、第一の回路配線パターンの表層に形成された誘電体からなる絶縁層8と、絶縁層の表層に第二の回路配線パターンと回路搭載部品を搭載するランドが形成された導体パターンと抵抗体4とが形成されており、回路搭載部品を搭載するランド部分以外を保護膜5でコートし、電子回路部品7を導電性接着剤で接続したセラミック基板において、誘電体は、アルミナ粉末とガラス粉末を溶剤で混練した低温焼成セラミック基板のグリーンシート11からなることを特徴とする多層セラミック基板とする。

(もっと読む)

素子チップ、素子内蔵基板及び電子機器

【課題】素子チップの厚み方向に素子チップを押圧しても曲げ応力が加わり難い構造の素子チップを提供する。

【解決手段】回路基板13に接着剤12を介して実装される素子チップ1にかかわる。基板2上にスパイラルインダクターを構成するインダクター配線5と、インダクター配線5に沿ってインダクター配線5の一部を覆う第1樹脂膜6と、第1樹脂膜6に覆われていないインダクター配線5の他の一部と基板2との間に位置する第2樹脂膜7を有する。

(もっと読む)

保護要素

【課題】通常の回路基板担持体またはマルチレイヤー型回路基板担持体の上に被着されている金属または金属合金部に一体に形成することもでき、電子回路を被着させた回路基板担持材を含めて該電子回路が曝される200℃以上の高い動作温度でも安定に耐えることができる保護要素を提供する。

【解決手段】保護部(12)を上に形成可能な回路基板担持材(11)は、少なくとも高熱に対して安定で電気絶縁性のある材料から成り、該材料の熱膨張係数は、少なくとも、前記保護部(12)が形成されている金属または金属合金部(15)の熱膨張係数に実質的に対応して推移する。

(もっと読む)

埋め込み部品具有配線板、埋め込み部品具有配線板の製造方法

【課題】埋め込み部品具有配線板およびその製造方法において、生産効率を向上すること。

【解決手段】第1の板状絶縁層と、第1の板状絶縁層上に配置され、該第1の板状絶縁層に対向する第1の面と該第1の面とは反対の側の第2の面とを有し、該第2の面に、電気導通する部材が露出するように設けられている電気/電子部品と、第1の板状絶縁層に対して積層する位置に設けられた、電気/電子部品が存在する領域に対応して、該電気/電子部品から離間した縁の開口部を有する第2の板状絶縁層と、第1、第2の板状絶縁層の間を満たすように、かつ、第2の板状絶縁層の開口部の縁と電気/電子部品との間を満たすように、設けられた絶縁樹脂部と、第2の板状絶縁層の第1の板状絶縁層に対向する側とは反対側の面上に設けられた配線パターンと、配線パターンと電気/電子部品の第2の面の電気導通する部材とを電気的に接続する導電部材とを具備する。

(もっと読む)

部品内蔵基板の製造方法

【課題】部品内蔵基板の絶縁層に埋設されたチップ部品の外部電極を絶縁層上の電極層に接続するビア又はスルーホールのストレート性を高くする。

【解決手段】絶縁層2に埋設されたチップ部品3の外部電極4a、4bにつき、上面側の延長部分42の少なくともビア5の形成位置42aを、表面粗さの指標Rzにおいて、0<Rz<5μmを満たすように平坦化して表面の湾曲を解消し、それによって、絶縁層2に形成するビア5又はスルーホールのストレート性を高くする。

(もっと読む)

半導体装置の製造方法

【課題】擬似ウエハーの樹脂層にレーザ等でビアホールを形成することなく、簡単な工程で微細な貫通ビアを形成してチップの実装密度を高める半導体装置を提供する。

【解決手段】複数の半導体チップ20と、複数の突起を有する金属構造体とを支持基板11上の所定の箇所に配置し、前記複数の半導体チップ及び前記金属構造体25を樹脂で覆って固化し、前記固化した樹脂の一部及び前記金属構造体の一部を除去、平坦化して、前記金属構造体の前記突起25aを貫通ビアとして露出させ、前記半導体チップ及び前記貫通ビアが埋め込まれた樹脂層を前記支持基板から剥離し、前記剥離面に所定の配線パターンを形成して擬似ウエハーを完成する。

(もっと読む)

エンベデッド基板の製造方法

【課題】エンベデッド基板の製造方法を提供する。

【解決手段】

本発明によるエンベデッド基板の製造方法は、両面にパターンが形成され、上下部が貫通されるキャビティが形成されたコア基板と、上記キャビティに内蔵されるチップと、上記パターンを保護するように上記コア基板の両面にそれぞれ形成される第1及び第2絶縁体と、を含むエンベデッド基板の製造方法であって、上記コア基板を準備するステップと、上記キャビティの下側を遮蔽するように上記コア基板の下面に上記第1絶縁体をラミネイションするステップと、上記キャビティから露出する上記第1絶縁体に接着層を形成するステップと、上記接着層に上記チップを接着させて上記キャビティに上記チップを内蔵するステップと、上記コア基板の上面に上記第2絶縁体をラミネイションするステップと、を含むことを特徴とする。

(もっと読む)

セラミック基板及びその製造方法並びにイメージセンサーパッケージ及びその製造方法

【課題】本発明は、セラミック基板及びその製造方法並びにイメージセンサーパッケージ及びその製造方法を提供する。

【解決手段】本発明のセラミック基板は、上部面に第1溝が形成され、第1溝に第2溝が形成され、第2溝に貫通孔が形成されたセラミックボディーと、第1溝に形成された第1電極パッドと、セラミックボディーの上部面、下部面及びこれら両面のうちのいずれかに形成され、第1電極パッドに電気的に接続された第2電極パッドと、を含むことを特徴とする。

(もっと読む)

多層配線板およびその製造方法

【課題】層間導通部の補強効果を向上した多層配線板およびその製造方法を提供することを課題とする。

【解決手段】第1絶縁樹脂層110の一方の主面に形成された第1導体回路パターン112を備えた第1基板11と、第2絶縁樹脂層120の一方の主面に形成された第2導体回路パターン122を備えた第2基板12と、第1絶縁樹脂層110を貫通して形成された層間導通部115とを有し、第1基板11と第2基板12とを積層し、層間導通部115を介して第1導体回路パターン112と第2導体回路パターン122とを接合した多層配線板において、第1導体回路パターン112と層間導通部115との接合部の周囲に空隙を介して第1絶縁樹脂層110上に形成された第1補強パターン114と、第2導体回路パターン122と層間導通部115との接合部の周囲に空隙を介して第2絶縁樹脂層120上に形成された第2補強パターン124とを備えて構成される。

(もっと読む)

半導体パッケージの製造方法

【課題】銅コアボールをスペーサ部材として用いて上基板と下基板とを接続する際にモールド樹脂内に多量のはんだが閉じこめられない半導体パッケージの製造方法を提供することを課題とする。

【解決手段】上基板20を含みその周囲に延在部40aを有する上基板用基板材40の接合パッドに、スペーサ部材として銅コアボール18を接合するとともに、下基板12を含みその周囲に延在部50aを有する下基板用基板材50を準備する。上基板用基板材40を銅コアボール18を介して下基板用基板材50に接続する。上基板用基板材40と下基板用基板材50との間にモールド樹脂22を充填して固定する。上基板用基板材40延在部40aと下基板用基板50の延在部50aとを含む部分を除去し、半導体パッケージ10を個片化する。

(もっと読む)

部品内蔵多層配線板およびその製造方法

【課題】配線板の表面および裏面に実装される電子部品を1回の接続工程で製造可能とした部品内蔵多層配線板およびその製造方法を提供する。

【解決手段】実施形態の部品内蔵多層配線板は、第1の印刷配線板と、第1の印刷配線板と同じ大きさの第2の印刷配線板と、第1の印刷配線板の表層に実装される第1電子部品と、第1の印刷配線板と第2の印刷配線板の間に内蔵され、第1電子部品と対向する前記第1の印刷配線板の裏層に実装される第2電子部品とを有する。そして、第1の印刷配線板の第1電子部品および第2電子部品の両端に設けられるスルーホールを用いて、第1の印刷配線板と第1電子部品との接続時に、第1の印刷配線板と第2電子部品との接続を同時に行う。

(もっと読む)

電子装置及びその製造方法

【課題】多層配線が簡易な方法によって低コストで形成される電子装置の製造方法を提供する。

【解決手段】第1配線層30の上に、絶縁層22の上に金属層32aが積層された積層膜CFを形成する工程と、積層膜CFの上に開口部23aが設けられたレジスト23を形成する工程と、レジスト23の開口部23aを通して金属層32aをエッチングすることにより金属層32aに開口部32xを形成する工程と、ウェットブラスト法により、金属層32aの開口部32xを通して絶縁層22をエッチングすることにより、第1配線層30に到達するビアホールVHを形成する工程と、ビアホールVHに導電性ペースト40又ははんだからなるビア導体を形成することにより、第1配線層30と第2配線層32となる金属層32aとをビア導体で接続する工程とを含む。

(もっと読む)

多層回路基板の製造方法

【課題】放熱性が良く短絡故障のおそれがない多層回路基板の製造方法を提供する。

【解決手段】放熱板3に塗布した第1の樹脂40〔図2(a)参照〕を熱硬化させ、放熱板3に接合された第1の接着層4を形成する〔図2(b)参照〕。第1の接着層4に第2の樹脂50を塗布し〔図2(c)参照〕、その第2の樹脂50の上に、予め形成されたサブアセンブリとしての基板本体2を載せる〔図2(d)参照〕。基板本体2および放熱板3を上下から加圧しつつ加熱する。第2の樹脂50を熱硬化させて、第2の接着層5を形成するとともに、多層回路基板1を形成する〔図2(e)参照〕。

(もっと読む)

配線基板およびその実装構造体

【課題】

本発明は、電子部品との接続信頼性を向上させる要求に応える配線基板およびその実装構造体を提供するものである。

【解決手段】

本発明の一形態にかかる配線基板3は、基体11と、該基体11の上面側のみに積層された複数の絶縁層14と、基体11の下面に部分的に形成された第1接続パッド7aと、基体11と該基体11に隣接する絶縁層14との間に部分的に形成された第1導電層10aと、隣接した絶縁層14同士の間に部分的に形成された第2導電層10bと、最上層に位置する絶縁層14の上面に部分的に形成された第2接続パッド7bと、を備え、基体11および絶縁層14の平面方向の熱膨張率は、第1接続パッド7a、第1導電層10a、第2導電層10bおよび第2接続パッド7bの平面方向の熱膨張率よりも小さく、絶縁層14の平面方向の熱膨張率は、基体11の平面方向の熱膨張率よりも小さい。

(もっと読む)

半導体装置

【課題】製造工程を簡素化しつつ、スイッチング素子起因の高周波ノイズを抑制し、且つ、製造時における電子部品の信頼性を向上できる半導体装置を提供する。

【解決手段】複数の樹脂フィルムとともに電子部品を積層して積層体とし、この積層体を加圧・加熱することで、一括で樹脂フィルムを一体化しつつ電子部品を封止してなる。配線部のうち、ハーフブリッジ回路及びコンデンサの接続点とスイッチング素子とを接続する第1配線部、スイッチング素子を接続する第2配線部、接続点とコンデンサを接続する第3配線部、ゲート電極と制御ICを接続する第4配線部が、絶縁基材の厚さ方向に沿って設けられている。上記配線部を除く配線部である第5配線部は、導体パターンの表面及び該表面の裏面に層間接続ビアがそれぞれ接続され、2つの層間接続ビアが絶縁基材の厚み方向に垂直な方向において、互いに重ならないように離間して配置された配線部分を含む。

(もっと読む)

61 - 80 / 629

[ Back to top ]