Fターム[5F004DA26]の内容

半導体のドライエッチング (64,834) | 処理に用いるガス (14,486) | O2 (2,010)

Fターム[5F004DA26]に分類される特許

161 - 180 / 2,010

半導体装置の製造方法及びコンピュータ記録媒体

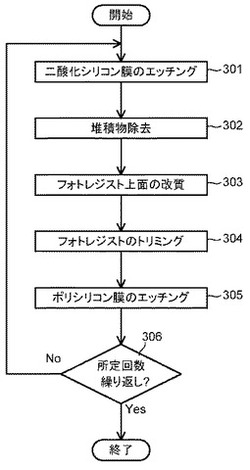

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

プラズマ処理装置

【課題】プラズマ耐性の高い酸化イットリウムを含む材料で保護膜を形成した場合でも、酸化イットリウム粒子の脱粒やクラックなどによる劣化を抑えることができるプラズマ処理装置を提供する。

【解決手段】実施形態によれば、プラズマ処理装置10はチャンバ11内に処理対象保持手段と、チャンバ11内に導入されたガスをプラズマ化するプラズマ生成手段と、を備える。チャンバ11の内壁とチャンバ11内の構成部材のプラズマ処理室61の表面には、酸化イットリウム被膜からなる保護膜50が形成される。また、保護膜50は、酸化イットリウム粒子を有し、膜厚が10μm以上200μm以下であり、膜密度が90%以上であり、単位面積20μm×20μm中に存在する粒界が確認できる酸化イットリウム粒子が面積率で0〜80%であり、粒界が確認できない酸化イットリウム粒子が面積率20〜100%である。

(もっと読む)

プラズマ発生装置およびプラズマ処理装置

【課題】簡易な構成で均一なプラズマを発生させることができるプラズマ発生装置およびプラズマ処理装置を提供する。

【解決手段】プラズマ発生装置100は、マイクロ波を発生させるマイクロ波発生部2と、一端がマイクロ波発生部2と接続された第1の導波管3と、第1の導波管3のマイクロ波発生部2と接続された側とは反対の側に接続された第2の導波管4と、を備えている。第2の導波管4は、円環状のスロット5が設けられたH面と、H面に対して垂直な方向に伸びるE面と、を有している。H面に対して垂直な方向における第1の導波管3の断面寸法Lh1と、第2の導波管4の断面寸法Lh2と、は、同じとされ、E面に対して垂直な方向における第2の導波管4の断面寸法は、第1の導波管3の断面寸法よりも大きくされている。

(もっと読む)

光発電体用半導体基板の製造方法

【課題】ゲッタリング層の除去と凹凸構造の形成とを、ドライプロセスで行う手法を提供することで、半導体基板の汚染を防ぎ、かつ低コストで光発電体用の半導体基板を提供する。

【解決手段】ゲッタリング層を有する半導体基板を用意するステップと、前記半導体基板のゲッタリング層に、エッチングガスを供給して、半導体基板の表面に凹凸形状を形成するステップとを含む、光発電体用半導体基板の製造方法を提供する。エッチングガスは、ClF3,XeF2,BrF3,BrF5およびNF3からなる群から選ばれる一以上のガスを含むことが好ましく、さらに分子中に酸素原子を含有するガスをさらに含むことが好ましい。

(もっと読む)

上部電極及びプラズマ処理装置

【課題】プラズマの均一性を高める。

【解決手段】平行平板型のプラズマ処理装置用の上部電極105であって、所望の誘電体から形成された基材105aと、前記基材105aの表面のうち、少なくとも前記プラズマ処理装置の下部電極210側の表面の一部に形成された導電体層110と、を含み、前記導電体層110は、前記下部電極210側の表面の外側が内側より密になるように疎密のパターンを有する上部電極105が提供される。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】窓部の損傷を低減させることができるプラズマ処理装置およびプラズマ処理方法を提供する。

【解決手段】プラズマ処理装置は処理容器2と、前記処理容器の内部を減圧する減圧部9と、被処理物を載置する載置部4と、内部にガスを供給するガス供給部18と、電磁波を透過させる窓部3と、前記窓部の外方に配置され、電磁場を発生させる複数の導体部21と複数の容量部とを有した負荷部20と、前記負荷部20に電力を印加する電源6bと、を備えている。前記導体部21と前記容量部とは電気的に交互に接続され、被処理物のプラズマ処理を行う場合には、前記容量部同士の間に設けられた前記導体部21において電位差の虚数成分が0(ゼロ)となる位置が生じるようにされ、前記負荷部20の第1の端子と、第2の端子と、の間における電位差の虚数成分の値が電位差の実数成分の値以下とされている。

(もっと読む)

排気ポンプ

【課題】反跳したパーティクルの処理室内への侵入を防止することができる反射装置を提供する。

【解決手段】反射装置36は、排気マニホールド16の内部に配置され、TMP18に対向するように配置された円板状の第1の反射面部材41と、該第1の反射面部材41の周縁に配置され且つTMP18の回転軸43を指向するように面角度が設定された円環状の第2の反射面部材42とから成る反射板38を備える。

(もっと読む)

半導体素子の作製方法

【課題】同一ウエハ面内で素子ごとにエッチング深さが異なる形状を簡単に、且つ精度よく加工することができる半導体素子の作製方法を提供する。

【解決手段】開口部幅の異なる領域毎に、半導体表面のエッチングが進行する第1の状態か、半導体表面にポリマーが生成される第2の状態のどちらか一方のみが発現するように前記開口部幅が設定された開口部1901を有する第一のマスク1900を半導体表面に形成すると共に、第一のマスクの周辺に第一のマスクの開口部に供給される水素プラズマ濃度を制御するための第二のマスクを形成する第1の工程と、メタンプラズマおよび水素プラズマを第一のマスク1900および第二のマスクが形成された半導体表面に照射する第2の工程を有するようにした。

(もっと読む)

炭化珪素除去装置、及び炭化珪素の除去方法

【課題】本発明は、炭化珪素に含まれる炭素成分及び珪素成分を精度よく除去可能な炭化珪素除去装置、及び炭化珪素の除去方法を提供することを課題とする。

【解決手段】炭化珪素が付着した炭化珪素形成装置の部材を収容する処理チャンバー内に、プラズマ化させたフッ素含有ガスを供給することで、炭化珪素に含まれる珪素成分を除去する第1のステップと、処理チャンバー内に、プラズマ化させた酸素含有ガスを供給することで、炭化珪素に含まれる炭素成分を除去する第2のステップと、を含み、第1のステップと、第2のステップと、を交互に行なう。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥の発生を低減できて積層欠陥の発生を抑制でき、オン電圧ドリフトを抑制できるSiCバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20は、六方晶構造の炭化珪素半導体で作製され、メサ状の半導体層31が六角柱形状で6つの側面(メサ面)31Aをすべて{0m−m0}面(m,nは整数)とした。これにより、メサ面31Aに対する〈11−20〉方向のバーガーズベクトルBV1,BV2の角度θ1,θ2(図4)が、{11−20}面の素子表面(メサ面)に対するバーガーズベクトルBV101,BV102の角度θ101,θ102(図12)に比べて小さくなると共に表面欠陥が発生するのに必要なバーガーズベクトルBV1,BV2の長さが長くなる。これにより、メサ面31Aに表面欠陥SDが入り難くなり、メサ状の半導体層31の各メサ面31Aでの表面欠陥を低減できて、積層欠陥の発生を抑制できる。

(もっと読む)

プラズマ処理装置

【課題】試料の径方向について処理の特性や加工形状の均一さを向上させたプラズマ処理装置を提供する。

【解決手段】真空容器内部に配置され内部でプラズマが形成される処理室と、この処理室内に配置された試料台と、前記処理室の上方に配置され前記プラズマを形成する電界が透過する誘電体製の円形の板部材と、この板部材の上方に配置され内部に前記電界が導入される円筒形の空洞部と、この空洞の上部の中心に連結され上下に延在した内部を前記電界が伝播する円筒形の管路と、この管路の端部に配置され前記電界を発生する発生器とを備え、前記空洞部が前記板部材を底面とする径の大きな円筒形の空洞を有した第1の円筒空洞部とこの第1の円筒空洞部の上方でこれに接続されて配置され径の小さな円筒形の空洞を有した第2の円筒空洞部と、前記第1及び第2の円筒空洞部との間でこれらを接続する段差部とを備えた。

(もっと読む)

基板処理方法及び記憶媒体

【課題】エッチングレートを低下させることなくアスペクト比の高いホール等をシリコン層に形成することができる基板処理方法を提供する。

【解決手段】ウエハ上のポリシリコン層38が臭化水素ガス、酸素ガス及び三弗化窒素ガスを含む処理ガスから生成されたプラズマ中の臭素陽イオン45aや臭素ラジカル45bでエッチングされ、次いで、該エッチング中に生成された臭化珪素系デポ物44が酸素ガス及び窒素ガスを含む処理ガスから生成されたプラズマ中の酸素ラジカル46や窒素ラジカル47で酸化処理されて酸化珪素に変成し、該酸化珪素がアルゴンガス及び三弗化窒素ガスを含む処理ガスから生成されたプラズマ中のフッ素陽イオン48aやフッ素ラジカル48bで引き続きエッチングされることによって、ホール43のエッチングレート低下が防止される。

(もっと読む)

クリーニングガス及びそれを用いたリモートプラズマクリーニング方法

【課題】CVD装置内の堆積物のリモートプラズマクリーニング法に用いられるクリーニングガスにおいて、地球温暖化係数が低く、かつ、高いエッチング速度が得られるクリーニングガス、及びそれを用いるリモートプラズマクリーニング方法を提供する。

【解決手段】CVD装置の反応チャンバー1内に堆積した、Si含有物、Ge含有物、又は金属含有物を、リモートプラズマクリーニング法により除去するクリーニングガスにおいて、該ガスはCFxOy[但し、xは2又は4であり、x=2のときy=1〜3の整数、x=4のときy=1〜4の整数を表す。]とN2が含有されている混合ガスである。

(もっと読む)

半導体素子の製造方法

【課題】被処理基板のエッチングにおける面内均一性を向上させるとともに、丸みのある滑らかな底面を有する素子分離用トレンチを形成することができる半導体素子の製造方法を提供する。

【解決手段】シリコン基板51に素子分離用トレンチ59を形成するためのパターニングが施されたハードマスク57を形成する工程と、該ハードマスクをエッチング用マスクとして、希ガス、ハロゲンガス、および酸化性ガスを含むプロセスガスを供給し、所定の深さよりも浅い深さまでシリコン基板51をエッチングする第一工程と、該第一工程の後に、希ガス、ハロゲンガス、酸化性ガス、および堆積性ガスを含むプロセスガスを、シリコン基板51の中央領域および周縁領域にそれぞれ流量を制御して供給し、所定の深さD2までシリコン基板51をエッチングして素子分離用トレンチ59を形成する第二工程と、を備える製造方法とする。

(もっと読む)

プラズマ処理装置及び方法

【課題】基材の表面近傍をごく短時間だけ均一に高温熱処理するに際して、あるいは、反応ガスによるプラズマまたはプラズマと反応ガス流を同時に基材へ照射して基材を低温プラズマ処理するに際して、基材の所望の被処理領域全体を短時間で処理することができるプラズマ処理装置及び方法を提供することを目的とする。

【解決手段】プラズマトーチユニットTにおいて、全体としてコイルをなす銅棒3が、石英ブロック4に設けられた銅棒挿入穴12内に配置され、石英ブロック4は、銅棒挿入穴12及び冷却水配管15内を流れる水によって冷却される。トーチユニットTの最下部にプラズマ噴出口8が設けられる。長尺チャンバ内部の空間7にガスを供給しつつ、銅棒3に高周波電力を供給して、長尺チャンバ内部の空間7にプラズマを発生させ、基材2に照射する。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

【課題】基板の温度が100℃以下の低温環境下において、基板上の被処理膜をエッチングする際のマスクを所定のパターンに適切に形成する。

【解決手段】ウェハWの被処理膜400上に反射防止膜401とレジストパターン402が形成される(図10(a))。レジストパターン402がトリミングされると共に、反射防止膜401がエッチングされる(図10(b))。ウェハWの温度を100℃以下に維持した状態でプラズマ処理を行い、レジストパターン402及び反射防止膜パターン403上に、100MPa以下の膜ストレスを有するシリコン窒化膜404が成膜される(図10(c))。シリコン窒化膜404がエッチングされ、レジストパターン402及び反射防止膜パターン403が除去されて、被処理膜400上にシリコン窒化膜パターン405が形成される(図10(d))。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流が小さく、好ましくはオン電流及び移動度も高く、工程が簡略化された半導体装置の作製方法を提供する。

【解決手段】チャネルエッチ型の薄膜トランジスタの作製に際して、ゲート絶縁層上に少なくとも半導体層を形成し、半導体層上に導電膜を形成し、導電膜上にエッチングマスクを形成し、基板を反応室内に搬入し、導電膜を加工してソース電極及びドレイン電極層を形成し、反応室内に半導体エッチング用のガスを導入し、反応室内で半導体エッチング用のガスでエッチングを行い、基板を反応室から搬出し、その後エッチングマスクを除去する。すなわち、導電膜の加工から半導体エッチング用のガスで行うエッチングまでを同一チャンバー内で連続して行い、半導体エッチング用のガスで行うエッチングはエッチングマスクを除去する前に行う。

(もっと読む)

プラズマ処理方法

【課題】本発明は、密部スペース幅20nm以下のパターンにおいて、疎密マイクロローディングの低減を可能とするプラズマ処理方法を提供する。

【解決手段】本発明は、シリコン基板上に密部スペース幅20nm以下のパターンのマスクを有する試料のシリコンをプラズマエッチングするプラズマ処理方法において、Cl2ガスとN2ガスの混合ガスを用い、0.1Pa以下の圧力で、デューティー比5%〜50%の時間変調された間欠的な高周波電力を前記試料に印加しながら、シリコンのエッチングを行うことを特徴とするプラズマ処理方法である。

(もっと読む)

プラズマエッチング方法

【課題】レジストマスク、シリコンを含む膜及びシリコン層が上方側からこの順番で積層された基板に対して、レジストマスクのパターンを介してプラズマエッチング処理を行ってシリコン層に凹部を形成するにあたり、前記シリコンを含む膜のサイドエッチングの発生を抑えること。

【解決手段】窒化シリコン膜2をエッチングしてシリコン層1を露出させた後、塩素を含む処理ガスのプラズマ(イオン)を用いて当該シリコン層1を僅かにエッチングして、窒化シリコン膜2の側壁に塩素とシリコンとを含む付着物13を付着させる。この付着物13はシリコン層1よりもエッチングされにくい物質であり、更に塩素イオンは異方性エッチングを行うプラズマである。

(もっと読む)

基板処理方法

【課題】スループットを飛躍的に向上させることができる基板処理方法を提供する。

【解決手段】ウエハ処理としての基板処理方法は、基板処理装置2,大気搬送装置3及びロードロック室4を備える基板処理システム1において実行され、半導体ウエハWを搬送する基板搬送ステップ(ステップS43及びS49)と、半導体ウエハWにエッチング処理を施す基板処理ステップ(ステップS44乃至S48)とを有し、基板搬送ステップ及び基板処理ステップは複数の動作からなり、基板処理方法は、各ステップを構成する複数の動作のうち少なくとも2つの動作を並行して実行する。

(もっと読む)

161 - 180 / 2,010

[ Back to top ]